Heutzutage verlangen elektronische Produkte nach Miniaturisierung und hoher Präzision, sodass die Miniaturisierung von Bauteilen zu einem wesentlichen Entwicklungstrend geworden ist. Wenn miniaturisierte Bauteile auf großflächigen Leiterplatten (PCBs) bestückt werden sollen, werden deutlich höhere Anforderungen an die Ebenheit der Leiterplatte gestellt. Folglich ist es für Leiterplattenhersteller zu einem zentralen Thema geworden, wie der Verzug von Leiterplatten verringert werden kann.

Gemäß den von IPC-600 bestätigten Fertigungsvorschriften darf die Verwerfung von Leiterplatten, die für die SMT-Bestückung bereit sind, höchstens 0,75 % betragen. Bei der Bestückung kleiner Bauteile auf Leiterplatten mit großen Flächen ist diese Vorschrift jedoch nicht ausreichend. Allgemein gilt: Um die Anforderungen der Miniaturbauteil-Bestückung auf Leiterplatten mit großen Flächen zu erfüllen, sollte die Verwerfung der Leiterplatte auf 0,5 % oder weniger reduziert werden.

Verzugsanalyse

Das Verzugproblem wird in diesem Teil des Artikels zunächst anhand einer 8-lagigen PCB mit den Abmessungen 248 mm ±0,25 x 162,2 ±0,20 analysiert. Der Verzug dieser Leiterplatte ist auf 0,5 % festgelegt, aber ihr tatsächlicher Verzug nach der ersten Produktionscharge liegt im Bereich von 2,5 % bis 3,2 %.

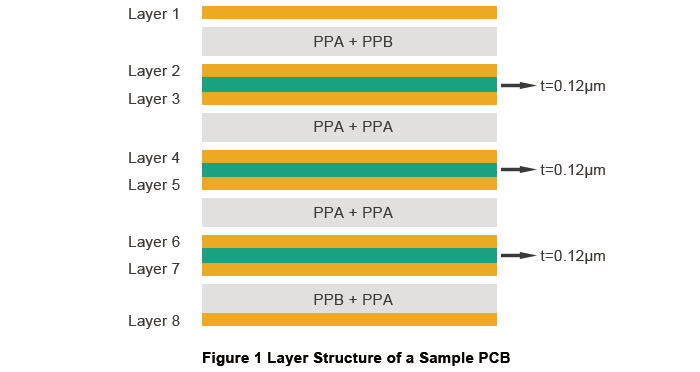

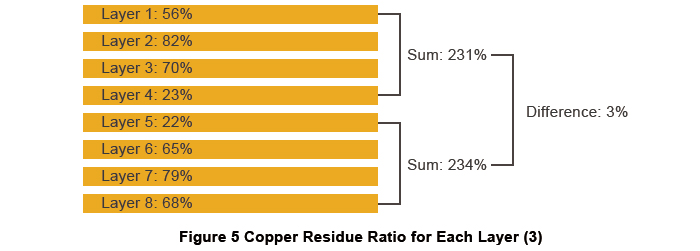

Der Lagenaufbau einer 8-lagigen Leiterplatte wird wie folgt dargestellt.

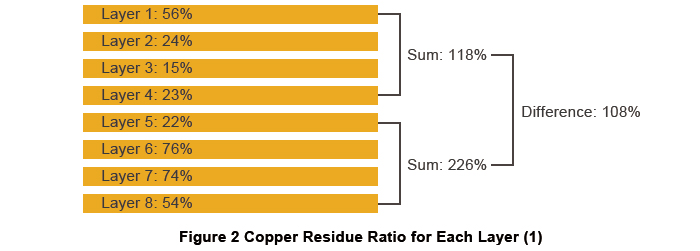

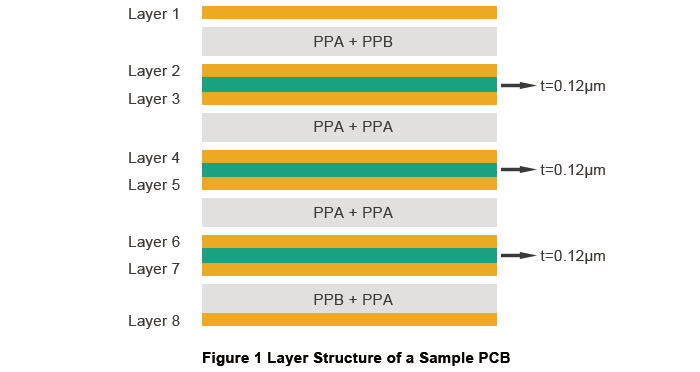

Das Kupferrückstandsverhältnis für jede Schicht ist in der folgenden Abbildung dargestellt.

Basierend auf der obigen Analyse ist das hervorstechende Merkmal dieser Musterplatine die ungleichmäßige Kupferverteilung in den einzelnen Lagen. Außerdem ist das Kupfer relativ dick. Infolgedessen kommt es zu einer Verwerfung der Platine.

Lösungen zur Vermeidung von Leiterplattenverzug

• Schema #1

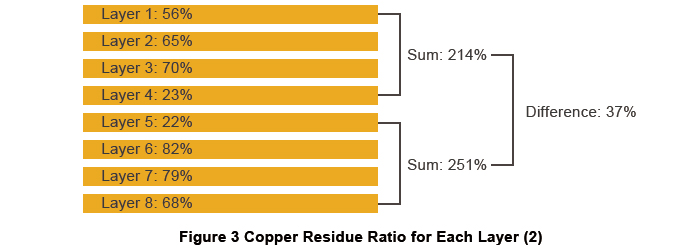

Die wichtigste Methode, um Kupferreste zwischen den Lagen der Leiterplatte auszugleichen, besteht darin, in leeren Bereichen Kupferflächen hinzuzufügen.

Um die Verformungsspannung der Leiterplatte zu verringern, ist es sinnvoll, die Panelgröße mit einer Rotations-Panelisierungsmethode zu verkleinern. Bei dieser Musterplatine sollte die Panelgröße von 610 mm x 520 mm auf 610 mm x 356 mm geändert werden. Das Panelraster des ersteren beträgt 3 x 2, während das des letzteren 2 x 2 beträgt.

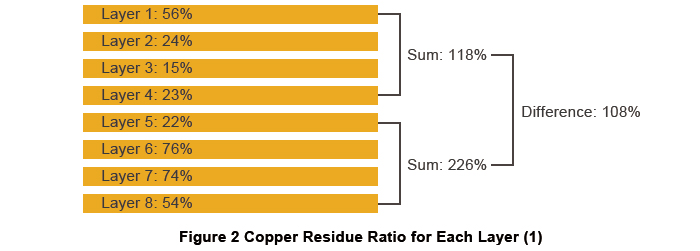

Aufgrund der oben genannten Verbesserungsmaßnahmen ist das Kupferrückstandsverhältnis in Abbildung 3 unten dargestellt. Nach diesen Modifikationen wurde die Verwerfung auf einen Bereich von 2,0 % bis 2,9 % reduziert, was eine deutliche Verbesserung darstellt, jedoch noch etwas von der Anforderung von 0,5 % entfernt ist.

•Schema Nr. 2

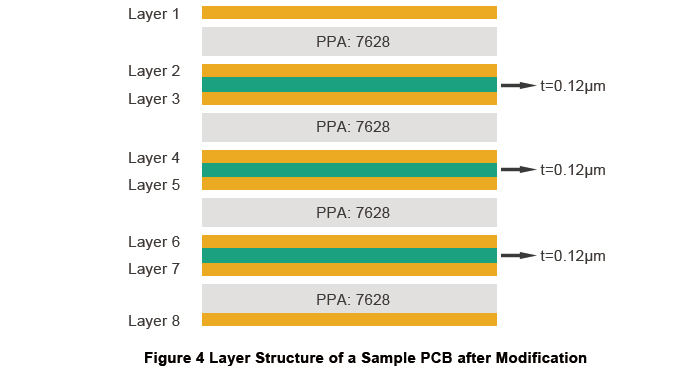

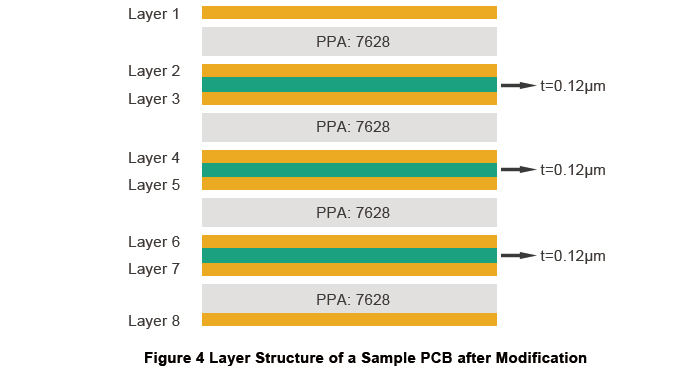

Basierend auf Schema Nr. 1 wird die Steifigkeit der Leiterplatte erhöht. Nach einer solchen Modifikation kann der Lagenaufbau der Leiterplatte durch die folgende Abbildung dargestellt werden.

Die Umsetzung dieses Konzepts führt zu einer Leiterplattenverwerfung im Bereich von 2,0 % bis 2,9 %. Offensichtlich löst dieses Konzept das Verwerfungsproblem nicht, was darauf hindeutet, dass nur ein geringer Zusammenhang zwischen Verwerfung und Platinensteifigkeit besteht. Wir müssen Konzept Nr. 1 weiter optimieren, das heißt, weitere Möglichkeiten zur Balance der Kupferreste suchen.

•Schema Nr. 3

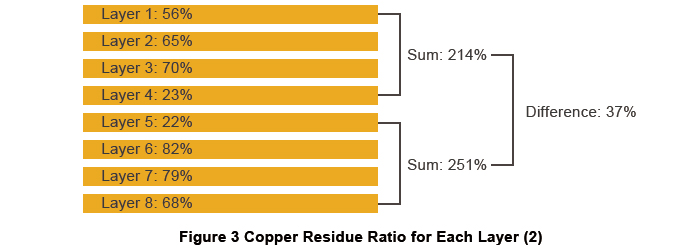

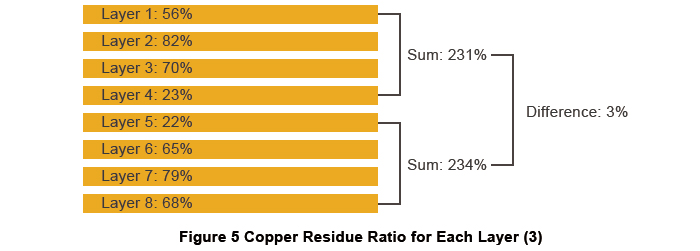

Basierend auf Schema Nr. 1 sollten Ebene 2 und Ebene 6 miteinander vertauscht werden. Das Kupferrestverhältnis für jede Lage der Leiterplatte nach Anwendung von Schema Nr. 3 ist in Abbildung 5 unten dargestellt.

Gemäß Schema Nr. 3 bleibt die Verwerfung der Leiterplatte innerhalb von 0,5 % und liegt auch nach zweimaligem Reflow-Löten weiterhin bei 0,5 %, was den Anforderungen entspricht. Darüber hinaus bestätigt eine Versuchsfertigung von 300 Stück die Zuverlässigkeit dieses Schemas. Folglich schneidet Schema Nr. 3 unter allen Schemata am besten ab.

Den obigen Experimenten zufolge ist die Verteilung in allen dielektrischen Schichten gleichmäßig, sodass die ungleichmäßige Verteilung des Kupfers die Ursache für das Auftreten von Leiterplattenverzug ist. Durch das Ausbalancieren der Kupferreste auf jeder Lage der Leiterplatte verringert sich der Plattenverzug von einem Bereich von 2,5 % bis 3,2 % auf einen Bereich innerhalb von 0,5 %. Dies zeigt, dass die Kernlösung für das Problem des Leiterplattenverzugs im Ausgleich der Kupferreste zwischen dielektrischen Schichten und Kupferschichten liegt. Dementsprechend sollte im Hinblick auf den Verzug während des Montageprozesses eine Angleichung durch Bauteilanordnung, thermische Verteilung und Montagedistribution erreicht werden, sodass der Leiterplattenverzug verringert und gleichzeitig die Produktqualität sichergestellt werden kann.

Mit dem Streben nach Miniaturisierung und Präzision ist die Reduzierung der Leiterplattenverwerfung unerlässlich geworden, insbesondere bei hochdichten Leiterplatten mit kleinen Bauteilen. Während IPC-600 eine Verwerfung von 0,75 % definiert, führen strengere Anforderungen zu einer Begrenzung auf 0,5 %. Unsere Untersuchungen an einer 8-lagigen Leiterplatte zeigten, dass eine nicht gleichmäßige Kupferverteilung eine der Hauptursachen für Verwerfung ist. Durch den Einsatz gezielter Maßnahmen, insbesondere da Schema Nr. 3 erfolgreich war, ist es uns gelungen, die Verwerfung zu minimieren, was die Bedeutung einer gleichmäßigen Kupferverteilung für maximale Stabilität der Leiterplatten unterstreicht.

Um sicherzustellen, dass Ihre Leiterplatten hohe Leistungsstandards erfüllen, ist es wichtig, sich auf die entscheidende Kupferverteilung zu konzentrieren. Solche Verbesserungen können Verzug deutlich minimieren und so die Produktqualität erhöhen. Fordern Sie noch heute ein Angebot von PCBCart an und erfahren Sie, wie diese maßgeschneiderten Ansätze in Ihrem nächsten Projekt angewendet werden können, um Zuverlässigkeit und Leistung zu steigern.

Erhalten Sie ein Sofortangebot für Leiterplattenbestückung und Leiterplattenfertigung

Hilfreiche Ressourcen

•Faktoren, die die Anzahl der Lagen und die Lagenverteilung in Leiterplatten bestimmen

•Herstellung von mehrlagigen Leiterplatten

•Die wichtigsten PCB-Designregeln, die Sie kennen müssen

•PCB-Designelemente, die die SMT-Fertigung beeinflussen