近年、電子製品には小型化と高精度が求められており、部品の小型化は不可欠な発展トレンドとなっています。小型化された部品を大面積のPCBに実装する際には、基板の平滑性に対してはるかに高い要求が課されます。そのため、PCBメーカーにとって、PCBの反りの程度をいかに低減するかが重要な課題となっています。

IPC-600 によって確認された製造規格によると、SMT 実装工程に進む準備が整った PCB の反りは最大でも 0.75% であることが求められています。ところが、大面積の回路基板に小型部品を実装する場合には、この規格は有効に機能しません。一般的に言えば、大面積の PCB 基板における小型化部品の実装要求を満たすためには、PCB の反りは 0.5% 以下に抑える必要があります。

反り解析

この記事のこの部分では、まずサイズが248mm±0.25×162.2±0.20の8層PCBサンプルを用いて反りの問題を分析する。この基板の反りは0.5%であることが要求されているが、初回ロット生産後の実際の反りは2.5%から3.2%の範囲に収まっている。

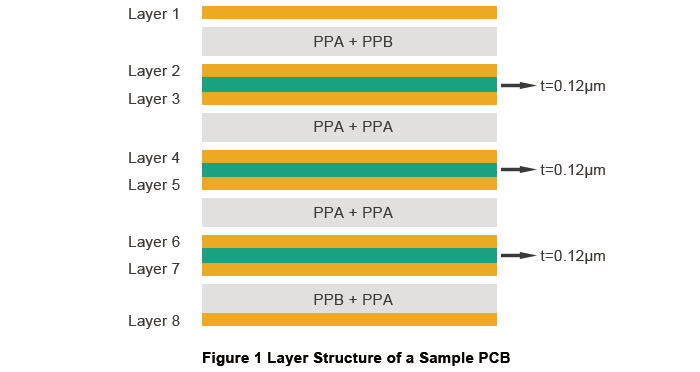

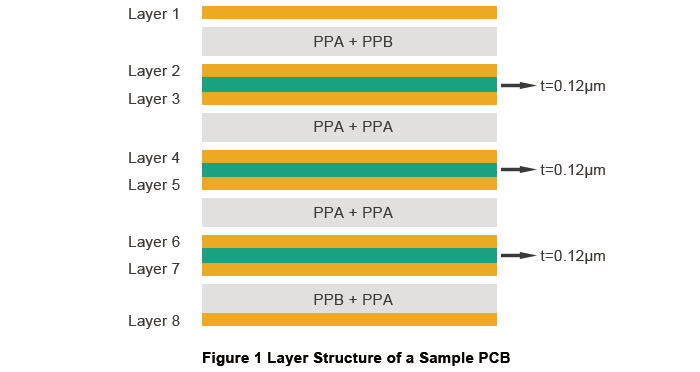

8層PCBの層構成は以下のように示されています。

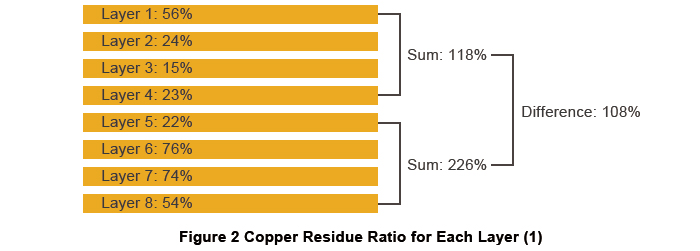

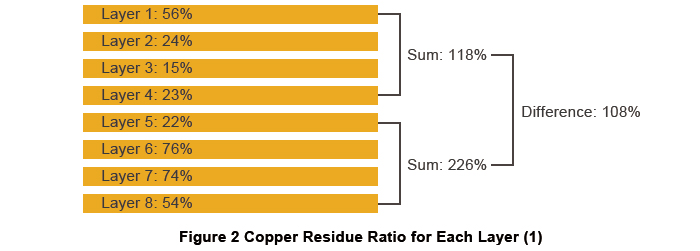

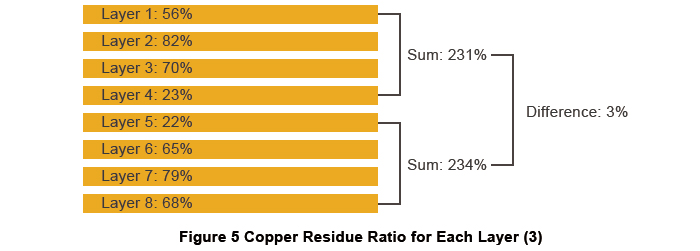

各層の銅残渣率は、次の図に示されています。

以上の分析に基づくと、このサンプル基板の突出した特徴は、各層の銅分布が不均一であることです。さらに、銅が比較的厚いため、その結果として基板反りが発生します。

PCB反りを防止するための対策

・スキーム#1

基板の層間で銅残渣をバランスさせる主な方法は、空白部分に銅ポーリングを追加することにあります。

基板の変形応力を低減するために、回転面付け方式を用いてパネルサイズを縮小することは有効な方法です。本サンプルPCBの場合、パネルサイズは610mm×520mmから610mm×356mmに変更する必要があります。前者のパネルアレイは3×2であり、後者は2×2となります。

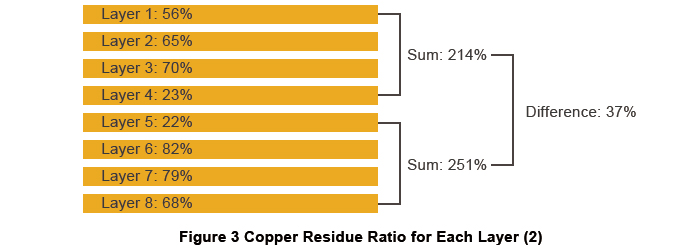

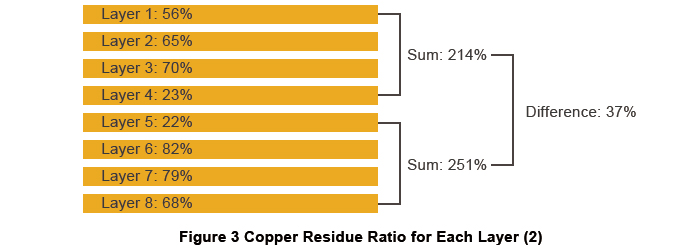

上記の改善策により、銅残渣率は以下の図3に示されている。これらの修正後、反りは2.0%から2.9%の範囲に改善され、明らかな向上が見られたものの、要求値である0.5%からはやや乖離している。

・スキーム#2

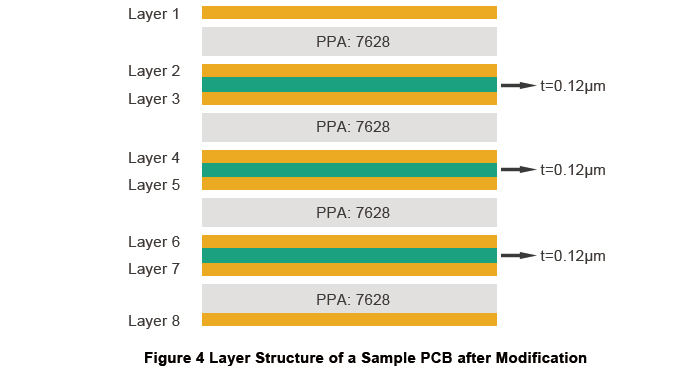

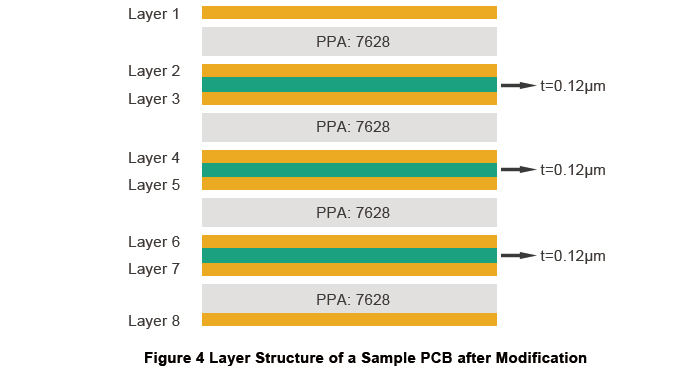

Scheme#1に基づき、基板の剛性が追加されました。この変更後、PCB基板の層構造は次の図のように示すことができます。

この方式を実装しても、PCB の反りは 2.0%~2.9%の範囲にとどまっています。明らかに、この方式は反りの問題解決には機能しておらず、反りと基板剛性との相関がほとんどないことを示しています。私たちは引き続き方案1を最適化する必要があり、すなわち銅残量のバランスを取るためのさらなる方法を探す必要があります。

・スキーム#3

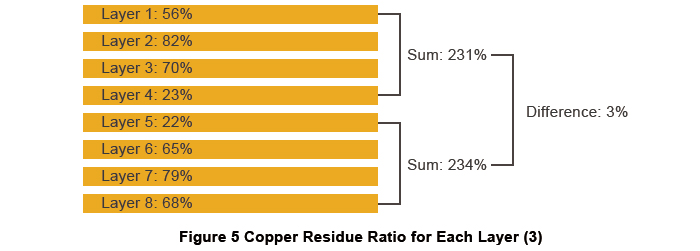

スキーム1に基づき、レイヤー2とレイヤー6は互いに入れ替える必要があります。スキーム3を適用した後のPCB各層の銅残存率を図5に示します。

スキーム3に従うと、PCBの反りは0.5%以内に収まり、2回のリフローはんだ付け後でも0.5%を維持しており、要求に適合しています。さらに、300個の試作により、このスキームの信頼性が検証されました。その結果、スキーム3はすべてのスキームの中で最も優れた性能を示しています。

上記の実験によれば、すべての誘電体層間の分布は均一であるため、PCB反りの発生を引き起こしているのは銅の不均一な分布であることが分かる。PCB基板各層の銅残量をバランスさせることで、基板反りは2.5%~3.2%の範囲から0.5%以内の範囲へと低減し、PCB反り問題の中核的な解決策は、誘電体層と銅層間の銅残量のバランスにあることが示されている。したがって、実装工程における反りに関しては、部品配置、熱分布および実装分布によって均一化を図ることで、製品品質を確保しつつ基板反りを低減することができる。

小型化と高精度化の追求に伴い、特に高密度な小型部品実装基板において、PCB反りの低減は不可欠となっています。IPC-600 では反りを 0.75% と定義していますが、より厳しい要求ではこれが 0.5% にまで引き下げられます。8層PCBに関する当社の研究では、不均一な銅分布が反りの主な原因の一つであることが示されました。集中的な対策を講じ、特に第3案(Scheme #3)が有効であったことで、反りを最小限に抑えることに成功しました。これは、基板の最大限の安定性を確保するためには、銅分布の均一性を維持することが極めて重要であることを裏付ける結果となりました。

基板の高い性能基準を確保するためには、極めて重要な要素である銅の分布に注目することが重要です。こうした最適化により反りを大幅に抑制でき、製品品質の向上につながります。PCBCart へ今すぐお見積りをご依頼いただき、これらのカスタマイズされた手法を次回のプロジェクトに適用して、信頼性と性能を向上させる方法をご確認ください。

PCBアセンブリおよびPCB製造の即時見積もりを取得

役立つリソース

•PCBにおける層数および層構成を決定する要因

•多層PCB製造

•必ず知っておくべき重要なPCB設計ルール

•SMT製造に影響を与えるPCB設計要素