Mit der Entwicklung der Gehäusetechnologien für elektronische Bauelemente hin zu Miniaturisierung, geringem Gewicht und hoher Leistung ist es zu einem Entwicklungstrend bei elektronischen Bauelementen geworden, die Funktionsdichte der Bauelemente zu erhöhen und den Abstand zwischen Eingangs- und Ausgangsanschlüssen zu verringern, was sich am deutlichsten in der automatischen Montagetechnik zeigt, die sich auszeichnet durchSMT (Surface-Mount-Technologie)Um die Oberflächenmontage von Bauteilen zu realisieren, besteht der erste Schritt darin, entsprechende Pads auf der Leiterplatte (PCB) herzustellen, sodass eine strukturierte Leiterplatte erhalten wird. Anschließend wird die Schablonendrucktechnologie angewendet, um Lotpaste auf der Oberfläche der PCB-Pads aufzubringen. Schließlich wird erhitzt, um die Lotpaste in eine Flüssigkeit zu überführen, die eine flüssige Brücke zwischen den Pins der Bauteile und dem PCB-Pad bildet. Unter dem Einfluss der Lötstoppmaske auf der Leiterplatte wird die schmelzende Lotpaste auf den entsprechenden Lötpadbereich begrenzt, um Brückenbildung zwischen den Lötstellen zu verhindern, sodass die automatische Bestückung des Chips auf der Leiterplatte realisiert wird. Je nach Gehäusetyp werden hauptsächlich runde und rechteckige Lötpads ausgewählt, das heißt,BGA (Ball Grid Array)und QFN (Quad Flat No-Lead)-Gehäuse. Wenn Sie mehr über BGA erfahren möchten, genügen nur VIER Schritte.

QFN-Wiki

Im Vergleich zu anderen Bauteilen mit unterschiedlichen Gehäusetypen ist das QFN-Gehäuse dafür ausgelegt, direkt auf einer PCB- oder FPC-Leiterplatte verlötet zu werden. Dank seiner freiliegenden Metallpads an der Unterseite bietet es eine bessere Wärmeableitung. Darüber hinaus zeichnet sich das QFN-Gehäuse durch hervorragende elektrische Eigenschaften aus, da seine Pins kürzer sind als die von Bauteilen mit verlängertem Gehäuse. Daher ist es von großer Bedeutung, QFN-Pads auf der Leiterplatte zu entwerfen, damit die hohe Zuverlässigkeit und Leistungsfähigkeit der Leiterplatte aufrechterhalten und sichergestellt werden kann.

Benetzungswinkel

Da die Größe der QFN-Pins und der Abstand zwischen den Pins relativ gering sind, kann es aufgrund der genauen Menge der aufgetragenen Lötpaste zu Lötbrücken oder Pseudolötungen kommen. Daher ist ein angemessenes Design der Padgröße der Leiterplatte auf Grundlage der Dicke der Schablone erforderlich (h0) ist für die Erfolgsquote des Lötens äußerst hilfreich. Angenommen, der Benetzungswinkel von Lötzinn auf der Lötfläche (θa) beträgt 30° und der Benetzungswinkel von Lötzinn auf der Lötstoppmaske (θr) beträgt 160°. Wenn die Rauheit der Pad-Oberfläche vernachlässigt wird, kann der Benetzungswinkel näherungsweise als Vorwärts- oder Rückzugswinkel der Dreiphasen-Kontaktlinie betrachtet werden. Entsprechend dem praktischen Lötverfahren von QFN-Bauteilen ermöglicht eine angemessene Steuerung der Temperaturkurven des Reflow-Lötens unter idealen Bedingungen, bei denen das Lot vollständig geschmolzen ist und die Pad-Oberfläche benetzt wird, sowohl die Sicherstellung der Löteffizienz als auch das Erreichen eines automatischen Montage-Lötgleichgewichts der Bauteile. Wenn das Pad vernünftig ausgelegt ist, erfüllt der Idealzustand der Lötstellen nicht nur die Anforderungen an die elektrische Leistung der Leiterplatte und die mechanische Verbindung, sondern vermeidet auch Lötfehler wie Brückenbildung und Pseudolötungen. In diesem Sinne muss der Zustand der Lötstellen die folgenden Formeln erfüllen:

a. Wenn Lötstellen innerhalb des QFN vollständig auf der PCB-Pad verteilt sind,θa≤θj(Zu)≤θr,θj(0)=30°x3(0)=x4(0)=Dx4

b. Wenn Zinn außerhalb des QFN im Seitenpad wächst,

(1)θj(Zu)=θs3+90°θ4(0)=30°θ3(0)=30°

(2)x3(0)=x4(0)=Dx4(0),x3(Zu)=0.

Pad-Design

In dieser Formel,θs3ist gleichθawobei beide den Benetzungswinkel von Lötzinn auf der Seitenkontaktfläche darstellen.

In vertikaler Richtung lautet die Gleichung des statischen Gleichgewichts der überbrückenden Flüssigkeit:

PdLy(x3(0)-x4(0)+Lx)+Wz-[T(x3(0)-x4(0)+Lx)(sinθ2(0)+sinθ1(0))+TLy(Sündeθ3(0)+sinθ4(0))]-ρgV0=0

Die Druckintensität am Boden der Lötverbindungen (Pd) ist:Pd=T(x3(0)-x4(0)+Lx)(sinθ2(0)+sinθ1(0))+Zielgruppey(Sündeθ3(0)+sinθ4(0))+ρgV0-Wz]/[Ly(x3(0)-x4(0)+Lx)]

In diesen Formeln,ρbezieht sich auf die Flüssigkeitsdichte von Lötzinn; T bezieht sich auf die Oberflächenspannung der Lötstellenflüssigkeit;x3(0) undx4(0) bezieht sich auf das Gleiten der beiden Enden flüssiger Lötverbindungen auf der flüssigen Lötfläche des unteren Lötpads;θ1(0) undθ2(0) beziehen sich auf die Kontaktwinkel auf beiden Seiten, die durch die Flüssig-Gas-Grenzfläche auf beiden Seiten der Lötstellen und der Oberfläche der unteren Lötpads gebildet werden, währendθ3(0) undθ4(0) beziehen sich auf die Kontaktwinkel an beiden Enden, die durch die Flüssig-Gas-Grenzfläche auf beiden Seiten gebildet werden;V0bezieht sich auf das Volumen der Lötverbindung;Wzbezieht sich auf die aufgebrachte Kraft des Pads am Ende des Chips und der Lötverbindung in vertikaler Richtung.

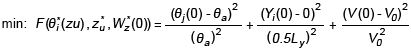

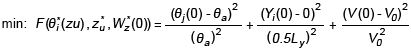

Unter der Einschränkung der Formeln (1) und (2) können Rahmenkurven von Lötstellen die Randbedingungen am oberen Ende der Lötstellen den Anfangsbedingungen äquivalent machen, basierend auf der effektiven Methode der Lösungen für Anfangswerte. Da die Lösung für Anfangswerte nicht in der Lage ist, die Anforderung zu erfüllen, dasszist gleich 0, wird es in ein äquivalentes Problem in Bezug auf die Minimierung der Zielfunktion umgewandelt, das in Gleichung (3) dargestellt ist.

Diese minimierte Zielfunktion kann angewendet werden, um die ideale Auslegungsgröße des Pads zu bestimmenDx4.

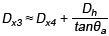

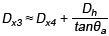

Außerdem müssen die geometrischen Merkmale des Zinnumschlingungswinkels des Leiterplattenpads berücksichtigt werden. In diesem Zusammenhang sollte die Vergrößerung des Pads ungefähr der folgenden Gleichung entsprechen:

In dieser Gleichung,Dhbezieht sich auf die Dicke des freiliegenden seitlichen Pads außerhalb des Chips. Durch die Optimierung impliziter Variablen wird die erwartete Fehlertoleranzanforderung durch die Zielfunktion erfüllt und die Konstruktionsgröße der Pads innen und außen (Dx4&Dx3) kann berechnet werden, wobei der Bedarf an Seitenwert am unteren Ende gedeckt ist.

Diese Methode stellt sicher, dass ein für QFN geeignetes Pad so ausgelegt werden kann, dass die hohe elektrische Leistung sowohl dieser Komponente als auch der Leiterplatte erreicht wird. Anschließend, mit professioneller und qualifizierterMontagefähigkeitist PCBCart in der Lage, Ihr ideales Design in die Realität umzusetzen.