PCB erfolgreich in Ihren Warenkorb gelegt

Differenzielle isometrische Verarbeitung und Simulationsverifikation von Hochgeschwindigkeits‑PCB‑Designs

Signale, die über differentielle Signalleitungen übertragen werden, enthalten eine differentielle Modenkomponente und eine Gleichtaktkomponente der Signale.

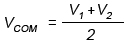

Die Höhe der differentiellen Signale bezieht sich auf die Differenz zwischen zwei Signalen gemäß der folgenden FormelVDiff=V1-V2. Die Höhe der Gleichtaktsignale entspricht der Hälfte der Summe zweier Signale gemäß folgender Formel Daher führt die Spannungsänderung einer einzelnen Leitung zwangsläufig zu einem gleichzeitigen Einfluss auf Differenzsignale und Gleichtaktsignale. Anschließend wird eine Grafiksoftware verwendet, um Funktionsdiagramme zu erstellen und den Einfluss auf Differenzsignale und Gleichtaktsignale jeweils zu untersuchen. Zur Vereinfachung der Untersuchung können die Signale analysiert werden, indem sie als trapezförmige Wellenform mit derselben Anstiegs- und Abfallzeit simuliert werden.

Daher führt die Spannungsänderung einer einzelnen Leitung zwangsläufig zu einem gleichzeitigen Einfluss auf Differenzsignale und Gleichtaktsignale. Anschließend wird eine Grafiksoftware verwendet, um Funktionsdiagramme zu erstellen und den Einfluss auf Differenzsignale und Gleichtaktsignale jeweils zu untersuchen. Zur Vereinfachung der Untersuchung können die Signale analysiert werden, indem sie als trapezförmige Wellenform mit derselben Anstiegs- und Abfallzeit simuliert werden.

• Einfluss auf differentielle Signale

Das positive Phasenanschlusssignal, das negative Phasenanschlusssignal und das Differenzsignal der differentiellen Leitungspaare sind in Abbildung 1 unten dargestellt, wobei die durchgezogene Linie die Differenzsignalwelle darstellt.

Wenn eine Phasenplatzierung vom positiven Phasenanschluss zum negativen Phasenanschluss erfolgt, wird es am steigenden oder fallenden Flankenrand eine Änderung der Differenz zwischen dem Signal des positiven Phasenanschlusses und dem Signal des negativen Phasenanschlusses geben, und diese Änderung wird sich mit der Änderung der Phase verändern.Trwird verwendet, um für die kürzere Zeit zwischen Anstiegs- und Abfallzeit zu stehen. Es kann angegeben werden, dass, wenn die Phasenlage weniger als Punkt zwei vonTrist die Signalverzerrung relativ gering, und die Vergrößerung der Phasenplatzierung führt zu einer starken Verzerrung der differentiellen Wellenform. Wenn die Phasenplatzierung überschreitetTrIm nichtmonotonen Bereich wird dies auf der Wellenform auftreten. Hier ist der nichtmonotone Bereich eine gerade Linie. Bei praktischen Signalen können jedoch aufgrund von Reflexionen im nichtmonotonen Bereich starke Auf- und Abbewegungen auftreten, wodurch sich Störimpulse bilden, die zu Fehltriggerungen führen und vermieden werden sollten. Außerdem wird die obere Flanke der differentiellen Wellenform mit zunehmender Phasenverschiebung langsamer, was zu einer unzureichenden Einschwingzeit für das Datensignal und zu einer unzureichenden Haltezeit für das Taktsignal führen kann.

• Einfluss auf das Gleichtaktsignal

Die Phasenplatzierung eines einzelnen Endsignals hat keinen Einfluss auf die differentielle Wellenform, verändert jedoch die Wellenform der Gleichtaktsignale. Wenn die Phasenplatzierung am positiven Endsignal erfolgt, tritt eine Wellenänderung bei den Gleichtaktsignalen auf. Es kann darauf hingewiesen werden, dass der Schwankungsbereich mit dem Ausmaß der Phasenplatzierung zusammenhängt. Wenn das Ausmaß der Phasenplatzierung jeweils 0,05 beträgtTr, 0,1Tr, 0,2Trund 0,5Tr, beträgt der Schwankungsbereich des Gleichtaktanteils jeweils 5 %, 10 %, 20 % und 50 % des ursprünglichen Schwankungsbereichs. Wenn die Phase zunimmt bisTroder mehr, wird die Schwankung auf ungefähr 100 % ansteigen, was den höchsten Schwankungsbereich darstellt. Die Änderung des Gleichtaktsignals kann zu EMI-Problemen führen, und da das Gleichtaktsignal unter vielen Bedingungen nicht am Endgerät empfangen wird, bildet sich am Empfangsterminal eine Reflexion, die zu Signalringing führt. Daher sollte der Schwankungsbereich des Gleichtaktsignals so weit wie möglich verringert werden.

Zusammenfassend lässt sich sagen, dass eine zu große relative Verzögerung zwischen differentiellen Paaren zu Fehltriggern von Signalen, Signalreflexionen, EMI und Problemen bei der Zeitsequenzierung führen kann. Der Einflussgrad der relativen Verzögerung des Signals hängt jedoch vom mit dem Signal kompatiblen Skalierungsfaktor ab.TrWenn der Skalierungsfaktor 0,05 beträgt, kann die Verzerrung von Differenzsignalen nahezu vernachlässigt werden. Für Gleichtaktsignale jedoch kann bei einem Skalierungsfaktor von 0,05 die Spannungsfluktuation der Gleichtaktsignale auf etwa 5 % begrenzt werden. Selbst im Fall einer vollständigen Reflexion beträgt die auf den Signalleitungen überlagerte Reflexionsspannung dann nur 10 % der ursprünglichen Fluktuation, was in der Regel ein akzeptabler Wert ist. Daher, im Prozess derHochgeschwindigkeits-PCB-DesignIn den Routing-Regelvorschriften kann die relative Verzögerung der differentiellen Signalleitung auf 0,05 eingestellt werden.Trdie in der Lage ist, die Anforderungen an die Signalintegrität zu erfüllen.

Bestimmung der relativen Verzögerungskategorie

Basierend auf der obigen Analyse liegt der Schlüssel zur Bestimmung der differentiellen isometrischen Kategorie, das heißt der Bestimmung der relativen Verzögerung differentieller Paare, in der Bestimmung vonTrBezieht sich auf den kleinsten Wert zwischen oberer und unterer Zeit von Differenzsignalen. Der Ausgang der Anstiegs- und Abfallzeit ist tatsächlich das Ergebnis der Kombination von Impedanz und Kapazität. Daher ist die Anstiegs-/Abfallzeit ohne Last tatsächlich die inhärente Anstiegs-/Abfallzeit.

Die folgenden drei Methoden können angewendet werden, um den Wert vonTrZielsprache: de

Zu übersetzender Text ist wie folgt (bitte nur den Inhalt selbst übersetzen, keine Erklärungen hinzufügen):

•Anstiegs-/Abfallzeit kann direkt den Komponentenhandbüchern entnommen werden. In den meisten Fällen wird dieser Parameter jedoch nicht angegeben.

•Wert vonTrkann aus Ramp-Schlüsselwörtern des Komponenten-IBIS-Modells (Input/Output Buffer Informational Specification) gewonnen werden. Anstiegs-/Abfallzeitparameter unter den Ramp-Schlüsselwörtern werden im Allgemeinen am Ausgangsport gemessen, der mit einem Widerstand von 50 Ω verbunden ist, was üblicherweise 20 % bis 80 % der Endspannung entspricht. Da die Parameter ohne Berücksichtigung des Einflusses des Gehäuses gewonnen werden, ist es für uns streng, die Anstiegs-/Abfallzeit als den Wert vonTr.

•Der Wert vonTrkann entsprechend der minimalen oder maximalen Taktfrequenz der Ausgangssignale abgeschätzt werden. Da die verteilte steigende Flanke in den meisten Hochgeschwindigkeits-Digitalsystemen ungefähr 10 % der Taktfrequenz beträgt, ist der Wert vonTrkann mit der minimalen Taktperiode Tclk geschätzt werden, die auf der Grundlage der folgenden Formel angegeben ist:Tr=Tclkx 10 %.

Der anhand der Taktperiode ermittelte Schätzwert ist in der Regel streng, da parasitäre Gehäuseparameter oder die Belastung durch Bauteile die inhärente Anstiegs- und Abfallzeit in Transistoren stark verlangsamen.

In der praktischen Arbeit geben Schaltungsentwickler in den meisten Situationen keine Informationen überTran Leiterplatten-Layoutingenieure, die nur einige vage Anforderungen in Bezug auf differentielle isometrische Kontrolle erhalten. Die dritte Methode bietet den Leiterplatten-Layoutingenieuren zweifellos ein einfaches Schema, sofern die höchste Taktfrequenz auf der Signalleitung ermittelt wird. Die höchste Taktfrequenz gilt als der zuverlässigste Designparameter für Schaltungsentwickler und wird den Leiterplatten-Layoutingenieuren in der Regel zu Beginn des Leiterplattendesigns zur Verfügung gestellt.

Die dritte Methode führt in der Regel zu einer Liste von Referenzwerten innerhalb der Kategorie der relativen Verzögerungssteuerung zwischen differentiellen Paaren, wie in der folgenden Tabelle dargestellt.

| Taktfrequenz/ns | Taktfrequenz/MHz | Relative-Verzögerungskategorie/ps | Übertragungsleitungslänge/mil |

| 3,75 | 266 | 18,8 | 105 |

| 3 | 333 | 15 | 84 |

| 2,5 | 400 | 12,5 | 70 |

| 1,87 | 533 | 9,4 | 52 |

| 1,5 | 667 | 7,5 | 42 |

| 1,25 | 800 | 6.3 | 35 |

Simulationsverifizierung

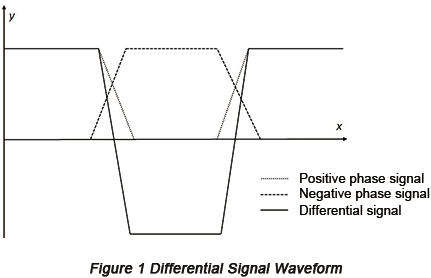

Nehmen wir das DQS- (Data Strobe) Differenzsignal zwischen TSM320 und MT41J256M16 als Beispiel, CadenceSimulationssoftwarewird angewendet, um ein DOS-Signal an den DRR3-Speicher zu übertragen, den Speicherkontrollchip zu simulieren, seinen Einfluss auf die Aufbau- und Haltezeit des Datensignals zu analysieren und die obige Analyse zu verifizieren. Die Simulationsschaltung ist in Abbildung 2 unten dargestellt.

Basierend auf Abbildung 2 beträgt die Referenzspannung der Ausgangspins 1,5 V; der Speicherkontrollchip ist im ODT-Modus (On-Die Termination) direkt über eine 800-mil-Übertragungsleitung mit dem Speicherchip verbunden; die differentielle Impedanz beträgt 100 Ω und die Simulations-Taktfrequenz 800 MHz. Eine Übertragungsleitung von 50 Ω ist in Reihe mit dem positiven DQS-Phasenanschluss verbunden, um das Abweichungsphänomen differentieller Paare zu simulieren. Im Fall isometrischer Differenzleitungen beträgt die Länge der einseitigen 50-Ω-Übertragungsleitung 0 mil.

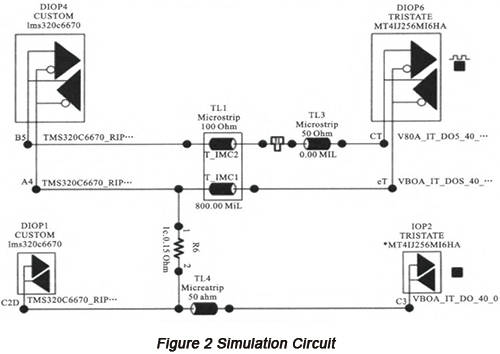

Die Simulation wird an der differentiellen isometrischen Schaltung durchgeführt. Abbildung 3 zeigt das Ausgangssignal am positiven Phasenanschluss der differentiellen Signale. Durch Messung beträgt die Anstiegszeit etwa 216 ps, während die Abfallzeit 219 ps beträgt, sodass die minimale Anstiegs-/AbfallzeitTrsollte 216 ps sein.

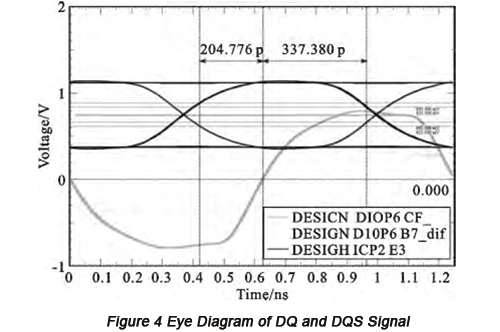

Abbildung 4 ist ein Augendiagramm des Datensignals DQ und des Gatingsignals DQS aus einer Simulation mit einer Einschwingzeit von 205 ps und einer Haltezeit von 337 ps. Entsprechend der Flankenwechselrate der DQS- und DQ-Signale in der Simulation und basierend auf dem Datenhandbuch wird für die Datensignale am Empfangsterminal eine minimale Einschwingzeit von 85 ps und eine minimale Haltezeit von 95 ps gefordert. Daher beträgt die Übererfüllung der minimalen Einschwingzeit 120 ps und der Haltezeit 242 ps.

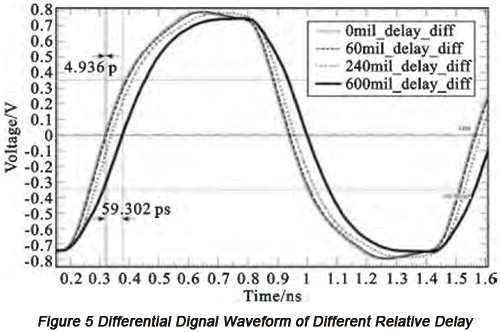

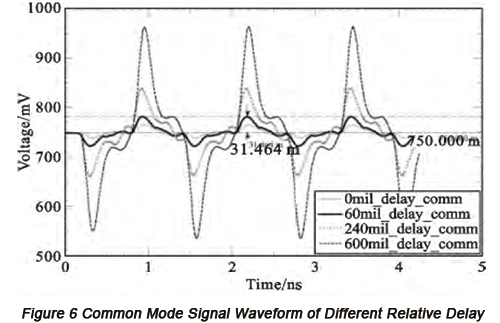

Die Situation des Vorhandenseins von 0,05TrPhasenplatzierung, 0,2TrPhasenplatzierung und 0,5TrDie Phasenplatzierung am positiven Phasenanschluss muss berücksichtigt werden. Die Schaltung kann mit einer einpoligen Übertragungsleitung simuliert werden, deren Länge entsprechend auf 60 mil, 240 mil und 600 mil eingestellt ist. Die differentiellen Signalwellenformen und die Gleichtakt-Signalwellenformen aus vierfacher Simulation sind in Abbildung 5 und 6 dargestellt.

Basierend auf Abbildung 5 ist die Verzerrung minimal, wenn die relativen Verzögerungen 0,05 betragenTrund 0,2Trstattfinden. Besonders wenn die relative Verzögerung 0,05 beträgtTr, nur eine Platzierung von etwa 5 ps vom differentiellen Signal zur differentiellen Signalform ohne relative Verzögerung, sodass die Übermessung der Datensignal-Setup-Zeit um etwa 5 ps erhöht wird, während die Übermessungszeit der Haltezeit um 5 ps verringert wird. Obwohl die Übermessungszeit der Haltezeit verringert wird, ist diese Platzierungsmenge im Vergleich zur Haltezeit von 242 ps sehr gering. Zeitsequenzierung kann vermieden werden. Für die Situation, wenn die relative Verzögerung 0,5 beträgtTrDie Platzierung der DQS-Signalkurve hat etwa 60 ps erreicht. Obwohl diese Platzierung noch in die Kategorie der Übermessung fällt, sollte ihr ausreichende Aufmerksamkeit geschenkt werden.

Basierend auf Abbildung 6 führt die Zunahme der Phasenplatzierung zu offensichtlichen periodischen Schwankungen der Wellen und zur allmählichen Vergrößerung der Reichweite. Wenn die relative Verzögerung jeweils 0,05 beträgtTr, 0,2Trund 0,5Tr, der gemessene Spitzenwert des Gleichtaktsignals beträgt jeweils 61 mV, 176 mV und 430 mV, wobei der höchste Wert dem Siebenfachen des niedrigsten entspricht. Der größte Schwankungsbereich beträgt jeweils 4,3 %, 12 % und 29 %.

Zusammenfassend lässt sich sagen, dass das Simulationsergebnis mit dem durch die Analyse des mathematischen Funktionsdiagramms erhaltenen Ergebnis übereinstimmt. Wenn die relative Verzögerung zwischen differentiellen Paaren weniger als 0,05 beträgtTr, der Einfluss auf die Signale ist ziemlich gering.

Die minimale Taktperiode des Ausgangssignals am Ausgangsanschluss wird zur Abschätzung der Kategorie der relativen Verzögerungssteuerung herangezogen. Basierend auf dem Komponentenhandbuch beträgt die minimale Taktperiode der Komponenten 1,25 ns bei einer Taktfrequenz von 800 MHz. Gemäß Tabelle 1 sollte die relative Verzögerung bei einer Übertragungsleitungslänge von 35 mil innerhalb von 6,3 ps gehalten werden. Offensichtlich ist dieser Wert deutlich kleiner als die Steuerkategorie der relativen Verzögerung von 0,05.Trdurch Simulation. Daher ist die geschätzte relative Verzögerungssteuerungskategorie relativ konservativ und genauer als das Simulationsergebnis.

Hilfreiche Ressourcen

•Forschung zum Hochgeschwindigkeits‑PCB‑Design in eingebetteten Anwendungssystemen

•So entwerfen Sie Bild-Ebenen für Hochgeschwindigkeits‑Leiterplatten

•Herausforderungen der Hochgeschwindigkeits‑PCB‑Entwicklung in Bezug auf Signalintegrität und deren Lösungen

•Simulation von Leiterplatten mit OrCAD PSpice

•Umfassender Leiterplatten-Fertigungsservice von PCBCart – zahlreiche wertsteigernde Optionen

•Fortschrittlicher Leiterplattenbestückungsservice von PCBCart – ab 1 Stück