PCB ajouté avec succès à votre panier

Traitement isométrique différentiel et vérification par simulation de la conception de PCB haute vitesse

Les signaux transmis dans des lignes de signal différentielles contiennent une composante en mode différentiel et une composante en mode commun des signaux.

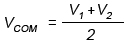

La quantité de signaux différentiels fait référence à la différence entre deux signaux selon la formuleVdiff=V1-V2. La quantité de signaux en mode commun correspond à la moitié de la somme de deux signaux selon la formule Par conséquent, la variation de tension d’une seule ligne entraîne inévitablement une influence simultanée sur les signaux en mode différentiel et les signaux en mode commun. Ensuite, un logiciel de tracé est utilisé pour dessiner le diagramme de la fonction mathématique afin d’étudier séparément l’influence sur les signaux en mode différentiel et les signaux en mode commun. Pour faciliter la recherche, les signaux peuvent être analysés en les simulant sous forme d’onde trapézoïdale avec le même temps de montée et de descente.

Par conséquent, la variation de tension d’une seule ligne entraîne inévitablement une influence simultanée sur les signaux en mode différentiel et les signaux en mode commun. Ensuite, un logiciel de tracé est utilisé pour dessiner le diagramme de la fonction mathématique afin d’étudier séparément l’influence sur les signaux en mode différentiel et les signaux en mode commun. Pour faciliter la recherche, les signaux peuvent être analysés en les simulant sous forme d’onde trapézoïdale avec le même temps de montée et de descente.

• Influence sur les signaux différentiels

Le signal de la borne de phase positive, le signal de la borne de phase négative et le signal différentiel des paires de lignes différentielles sont présentés dans la Figure 1 ci-dessous, dans laquelle la ligne pleine représente l’onde du signal différentiel.

Si un placement de phase a lieu du terminal de phase positif vers le terminal de phase négatif, il y aura une variation de la différence entre le signal du terminal de phase positif et le signal du terminal de phase négatif au front montant ou descendant, et cette variation changera avec la variation de la phase.Trest utilisé pour représenter la durée la plus courte entre le temps de montée et le temps de descente. Il peut être indiqué que lorsque le placement de phase est inférieur à zéro virgule deux deTr, la distorsion du signal est relativement faible et l’augmentation du décalage de phase entraîne une forte distorsion de la forme d’onde différentielle. Lorsque le décalage de phase dépasseTrune zone non monotone apparaîtra sur la forme d’onde. Ici, la zone non monotone est une ligne droite. Cependant, pour des signaux pratiques, en raison des réflexions, de fortes montées et descentes peuvent se produire dans la zone non monotone, avec formation d’impulsions parasites entraînant de faux déclenchements, ce qui doit être évité. De plus, le front montant de la forme d’onde différentielle devient lent avec l’augmentation du déphasage, ce qui peut conduire à un temps d’établissement insuffisant pour le signal de données et à un temps de maintien insuffisant pour le signal d’horloge.

• Influence sur le signal en mode commun

Le placement de phase d’un signal à borne unique n’aura pas d’influence sur la forme d’onde différentielle mais modifiera la forme d’onde des signaux en mode commun. Lorsque le placement de phase a lieu sur le signal de borne positive, une variation d’onde se produira sur les signaux en mode commun. Il peut être indiqué que l’ampleur des fluctuations est liée à la quantité de placement de phase. Lorsque la quantité de placement de phase est respectivement de 0,05Tr, 0,1Tr, 0,2Tret 0,5Tr, la plage de fluctuation du mode commun est respectivement de 5 %, 10 %, 20 % et 50 % de la plage de fluctuation initiale. Lorsque la phase augmente jusqu’àTrou plus, la fluctuation augmentera jusqu’à environ 100 %, ce qui constitue la plage de fluctuation la plus élevée. La variation du signal en mode commun peut entraîner un problème de CEM et, comme le signal en mode commun n’est pas reçu au terminal dans de nombreuses conditions, une réflexion se formera au niveau du terminal de réception, provoquant un « ringing » du signal. Par conséquent, la plage de fluctuation du signal en mode commun doit être réduite autant que possible.

En conclusion, un retard relatif trop important entre les paires différentielles peut provoquer de faux déclenchements de signaux, des réflexions de signal, des EMI et des problèmes de séquencement temporel. Cependant, le degré d’influence du retard relatif du signal dépend du facteur d’échelle compatible avec le signal.Tr. Lorsque le facteur d’échelle est de 0,05, la distorsion des signaux différentiels peut être presque ignorée. Cependant, pour les signaux en mode commun, lorsque le facteur d’échelle est de 0,05, la fluctuation de tension des signaux en mode commun peut être maintenue à environ 5 %. Ainsi, même en cas de réflexion totale, la tension de réflexion superposée sur les lignes de signal n’est que de 10 % de la fluctuation initiale, ce qui est généralement une valeur acceptable. Par conséquent, dans le processus deconception de PCB haute vitesse, le retard relatif de la ligne de signal différentiel dans les règles de régulation de routage peut être réglé à 0,05Trqui est capable de satisfaire l’exigence d’intégrité du signal.

Détermination de la catégorie de retard relatif

Sur la base de l’analyse ci-dessus, la clé de la détermination de la catégorie isométrique différentielle, c’est-à-dire la détermination du retard relatif des paires différentielles, réside dans la détermination deTrfaisant référence à la plus petite valeur entre le temps haut et le temps bas des signaux différentiels. La valeur de sortie du temps de montée et du temps de descente est en réalité le résultat de la combinaison de l’impédance et de la capacité. Par conséquent, le temps de montée/descente sans charge est en fait le temps de montée/descente intrinsèque.

Les trois méthodes suivantes peuvent être appliquées pour obtenir la valeur deTr:

•Le temps de montée/descente peut être directement obtenu à partir des manuels des composants. Cependant, dans la plupart des cas, ce paramètre n’est pas fourni.

•Valeur deTrpeuvent être obtenus à partir des mots-clés Ramp du modèle IBIS (Input/Output Buffer Informational Specification) du composant. Les paramètres de temps de montée/descente sous les mots-clés Ramp sont généralement mesurés au port de sortie connecté à une résistance de 50 Ω, ce qui correspond habituellement à 20 % à 80 % du temps de la tension finale. Puisque les paramètres sont obtenus sans prendre en compte l’influence du boîtier, il est strict pour nous d’utiliser le temps de montée/descente comme la valeur deTr.

•La valeur deTrpeut être estimée en fonction de la fréquence d’horloge minimale ou de la fréquence d’horloge maximale des signaux de sortie. Étant donné que le front montant distribué représente approximativement 10 % de la fréquence d’horloge dans la plupart des systèmes numériques à haute vitesse, la valeur deTrpeut être estimé avec la période d’horloge minimale Tclk fournie sur la base de la formule :Tr=Tclkx 10 %.

La valeur estimée obtenue à partir de la période d’horloge est généralement stricte, car les paramètres parasites du boîtier ou la charge des composants ralentissent considérablement le temps de montée/descente intrinsèque des transistors.

Dans le travail pratique, dans la plupart des situations, les concepteurs de circuits ne fournissent pas d’informations surTraux ingénieurs de routage PCB qui ne reçoivent que des exigences ambiguës en matière de contrôle isométrique différentiel. La troisième méthode fournit sans aucun doute un schéma simple aux ingénieurs de routage PCB dès lors que la fréquence d’horloge la plus élevée sur la ligne de signal est obtenue. La fréquence d’horloge la plus élevée est considérée comme le paramètre de conception le plus fiable pour les concepteurs de circuits et elle est généralement fournie aux ingénieurs de routage PCB au début de la conception du PCB.

La troisième méthode conduit généralement à une liste de valeurs de référence dans la catégorie de contrôle de délai relatif entre paires différentielles, comme le montre le tableau ci-dessous.

| Fréquence d’horloge/ns | Fréquence d’horloge/MHz | Catégorie de retard relatif/ps | Longueur de ligne de transmission/mil |

| 3,75 | 266 | 18,8 | 105 |

| 3 | 333 | 15 | 84 |

| 2,5 | 400 | 12,5 | 70 |

| 1,87 | 533 | 9,4 | 52 |

| 1,5 | 667 | 7,5 | 42 |

| 1,25 | 800 | 6.3 | 35 |

Vérification de la simulation

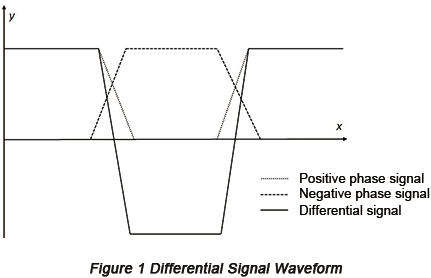

Prenons le signal différentiel DQS (Data Strobe) entre le TSM320 et le MT41J256M16 comme exemple, Cadencelogiciel de simulationest appliqué pour transmettre le signal DOS à la mémoire DRR3 afin de simuler la puce de contrôle de mémoire, d’analyser son influence sur le temps d’établissement et de maintien du signal de données et de vérifier l’analyse ci-dessus. Le circuit de simulation est présenté sur la Figure 2 ci-dessous.

D’après la Figure 2, la tension de référence des broches de sortie est de 1,5 V ; la puce de contrôle de la mémoire est directement connectée à la puce mémoire via le mode ODT (On-Die Termination) avec une ligne de transmission de 800 mil ; l’impédance différentielle est de 100 Ω et la fréquence d’horloge de simulation est de 800 MHz. Une ligne de transmission de 50 Ω est connectée en série à la borne de phase positive DQS pour simuler le phénomène de désaccord des paires différentielles. Dans le cas de différentiels isométriques, la longueur de la ligne de transmission à borne unique de 50 Ω est de 0 mil.

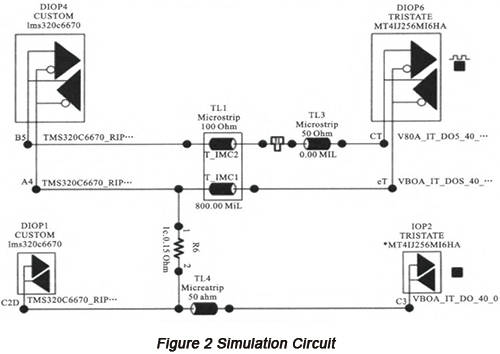

La simulation est effectuée sur le circuit isométrique différentiel. La figure 3 illustre le signal de sortie à la borne de phase positive des signaux différentiels. D’après les mesures, le temps de montée est d’environ 216 ps tandis que le temps de descente est de 219 ps, ce qui donne le temps de montée/descente minimal.Trdevrait être 216 ps.

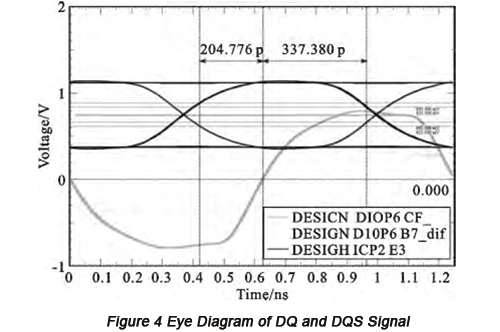

La figure 4 est un diagramme de l’œil du signal de données DQ et du signal de validation DQS obtenu par simulation, avec un temps d’établissement de 205 ps et un temps de maintien de 337 ps. Selon la fréquence de commutation des signaux DQS et DQ obtenue par simulation et d’après le manuel des données, le temps d’établissement minimal des signaux de données requis par le terminal de réception doit être de 85 ps et le temps de maintien minimal de 95 ps. Par conséquent, la marge par rapport au temps d’établissement minimal est de 120 ps et celle du temps de maintien est de 242 ps.

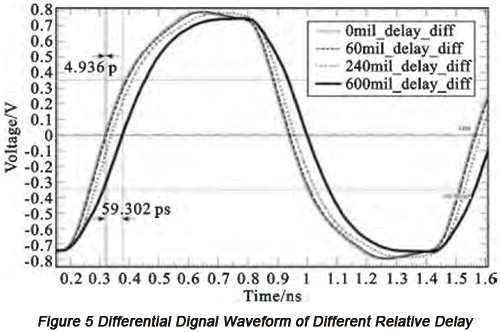

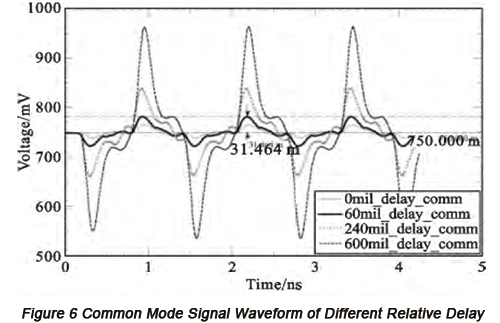

La situation de l’existence de 0,05Trplacement de phase, 0,2Trplacement de phase et 0,5TrIl faut tenir compte du placement de phase au niveau de la borne de phase positive. Le circuit peut être simulé avec une longueur de ligne de transmission à borne unique respectivement fixée à 60 mil, 240 mil et 600 mil. Les formes d’onde du signal différentiel et du signal en mode commun obtenues par simulation sur 4 itérations sont illustrées aux figures 5 et 6.

D’après la Figure 5, la distorsion est minimale lorsque les retards relatifs sont de 0,05Tret 0,2Travoir lieu. Surtout lorsque le retard relatif est de 0,05Tr, seul un placement d’environ 5 ps entre le signal différentiel et la forme d’onde du signal différentiel sans retard relatif, de sorte que la marge de mise en place du signal de données soit augmentée d’environ 5 ps tandis que la marge de maintien soit réduite de 5 ps. Bien que la marge de maintien soit réduite, cette quantité de placement est très faible par rapport au temps de maintien de 242 ps. Le séquencement temporel peut être évité. Pour la situation où le retard relatif est de 0,5Tr, le placement de la forme d’onde du signal DQS a atteint environ 60 ps. Bien que ce placement soit encore dans la catégorie de la sur‑mesure, il convient d’y prêter une attention suffisante.

D’après la Figure 6, l’augmentation du placement de phase entraîne une fluctuation périodique évidente des ondes et l’augmentation progressive de l’amplitude. Lorsque le retard relatif est respectivement de 0,05Tr, 0,2Tret 0,5Trla valeur de crête mesurée du signal en mode commun est respectivement de 61 mV, 176 mV et 430 mV, parmi lesquelles la plus élevée est sept fois la plus faible. La plus grande plage de fluctuation est respectivement de 4,3 %, 12 % et 29 %.

En conclusion, le résultat de la simulation est compatible avec le résultat obtenu par l’analyse du diagramme de la fonction mathématique. Lorsque le retard relatif entre les paires différentielles est inférieur à 0,05Tr, l’influence sur les signaux est assez faible.

La période d’horloge minimale du signal de sortie au terminal de sortie est utilisée pour estimer la catégorie de contrôle du retard relatif. D’après le manuel du composant, la période d’horloge minimale des composants est de 1,25 ns avec une fréquence d’horloge de 800 MHz. Selon le Tableau 1, le retard relatif doit être contrôlé dans une plage de 6,3 ps avec une longueur de ligne de transmission de 35 mil. De toute évidence, cette valeur est bien inférieure à la catégorie de contrôle du retard relatif de 0,05.Trpar la simulation. Par conséquent, la catégorie de contrôle du retard relatif estimée est relativement conservatrice, ce qui est plus spécifique que le résultat simulé.

Ressources utiles

•Recherche sur la conception de PCB haute vitesse dans les systèmes d’application embarqués

•Comment concevoir des plans d’image pour des circuits imprimés haute vitesse

•Défis de conception de PCB haute vitesse en matière d’intégrité du signal et leurs solutions

•Simulation de circuits imprimés avec OrCAD PSpice

•Service complet de fabrication de PCB par PCBCart - Multiples options à valeur ajoutée

•Service avancé d’assemblage de PCB par PCBCart - À partir d’une seule pièce