PCB aggiunto con successo al carrello

Elaborazione Isometrica Differenziale e Verifica tramite Simulazione nella Progettazione di PCB ad Alta Velocità

I segnali trasmessi nelle linee di segnale differenziali contengono una componente in modalità differenziale e una componente in modalità comune dei segnali.

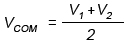

La quantità di segnali differenziali si riferisce alla differenza tra due segnali secondo la formulaVdiff=V1-V2La quantità di segnali in modo comune si riferisce alla metà della somma di due segnali secondo la formula Pertanto, la variazione di tensione di una singola linea porta inevitabilmente a un’influenza simultanea sui segnali in modo differenziale e sui segnali in modo comune. Successivamente, si utilizza un software di grafica per tracciare il diagramma della funzione matematica al fine di studiare rispettivamente l’influenza sui segnali in modo differenziale e sui segnali in modo comune. Per comodità di ricerca, i segnali possono essere analizzati simulandoli come forme d’onda trapezoidali con lo stesso tempo di salita e di discesa.

Pertanto, la variazione di tensione di una singola linea porta inevitabilmente a un’influenza simultanea sui segnali in modo differenziale e sui segnali in modo comune. Successivamente, si utilizza un software di grafica per tracciare il diagramma della funzione matematica al fine di studiare rispettivamente l’influenza sui segnali in modo differenziale e sui segnali in modo comune. Per comodità di ricerca, i segnali possono essere analizzati simulandoli come forme d’onda trapezoidali con lo stesso tempo di salita e di discesa.

• Influenza sui segnali differenziali

Il segnale del terminale di fase positiva, il segnale del terminale di fase negativa e il segnale differenziale delle coppie di linee differenziali sono mostrati nella Figura 1 sottostante, in cui la linea continua rappresenta l’onda del segnale differenziale.

Se un posizionamento di fase avviene dal terminale di fase positivo al terminale di fase negativo, ci sarà una variazione della differenza tra il segnale del terminale di fase positivo e il segnale del terminale di fase negativo sul fronte di salita o di discesa e tale variazione cambierà con il cambiamento della fase.Trviene utilizzato per indicare il tempo più breve tra il tempo di salita e quello di discesa. Si può indicare che quando il posizionamento di fase è inferiore a zero virgola due diTr, la distorsione del segnale è relativamente piccola e l’aumento del posizionamento di fase porta a una forte distorsione della forma d’onda differenziale. Quando il posizionamento di fase superaTr, un'area non monotona si verificherà sull'onda. Qui l'area non monotona è una linea retta. Tuttavia, per segnali pratici, a causa delle riflessioni, possono verificarsi grandi salite e discese nell'area non monotona con la formazione di impulsi di interferenza che portano a falsi trigger, cosa che dovrebbe essere evitata. Inoltre, il fronte superiore dell'onda differenziale diventa lento con l'aumento dello sfasamento, il che può portare a un tempo di assestamento insufficiente per il segnale di dati e a un tempo di mantenimento insufficiente per il segnale di clock.

• Influenza sul segnale di modo comune

Il posizionamento di fase del segnale a singolo terminale non avrà influenza sulla forma d’onda differenziale, ma cambierà la forma d’onda dei segnali di modo comune. Quando il posizionamento di fase avviene sul segnale del terminale positivo, si verificherà una variazione d’onda sui segnali di modo comune. Si può indicare che l’intervallo di fluttuazione è correlato all’entità del posizionamento di fase. Quando l’entità del posizionamento di fase è rispettivamente 0,05Tr, 0,1Tr, 0,2Tre 0,5Tr, l'intervallo di fluttuazione del modo comune è rispettivamente il 5%, 10%, 20% e 50% dell'intervallo di fluttuazione originale. Quando la fase aumenta aTro più, la fluttuazione aumenterà fino a circa il 100%, che è il più alto intervallo di fluttuazione. La variazione del segnale di modo comune può causare problemi di EMI e, poiché il segnale di modo comune non viene ricevuto al terminale in molte condizioni, si formeranno riflessioni al terminale ricevente, causando il ronzio del segnale. Pertanto, l’intervallo di fluttuazione del segnale di modo comune dovrebbe essere ridotto il più possibile.

In conclusione, un ritardo relativo eccessivo tra le coppie differenziali può causare falsi trigger dei segnali, riflessioni di segnale, EMI e problemi di temporizzazione. Tuttavia, il grado di influenza del ritardo relativo del segnale dipende dal fattore di scala compatibile con il segnaleTrQuando il fattore di scala è 0,05, la distorsione dei segnali differenziali può essere quasi ignorata. Tuttavia, per i segnali di modo comune, quando il fattore di scala è 0,05, la fluttuazione di tensione dei segnali di modo comune può essere controllata a circa il 5%. Quindi, anche in condizioni di riflessione totale, la tensione di riflessione sovrapposta alle linee di segnale è solo il 10% della fluttuazione originale, che è solitamente un valore accettabile. Pertanto, nel processo diprogettazione PCB ad alta velocitànelle regole di regolamentazione del routing, il ritardo relativo della linea di segnale differenziale può essere impostato su 0,05Trche sia in grado di soddisfare il requisito di integrità del segnale.

Determinazione della categoria di ritardo relativo

Sulla base dell'analisi di cui sopra, la chiave per determinare la categoria isometrica differenziale, cioè la determinazione del ritardo relativo delle coppie differenziali, risiede nella determinazione diTrfacendo riferimento al valore più piccolo tra il tempo alto e il tempo basso dei segnali differenziali. L’uscita del tempo di salita e del tempo di discesa è in realtà il risultato della combinazione di impedenza e capacità. Pertanto, il tempo di salita/discesa senza carico è in realtà il tempo di salita/discesa intrinseco.

I seguenti tre metodi possono essere applicati per ottenere il valore diTr:

•Il tempo di salita/discesa può essere ottenuto direttamente dai manuali dei componenti. Tuttavia, nella maggior parte dei casi, questo parametro non viene fornito.

•Valore diTrpuò essere ottenuto dalle parole chiave Ramp del modello IBIS (Input/Output Buffer Informational Specification) del componente. I parametri di tempo di salita/discesa sotto le parole chiave Ramp sono generalmente misurati alla porta di uscita collegata a un resistore da 50 Ω, che di solito corrispondono al tempo dal 20% all’80% della tensione finale. Poiché i parametri sono ottenuti senza considerare l’influenza del package, per noi è rigoroso usare il tempo di salita/discesa come valore diTr.

•Il valore diTrpuò essere stimato in base alla frequenza di clock minima o alla frequenza di clock massima dei segnali di uscita. Poiché il fronte di salita distributivo è approssimativamente il 10% della frequenza di clock nella maggior parte dei sistemi digitali ad alta velocità, il valore diTrpuò essere stimato con il periodo di clock minimo Tclk fornito in base alla formula:Tr=Tclkx 10%.

Il valore stimato ottenuto tramite il periodo di clock è solitamente rigoroso perché i parametri parassiti del package o il carico dei componenti rallentano notevolmente il tempo di salita/discesa intrinseco nei transistor.

Nel lavoro pratico, nella maggior parte delle situazioni, i progettisti di circuiti non forniscono informazioni suTrai progettisti di layout PCB che ricevono solo alcune richieste ambigue in termini di controllo isometrico differenziale. Il terzo metodo fornisce senza dubbio uno schema semplice ai progettisti di layout PCB, purché sia ottenuta la massima frequenza di clock sulla linea di segnale. La massima frequenza di clock è considerata il parametro di progettazione più affidabile per i progettisti di circuiti ed è solitamente fornita ai progettisti di layout PCB all’inizio della progettazione del PCB.

Il terzo metodo di solito porta a un elenco di valori di riferimento all'interno della categoria di controllo del ritardo relativo tra coppie differenziali, come mostrato nella tabella seguente.

| Frequenza di clock/ns | Frequenza di clock/MHz | Categoria di ritardo relativo/ps | Lunghezza della linea di trasmissione/mil |

| 3,75 | 266 | 18,8 | 105 |

| 3 | 333 | 15 | 84 |

| 2,5 | 400 | 12,5 | 70 |

| 1,87 | 533 | 9,4 | 52 |

| 1,5 | 667 | 7,5 | 42 |

| 1,25 | 800 | 6,3 | 35 |

Verifica della simulazione

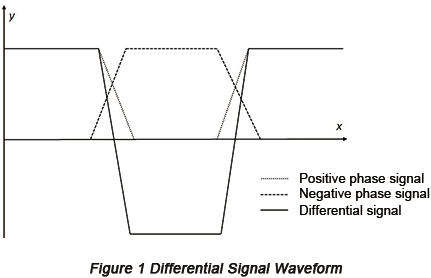

Prendendo come esempio il segnale differenziale DQS (Data Strobe) tra TSM320 e MT41J256M16, Cadencesoftware di simulazioneviene applicato per trasmettere il segnale DOS alla memoria DRR3 per simulare il chip di controllo della memoria, analizzare la sua influenza sul tempo di setup e hold del segnale dati e verificare l’analisi di cui sopra. Il circuito di simulazione è mostrato nella Figura 2 seguente.

In base alla Figura 2, la tensione di riferimento dei pin di uscita è 1,5 V; il chip di controllo della memoria è collegato direttamente al chip di memoria tramite la modalità ODT (On-Die Termination) con una linea di trasmissione di 800 mil; l’impedenza differenziale è di 100 Ω e la frequenza di clock di simulazione è di 800 MHz. Una linea di trasmissione da 50 Ω è collegata in serie al terminale di fase positiva del DQS per simulare il fenomeno di discrepanza delle coppie differenziali. Nel caso di differenziali isometrici, la lunghezza della linea di trasmissione a singolo terminale da 50 Ω è di 0 mil.

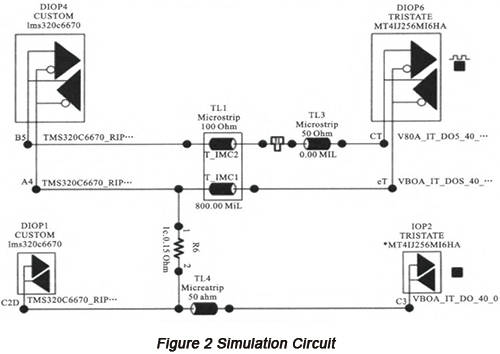

La simulazione viene eseguita sul circuito isometrico differenziale. La Figura 3 illustra il segnale di uscita al terminale di fase positiva dei segnali differenziali. Attraverso la misurazione, il tempo di salita è approssimativamente 216 ps mentre il tempo di discesa è 219 ps, quindi il tempo minimo di salita/discesaTrdovrebbe essere 216 ps.

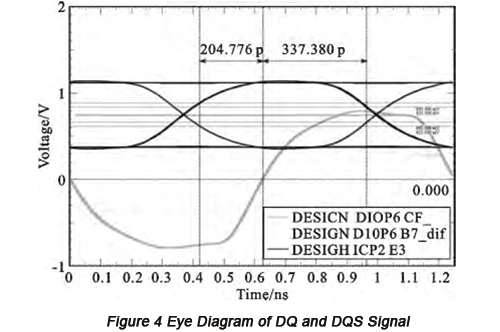

La Figura 4 è un diagramma a occhio del segnale di dati DQ e del segnale di gating DQS ottenuto tramite simulazione, con un tempo di setup di 205 ps e un tempo di hold di 337 ps. In base alla velocità di commutazione dei segnali DQS e DQ ottenuta tramite simulazione e secondo il manuale dei dati, il tempo minimo di setup dei segnali di dati richiesto dal terminale ricevente è di 85 ps e il tempo minimo di hold è di 95 ps. Pertanto, il margine rispetto al tempo minimo di setup è di 120 ps e quello rispetto al tempo minimo di hold è di 242 ps.

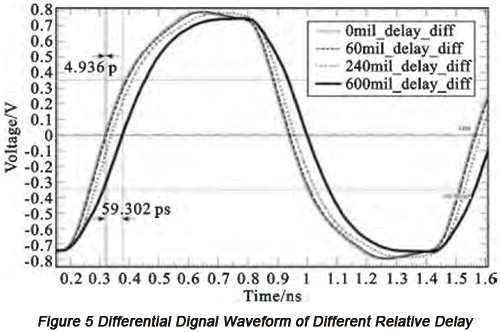

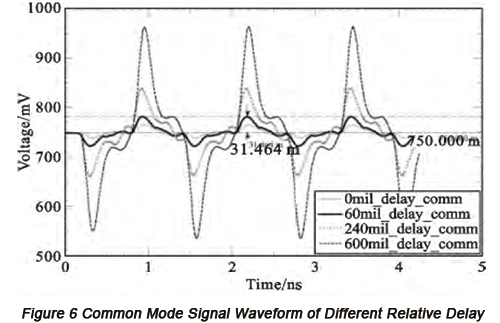

La situazione dell'esistenza di 0,05Trposizionamento di fase, 0,2Trposizionamento di fase e 0,5Tril posizionamento di fase al terminale di fase positivo deve essere preso in considerazione. Il circuito può essere simulato con una linea di trasmissione a singolo terminale la cui lunghezza è rispettivamente impostata a 60 mil, 240 mil e 600 mil. Le forme d’onda del segnale differenziale e del segnale di modo comune ottenute tramite simulazione per 4 volte sono illustrate nelle Figure 5 e 6.

In base alla Figura 5, la distorsione è minima quando i ritardi relativi sono pari a 0,05Tre 0,2Travvenire. Soprattutto quando il ritardo relativo è 0,05Tr, solo il posizionamento di circa 5 ps dal segnale differenziale alla forma d’onda del segnale differenziale senza ritardo relativo fa sì che il margine di setup del segnale dati aumenti di circa 5 ps mentre il margine di hold diminuisca di 5 ps. Sebbene il margine di hold diminuisca, questa quantità di posizionamento è così piccola rispetto al tempo di hold di 242 ps. La sequenza temporale può essere evitata. Per la situazione in cui il ritardo relativo è 0,5Tril posizionamento della forma d’onda del segnale DQS ha raggiunto circa 60 ps. Sebbene questo posizionamento rientri ancora nella categoria di sovramisurazione, è necessario prestare sufficiente attenzione.

In base alla Figura 6, l’aumento del posizionamento di fase porta a un’evidente fluttuazione periodica delle onde e al graduale aumento della portata. Quando il ritardo relativo è rispettivamente 0,05Tr, 0,2Tre 0,5Tril valore di picco misurato del segnale di modo comune è rispettivamente 61 mV, 176 mV e 430 mV, tra i quali il valore più alto è sette volte quello più basso. Il più ampio intervallo di fluttuazione è rispettivamente 4,3%, 12% e 29%.

In conclusione, il risultato della simulazione è compatibile con il risultato ottenuto tramite l’analisi del diagramma della funzione matematica. Quando il ritardo relativo tra le coppie differenziali è inferiore a 0,05Trl'influenza sui segnali è piuttosto piccola.

Il periodo minimo di clock del segnale in uscita al terminale di uscita viene applicato per stimare la categoria di controllo del ritardo relativo. In base al manuale del componente, il periodo minimo di clock dei componenti è 1,25 ns con una frequenza di clock di 800 MHz. Secondo la Tabella 1, il ritardo relativo dovrebbe essere controllato entro 6,3 ps con una lunghezza della linea di trasmissione di 35 mil. Apparentemente, questo valore è molto più piccolo della categoria di controllo del ritardo relativo di 0,05Trattraverso la simulazione. Pertanto, la categoria di controllo del ritardo relativo stimata è relativamente conservativa, risultando più specifica rispetto al risultato simulato.

Risorse utili

•Ricerca sulla progettazione di PCB ad alta velocità nei sistemi di applicazioni embedded

•Come progettare i piani di massa per PCB ad alta velocità

•Sfide dell’integrità del segnale nella progettazione di PCB ad alta velocità e loro soluzioni

•Simulazione PCB con OrCAD PSpice

•Servizio completo di produzione PCB da PCBCart - Molteplici opzioni a valore aggiunto

•Servizio avanzato di assemblaggio PCB da PCBCart - A partire da 1 pezzo