PCB がショッピングカートに正常に追加されました

高速PCB設計における差動アイソメトリック処理とシミュレーション検証

差動信号線で伝送される信号には、信号の差動モード成分とコモンモード成分が含まれる。

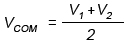

差動信号の量は、次の式に従う2つの信号の差を指しますV差分=V1-V2共通モード信号の量は、次の式に従う2つの信号の和の半分を指します。 したがって,単一ラインの電圧変化は,差動モード信号およびコモンモード信号の両方に同時に影響を及ぼすことになる。次に,グラフ作成ソフトウェアを用いて数学関数の図を描き,差動モード信号およびコモンモード信号への影響をそれぞれ検討する。研究を容易にするために,信号は立ち上がり時間と立ち下がり時間が同一の台形波形にシミュレートして解析することができる。

したがって,単一ラインの電圧変化は,差動モード信号およびコモンモード信号の両方に同時に影響を及ぼすことになる。次に,グラフ作成ソフトウェアを用いて数学関数の図を描き,差動モード信号およびコモンモード信号への影響をそれぞれ検討する。研究を容易にするために,信号は立ち上がり時間と立ち下がり時間が同一の台形波形にシミュレートして解析することができる。

・差動信号への影響

差動ラインペアの正相端子信号、負相端子信号および差動信号を以下の図1に示す。実線は差動信号波を表す。

正相端子から負相端子への位相配置が行われると、立ち上がりまたは立ち下がりエッジにおいて、正相端子信号と負相端子信号の差分に変化が生じ、この変化は位相の変化に伴って変動する。Trは、立ち上がり時間と立ち下がり時間のうち短い方を表すために使用されます。位相配置が 0.2 未満である場合を示すことができます。Tr信号の歪みは比較的小さく、位相配置の増加により差動波形の強い歪みが生じる。位相配置が…を超えるとTr波形上に非単調領域が生じる。このとき非単調領域は直線となる。しかし、実際の信号では反射のため、非単調領域で大きな上下変動が発生し、干渉パルスが形成されて誤動作トリガを引き起こす可能性があり、これは回避しなければならない。さらに、位相配置の増加に伴い、差動波形の立ち上がりエッジが遅くなり、データ信号の立ち上がり時間が不足したり、クロック信号のホールド時間が不足したりする可能性がある。

・コモンモード信号への影響

単一端子信号の位相配置は、差動波形には影響を与えないが、コモンモード信号の波形を変化させる。位相配置が正端子信号側で行われると、コモンモード信号に波形変化が生じる。変動範囲は位相配置量に関連していることが示される。位相配置量がそれぞれ0.05のときTr, 0.1Tr, 0.2Trと0.5Tr共通モードの変動範囲は、それぞれ元の変動範囲の 5%、10%、20% および 50% である。位相が増加するときTrさらに大きくなると、変動幅は最大変動範囲である約100%まで増加します。コモンモード信号の変化はEMI問題を引き起こす可能性があり、多くの条件下ではコモンモード信号が終端で受信されないため、受信側終端で反射が発生し、信号リンギングを招きます。したがって、コモンモード信号の変動幅は可能な限り小さく抑える必要があります。

結論として、差動ペア間の相対遅延が大きすぎると、信号の誤トリガ、信号反射、EMI およびタイミングシーケンスの問題を引き起こす可能性があります。しかし、相対遅延信号の影響度は、信号と整合するスケールファクターに依存します。Trスケールファクタが 0.05 の場合、差動信号の歪みはほとんど無視できます。しかし、コモンモード信号については、スケールファクタが 0.05 のとき、コモンモード信号の電圧変動はおよそ 5% に抑えることができます。したがって、全反射が生じる状況であっても、信号線上に重畳される反射電圧は元の変動量のわずか 10% にとどまり、これは通常許容可能な値です。したがって、そのプロセスにおいて高速PCB設計配線規則において、差動信号線の相対遅延は 0.05 に設定できますTr信号の完全性の要件を満たすことができる。

相対遅延カテゴリの判定

上記の解析に基づくと、差動アイソメトリックカテゴリの判定、すなわち差動ペアの相対遅延の判定の要点は、〜の判定にある。Tr差動信号の立ち上がり時間と立ち下がり時間のうち、より小さい値を指します。立ち上がり時間および立ち下がり時間の出力は、実際にはインピーダンスとキャパシタンスの組み合わせによる出力です。したがって、負荷のない立ち上がり/立ち下がり時間は、本来の(固有の)立ち上がり/立ち下がり時間となります。

次の3つの方法を適用して、~の値を取得できますTr:

•立ち上がり時間/立ち下がり時間は、部品のマニュアルから直接取得できます。しかし、ほとんどの場合、このパラメータは記載されていません。

•価値Trは、コンポーネントの IBIS(Input/Output Buffer Information Specification)モデルの Ramp キーワードから取得することができます。Ramp キーワード下の立ち上がり/立ち下がり時間パラメータは、一般的に 50Ω の抵抗が接続された出力ポートで測定され、通常は最終電圧の 20% から 80% までの時間です。これらのパラメータはパッケージの影響を考慮せずに取得されるため、立ち上がり/立ち下がり時間をその値として使用することは、私たちにとって厳密なものとなります。Tr。

•The value ofTr出力信号の最小クロック周波数または最大クロック周波数に基づいて推定することができる。ほとんどの高速デジタルシステムでは、分布立ち上がりエッジはクロック周波数のおよそ 10% であるため、その値はTr次の式に基づいて与えられる最小クロック周期 Tclk を用いて見積もることができる:Tr=Tクリック×10%

クロック周期から得られる推定値は通常厳密なものになります。これは、パッケージの寄生パラメータや素子の負荷によって、トランジスタ本来の立ち上がり/立ち下がり時間が大きく遅くなってしまうためです。

実務においては、ほとんどの場合、回路設計者は~に関する情報を提供しないTr差動アイソメトリック制御に関してあいまいな要求しか受け取っていないPCBレイアウトエンジニアにとって、第3の方法は、信号線上の最高クロック周波数さえ把握できれば、間違いなく単純な手法を提供する。最高クロック周波数は回路設計者にとって最も信頼できる設計パラメータと見なされており、通常、PCB設計の初期段階でPCBレイアウトエンジニアに提供される。

3 番目の方法では通常、差動ペア間の相対遅延制御カテゴリ内における基準値の一覧が得られます。以下の表に示します。

| クロック周波数/ns | クロック周波数/MHz | 相対遅延カテゴリ/ps | 伝送線路長さ/mil |

| 3.75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1.25 | 800 | 6.3 | 35 |

シミュレーション検証

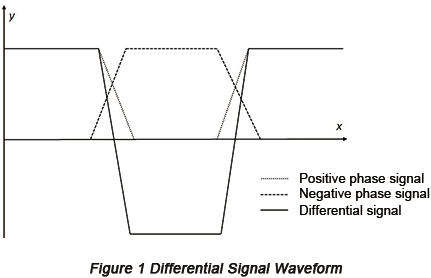

例として、TSM320 と MT41J256M16 間の DQS(データストローブ)差動信号を取り上げると、CadenceシミュレーションソフトウェアDRR3メモリにDOS信号を伝送してメモリ制御チップをシミュレートし、データ信号の立ち上がり・保持時間への影響を解析し、上記の解析を検証するために適用される。シミュレーション回路を図2に示す。

図2に基づくと、出力ピンの基準電圧は1.5Vであり、メモリ制御チップはODT(On-Die Termination)モードを介して、800milの伝送線路でメモリチップと直接接続されている。差動インピーダンスは100Ωで、シミュレーション時のクロック周波数は800MHzである。差動ペアの不一致現象をシミュレートするために、DQS正相端子に50Ωの伝送線路が直列接続されている。等長差動の場合、50Ωの単端伝送線路の長さは0milである。

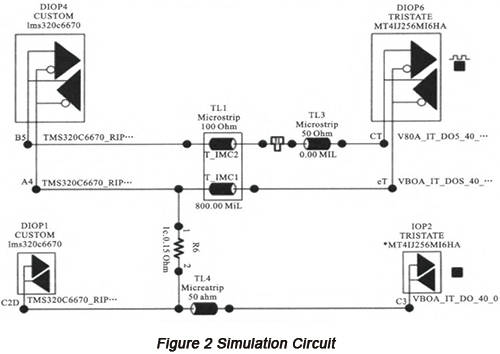

シミュレーションは差動アイソメトリック回路に対して実行される。図3は、差動信号の正相端子における出力信号を示している。測定の結果、立ち上がり時間は約216ps、立ち下がり時間は219psであり、したがって最小の立ち上がり/立ち下がり時間はTr216psであるべきです。

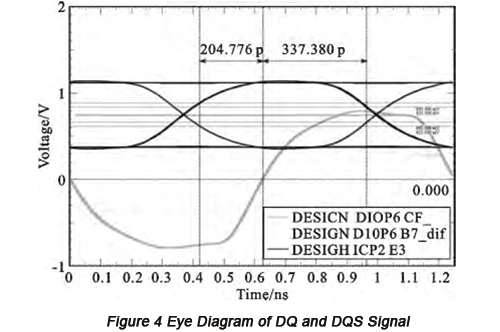

図4は、シミュレーションにより得られたデータ信号DQおよびゲーティング信号DQSのアイダイアグラムであり、セットアップ時間は205ps、ホールド時間は337psである。シミュレーションによるDQSおよびDQ信号の立ち上がり/立ち下がり速度とデータマニュアルに基づくと、受信端で要求されるデータ信号の最小セットアップ時間は85ps、最小ホールド時間は95psである。したがって、最小セットアップ時間のマージンは120ps、ホールド時間のマージンは242psとなる。

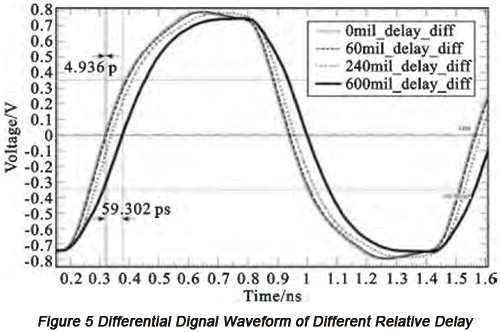

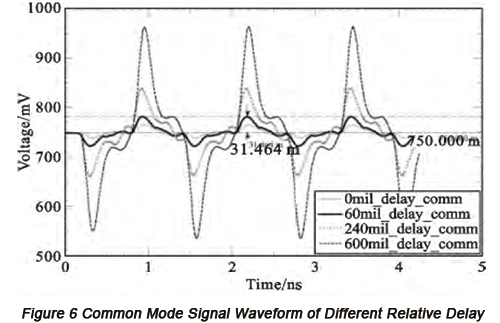

0.05の存在状況Tr位相配置、0.2Tr位相配置および0.5Tr正相端子での位相配置を考慮する必要がある。回路は、単端の伝送線路長をそれぞれ 60mil、240mil、600mil に設定してシミュレーションすることができる。4 回のシミュレーションによる差動信号波形およびコモンモード信号波形を図 5 および図 6 に示す。

図5に基づくと,相対遅延が0.05のとき,ひずみは最小となるTrおよび0.2Tr起こります。特に相対遅延が 0.05 のときに。Tr差動信号から差動信号波形までの配置を約 5ps とするだけで、相対遅延は発生せず、データ信号のセットアップ余裕は約 5ps 増加し、ホールド余裕時間は 5ps 減少する。ホールド余裕時間は減少するものの、この程度の配置量は 242ps のホールド時間に対してはごくわずかである。タイムシーケンスを回避することができる。相対遅延が 0.5 の場合にはTrDQS信号波形の配置は約60psに達しています。この配置は依然としてオーバーメジャーの範疇ではありますが、十分な注意を払う必要があります。

図6に基づくと,位相配置の増加は,波形に明らかな周期的変動をもたらし,レンジが徐々に増加することにつながる。相対遅延がそれぞれ0.05のときTr, 0.2Trと0.5Tr測定されたコモンモード信号のピーク値はそれぞれ 61mV、176mV、430mV であり、その中で最大値は最小値の 7 倍である。最大変動範囲はそれぞれ 4.3%、12%、29% である。

結論として、シミュレーション結果は数学関数の図による解析で得られた結果と一致している。差動ペア間の相対遅延が 0.05 未満の場合Tr信号への影響はかなり小さいです。

出力端子における出力信号の最小クロック周期は、相対遅延の制御カテゴリを見積もるために適用される。コンポーネントのマニュアルに基づくと、コンポーネントの最小クロック周期はクロック周波数 800MHz において 1.25ns である。表1によれば、伝送線路長が 35mil の場合、相対遅延は 6.3ps 以内に制御されなければならない。明らかに、この値は相対遅延の制御カテゴリ 0.05 よりもはるかに小さい。Trシミュレーションによって得られた結果である。そのため、推定された相対遅延制御の区分は比較的保守的であり、シミュレーション結果よりも具体的である。

役立つリソース

•組込み応用システムにおける高速PCB設計の研究

•高速PCB向けのイメージプレーン設計方法

•高速PCB設計における信号品質の課題とその解決策

•OrCAD PSpice を使用した PCB シミュレーション

・PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

•PCBCart の高度な PCB アセンブリサービス - 1 個から対応