電子科学技術の発展に伴い、ICチップで構成される電子システムは、大規模化、小型化および高速化の方向へ急速に発展している。同時に、電子システムの小型化により回路の配線密度が増大し、信号周波数は絶えず上昇し、信号の立ち上がり・立ち下がり時間も短くなるという問題が生じている。信号のインタコネクト遅延が信号の立ち上がり時間の10%を超えると、基板上の信号配線は伝送線路としての性質を示し、信号反射やクロストークといった一連の問題がますます顕在化する。高速化に伴う問題の出現はハードウェア設計により大きな課題をもたらし、論理的には正しいと見なされる設計であっても、高速性を考慮した適切な処理が行われなければ、システム全体の設計が失敗に終わる可能性がある。したがって、高速回路における問題をどのように解決するかは、システムの成否を左右する重要な要素の一つとなっている。

反省の原則とその影響

・反射の原理

反射の直接的な原因は、伝送線路のインピーダンスの不整合にあり、それによって終端で信号エネルギーが完全に吸収されないことが生じる。反射の問題は単一ネットワークの信号品質を反映しており、単一ネットワークの信号経路およびリターンパスの物理的特性に関連している。通常、物理的特性はPCB配線伝送線路に大きな影響を与える要因としては、主に配線材料、配線幅、配線厚さ、他の配線層およびプレーンとの距離、隣接材料の誘電率などが挙げられる。信号が単一ネットワークに沿って伝送されるとき、インターコネクト線路の過渡的なインピーダンス変化が生じる。もし信号が感じるインターコネクトのインピーダンスが一定に保たれていれば、波形は非歪のまま維持される。逆に、信号が感じるインターコネクトのインピーダンスが変化し続ける場合、その変化点で反射が発生し、歪みが生じる。反射した信号は信号の送信端へ戻り、さらに再反射を繰り返しながらエネルギーの減衰とともに縮小していく。最終的に、信号の電圧と電流は安定した状態に落ち着く。

・反射の計算

信号が伝送線路に沿って前方へ伝送されるとき、任意の時点で過渡インピーダンスが感じられる。信号が感じるインピーダンスが一定であれば、信号は正常に前方へ伝送される。感じられるインピーダンスが変化する限り、その原因が何であっても必ず反射が生じる。反射量を測る重要な指標は反射係数であり、これは反射電圧と元の信号電圧との比を示す。反射係数は次の式により定義できる。 。

。

この式において、Z1変更後のインピーダンスを指し、一方 Z は0変更前のインピーダンス。PCB配線の特性インピーダンスが 50Ω であると仮定する。伝送の過程で 150Ω の抵抗に遭遇すると、反射係数は (150-50)/(150+50)=1/2 となる(この場合、寄生容量や寄生インダクタンスの影響は考慮せず、抵抗は理想的な純抵抗とみなす)。この結果は、元の信号エネルギーの半分がソース端子へ反射されることを示している。伝送信号の電圧が 5V の場合、反射電圧は 2.5V となる。

・反射の影響

1). 反射によって生じる信号の歪み

リードが正しく終端されていない場合、駆動側からの信号パルスは受信端で反射されます。反射した信号が十分に強いと、重なり合った波形が論理状態を変化させ、予期しない影響を引き起こし、信号波形の歪みを招く可能性があります。歪みが顕著になると、多数のエラーが発生し、設計が失敗するおそれがあります。同時に、歪んだ信号はノイズに対して感度が高くなり、それによっても設計不良が生じる可能性があります。

2). 反射によって生じるオーバーシュートとアンダーシュート

オーバーシュートとは、最初のピーク値または谷値が電圧を超える現象を指します。立ち上がりエッジの場合は、最初のピーク値が最高電圧を超えることを指し、立ち下がりエッジの場合は、最初の谷値が最低電圧を超えることを指します。過度なオーバーシュートは保護ダイオードを破壊し、早期故障を引き起こす可能性があります。アンダーシュートとは、次の谷値またはピーク値が誤ったクロック信号を生成し、システムの誤読および誤書き込み動作を引き起こす可能性がある現象を指します。

3). 振動

オシレーションもまた、反射によって引き起こされる症状である。オーバーシュートと同様の性質を持ち、クロックサイクル内でオーバーシュートとアンダーシュートが繰り返し発生することをオシレーションと呼ぶ。これは、反射によって生じた余剰エネルギーが回路内でタイミングよく吸収されないことによって起こる結果である。

反射抑制方法

反射を引き起こす主な要因には、配線の幾何学的形状(幅、長さ、曲がり角度)、同一ネットワークにおける配線層の切り替え、コネクタを介した伝送、電源層とグランド層間の不連続、不適切なトポロジ構造、およびネットワーク終端の不整合が含まれる。主な抑制方法については、次の章で紹介する。

・システム周波数のエスカレーション

信号エッジの立ち上がり/立ち下がり速度は、可能な状況では低減され、信号と伝送線路が接続される前に、伝送線路上の反射が安定状態に達するようにする。

一方では設計規則を満たさなければならず、他方では異なる種類の信号が混在することを避けるため、低速なコンポーネントを選定する必要がある。

・信号処理の最適化

時間シーケンスに関する厳しい要求のため、高速上の問題を引き起こす可能性のあるコンポーネントおよびノードを事前に特定しておく必要があります。コンポーネントのレイアウトおよび配線に関するあらゆる要件を調整し、最終的に信号完全性の設計指標を制御します。主な処理方法には次のものが含まれます。

1).比較的薄いPCB基板スルーホールの寄生パラメータを低減するために適用される。

2).層数は適切に構成する必要があります。中間層を十分に活用してシールドを設定し、隣接グラウンドをより良く実装することで、寄生インダクタンスを効果的に低減し、信号の伝送長を短縮し、信号間のクロストークを大幅に向上させることができます。

3).PCB 上の信号ラインの幾何学的形状は、曲がりを減らし、配線のインピーダンス不連続点を最小限に抑えるように制御する必要があります。特に高周波回路での配線では、できる限り直線配線を適用すべきです。どうしても曲がりが必要な場合は、折れ線または 45° のアークを用いることで、高周波信号の外部放射および高周波信号同士の結合を低減することができます。

4).重要な信号ラインの配線は、不要なスルーホールを減らすために、同一平面上に配置する必要があります。

5).プレーンの完全性を確保し、信号ラインに対して低インピーダンスのリフローパスを提供する必要があります。これは、コモンモードインピーダンス結合およびコモンモードスイッチングノイズを低減し、電源システムに関する信号品質(シグナルインテグリティ)の問題を減少または排除することを目的としています。

6).正しいルーティングトポロジ構造の適用。

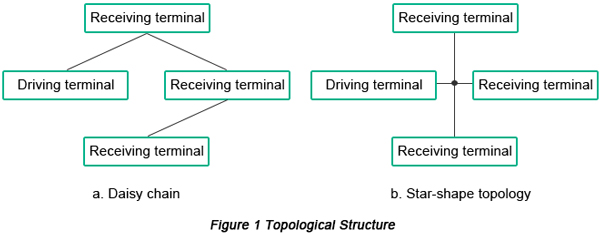

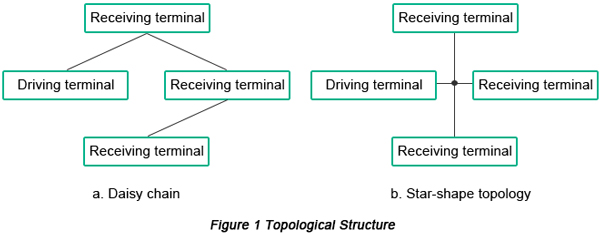

配線のトポロジ構造とは、信号線の配線順序および構造を指す。実際の回路では、1つのドライバソースが複数の負荷を駆動し、ドライバソースと負荷があるトポロジ構造に従う状況が常に存在する。異なるトポロジ構造は、信号に明らかに異なる影響を与える。通常、PCB配線には2種類の基本的なトポロジ構造が用いられ、それがデイジーチェーンとスター形トポロジであり、以下の図1に示す。

a. デイジーチェーン

ルーティングはドライバ端子から開始し、各受信端子へ順番に到達します。信号特性を変更するために直列抵抗を適用する場合、直列抵抗の位置はドライバ端子のすぐ近くに配置する必要があります。高調波干渉制御の観点では、デイジーチェーンは最も優れた配線効果を持ちます。しかし、この種のルーティングは配線可能性が最も低く、100%未満です。実際の設計では、デイジーチェーン内の分岐長は可能な限り短くする必要があります。このトポロジ構造の配線スペースは小さく、終端との互換性のために単一の抵抗を適用することができます。さらに、この種のルーティング構造では、異なる信号受信端子で信号受信のタイミングが同期しなくなります。

b. スター型トポロジー

この種の配線方式は、クロック信号の非同期化を効果的に回避することが可能ですが、各ブランチごとに終端抵抗が必要になるという欠点があります。終端抵抗の抵抗値は、ラインの特性インピーダンスと整合していなければなりません。異なる信号が受信端で同時に要求されるシステムに対しては、スター型トポロジが最も適しています。

・終了方法

信号伝送路の特性インピーダンスは一定に保たれなければならず、すなわち反射係数が0であり、伝送路上に反射がないことを意味する。この状態をインピーダンス整合と呼ぶ。このとき、信号は理想的に終端まで伝送される。一般的に、伝送線路の長さはこの条件に適合していなければならない。 。

。

この不等式において、L は伝送線路の長さを表します。trソース端子信号の立ち上がり時間を指します。tpd1伝送線路の単位長さあたりの負荷伝送遅延を指す。統合レベルの伝送が遠端に反射が到達する前に行われる場合、終端マッチング技術を適用する必要がある。伝送線路の終端接続の原則として、負荷反射係数または信号源反射係数のいずれかがゼロであれば、反射は消滅する。一般的に、2つの戦略が用いられる。すなわち、信号源インピーダンスを伝送線路インピーダンスに整合させる「ソース終端」と、負荷インピーダンスを伝送線路インピーダンスに整合させる「エンド終端」である。

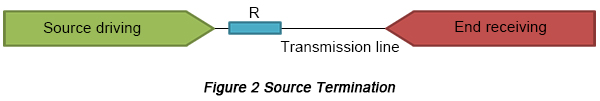

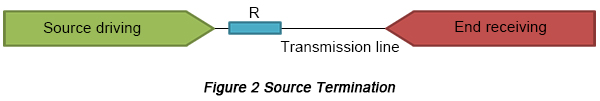

1). ソース終端

ソース終端は主にシリーズ終端方式であり、送信源近傍の位置で伝送線路に直列抵抗を挿入して実装される。直列抵抗の抵抗値とドライバ端子の抵抗値の合計は、伝送線路の抵抗値と等しくなければならない。シリーズ終端の原理は、負荷端からの反射電圧を除去することであり、伝送線路における二次反射を防止することにある。この原理を図2に示す。

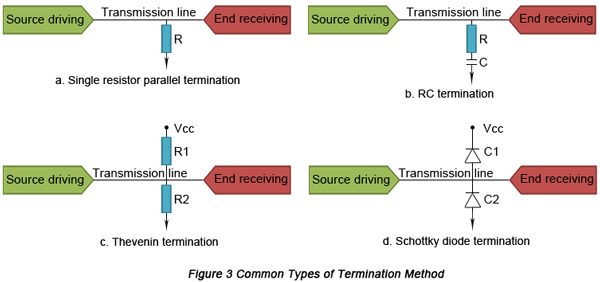

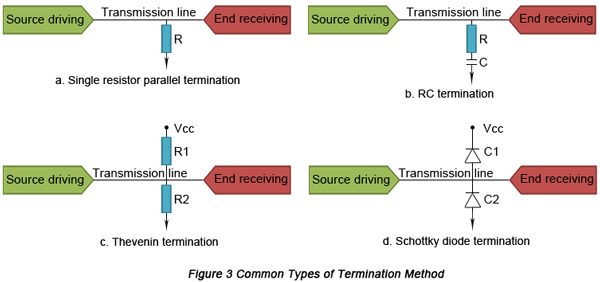

2). エンド終端

エンドターミネーションの主な原理は、インピーダンスマッチングを実現するために、負荷端子に隣接する位置にプルアップまたはプルダウン抵抗を追加することにある。エンドターミネーションは一般的に、単一抵抗並列終端、RC終端、テブナン終端、およびショットキーダイオード終端に分類され、図3に示すとおりである。

単一抵抗の並列終端における抵抗値は、伝送線路のインピーダンスと等しくなります。テブナン終端における2つの抵抗値は、次の式に従う必要があります。Z0=R1R2/(R1+R2)・RC終端における容量値は、次の式に従います。C=3T/Z0その中でT信号の立ち上がり時間を指し、一方 Z は0伝送線路のインピーダンスを指す。

システム設計の観点からは、他の3つの終端方式と比較して、ノイズ、EMI および RFI を最も低減できるため、まず並列終端を採用すべきである。実際の状況に応じて適切な終端方式を選択し、必要に応じてシミュレーション設計を実施すること。

結論

中で高速PCB設計成功するための前提条件には、合理的なレイアウトと配線、不要な折り返しやスルービアの回避、インピーダンスの連続性、一体化された信号リファレンスプレーン、および優れたグラウンディングが含まれます。設計と信号完全性を最適化し、より高い電磁両立性を得るためには、設計シミュレーション検証を実施する必要があります。これにより、設計者は設計上の欠陥にタイムリーに対処し、PCB設計における不足を補うことができます。

役立つリソース

•高速レイアウトのコツ

•高速PCB設計における信号品質の課題とその解決策

•高速デジタル・アナログ混在回路におけるシグナルインテグリティ解析とPCB設計

•PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

•PCBCart の高度な PCB アセンブリサービス - 1 個から対応

。

。

。

。