PCB berjaya ditambahkan ke troli beli-belah anda

Pemprosesan Isometrik Diferensial dan Pengesahan Simulasi bagi Reka Bentuk PCB Berkelajuan Tinggi

Isyarat yang dihantar dalam talian isyarat pembezaan mengandungi komponen mod pembezaan dan komponen mod umum bagi isyarat.

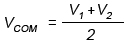

Jumlah isyarat pembeza merujuk kepada perbezaan antara dua isyarat mengikut formula berikutVperbezaan=V1-V2. Jumlah isyarat mod biasa merujuk kepada separuh daripada jumlah dua isyarat mengikut formula Oleh itu, perubahan voltan pada satu talian sudah pasti membawa kepada pengaruh serentak ke atas isyarat mod pembezaan dan isyarat mod umum. Seterusnya, perisian graf digunakan untuk melukis rajah fungsi matematik bagi mengkaji secara berasingan pengaruh ke atas isyarat mod pembezaan dan isyarat mod umum. Untuk memudahkan penyelidikan, isyarat boleh dianalisis dengan mensimulasikannya kepada bentuk gelombang trapezoid dengan masa naik dan masa turun yang sama.

Oleh itu, perubahan voltan pada satu talian sudah pasti membawa kepada pengaruh serentak ke atas isyarat mod pembezaan dan isyarat mod umum. Seterusnya, perisian graf digunakan untuk melukis rajah fungsi matematik bagi mengkaji secara berasingan pengaruh ke atas isyarat mod pembezaan dan isyarat mod umum. Untuk memudahkan penyelidikan, isyarat boleh dianalisis dengan mensimulasikannya kepada bentuk gelombang trapezoid dengan masa naik dan masa turun yang sama.

• Pengaruh pada isyarat pembeza

Isyarat terminal fasa positif, isyarat terminal fasa negatif dan isyarat pembeza bagi pasangan talian pembeza dipaparkan dalam Rajah 1 di bawah, di mana garisan penuh mewakili gelombang isyarat pembeza.

Jika penempatan fasa berlaku dari terminal fasa positif ke terminal fasa negatif, akan terdapat perubahan perbezaan antara isyarat terminal fasa positif dan isyarat terminal fasa negatif pada pinggir naik atau turun dan perubahan ini akan berubah selaras dengan perubahan fasa.Trdigunakan untuk mewakili masa yang lebih singkat antara masa naik dan masa turun. Ia boleh menunjukkan bahawa apabila penempatan fasa adalah kurang daripada titik dua bagiTr, herotan isyarat adalah agak kecil dan peningkatan penempatan fasa membawa kepada herotan kuat bentuk gelombang pembezaan. Apabila penempatan fasa melebihiTr, kawasan tidak monotonik akan berlaku pada bentuk gelombang. Di sini kawasan tidak monotonik ialah satu garis lurus. Walau bagaimanapun, bagi isyarat praktikal, disebabkan pantulan, turun naik yang besar mungkin berlaku dalam kawasan tidak monotonik dengan denyut gangguan terbentuk yang membawa kepada pencetus palsu, yang harus dielakkan. Selain itu, pinggir atas bentuk gelombang pembezaan menjadi perlahan dengan peningkatan penempatan fasa, yang mungkin menyebabkan masa penetapan yang tidak mencukupi untuk isyarat data dan mungkin menyebabkan masa pegangan yang tidak mencukupi untuk isyarat jam.

• Pengaruh pada isyarat mod biasa

Penempatan fasa isyarat terminal tunggal tidak akan mempengaruhi bentuk gelombang pembezaan tetapi akan mengubah bentuk gelombang isyarat mod sepunya. Apabila penempatan fasa berlaku pada isyarat terminal positif, perubahan gelombang akan berlaku pada isyarat mod sepunya. Dapat ditunjukkan bahawa julat turun naik berkaitan dengan jumlah penempatan fasa. Apabila jumlah penempatan fasa masing-masing ialah 0.05Tr, 0.1Tr, 0.2Trdan 0.5Tr, julat turun naik mod sepunya masing-masing ialah 5%, 10%, 20% dan 50% daripada julat turun naik asal. Apabila fasa meningkat kepadaTratau lebih, turun naik akan meningkat kepada kira-kira 100% iaitu julat turun naik tertinggi. Perubahan isyarat mod sepunya boleh menyebabkan masalah EMI dan memandangkan isyarat mod sepunya tidak diterima di terminal dalam banyak keadaan, pantulan akan terbentuk di terminal penerima, menyebabkan deringan isyarat. Oleh itu, julat turun naik isyarat mod sepunya harus dikurangkan sebanyak mungkin.

Kesimpulannya, kelewatan relatif yang terlalu besar antara pasangan pembeza boleh menyebabkan pencetusan isyarat palsu, pantulan isyarat, EMI dan masalah penjujukan masa. Walau bagaimanapun, tahap pengaruh isyarat kelewatan relatif bergantung pada faktor skala yang serasi dengan isyaratTr. Apabila faktor skala ialah 0.05, herotan isyarat pembezaan boleh hampir diabaikan. Walau bagaimanapun, bagi isyarat mod sepunya, apabila faktor skala ialah 0.05, turun naik voltan isyarat mod sepunya boleh dikawal pada kira-kira 5%. Kemudian, walaupun dalam keadaan pantulan penuh, voltan pantulan yang bertindan pada talian isyarat hanyalah 10% daripada turun naik asal, yang biasanya merupakan nilai yang boleh diterima. Oleh itu, dalam prosesreka bentuk PCB berkelajuan tinggi, kelewatan relatif talian isyarat pembezaan dalam peraturan penghalaan boleh ditetapkan kepada 0.05Tryang mampu memenuhi keperluan keutuhan isyarat.

Penentuan Kategori Kelewatan Relatif

Berdasarkan analisis di atas, kunci penentuan kategori isometrik pembezaan, iaitu penentuan kelewatan relatif pasangan pembezaan, terletak pada penentuanTrmerujuk kepada nilai terkecil antara masa atas dan bawah bagi isyarat pembezaan. Output masa naik dan masa turun sebenarnya ialah output gabungan impedans dan kapasitans. Oleh itu, masa naik/turun tanpa beban sebenarnya ialah masa naik/turun teras.

Tiga kaedah berikut boleh digunakan untuk mendapatkan nilaiTr:

•Masa naik/turun boleh diperoleh secara langsung daripada manual komponen. Namun begitu, dalam kebanyakan situasi, parameter ini tidak disediakan.

•Nilai bagiTrboleh diperoleh daripada kata kunci Ramp daripada model komponen IBIS (Input/Output Buffer Informational Specification). Parameter masa naik/jatuh di bawah kata kunci Ramp biasanya diukur pada port keluaran yang disambungkan dengan perintang 50Ω, yang biasanya merupakan 20% hingga 80% daripada masa voltan akhir. Oleh kerana parameter diperoleh tanpa mempertimbangkan pengaruh pakej, adalah ketat bagi kita untuk menggunakan masa naik/jatuh sebagai nilaiTr.

•NilaiTrboleh dianggarkan mengikut frekuensi jam minimum atau frekuensi jam maksimum bagi isyarat keluaran. Oleh sebab pinggir naik teragih adalah kira-kira 10% daripada frekuensi jam dalam kebanyakan sistem digital berkelajuan tinggi, nilaiTrboleh dianggarkan dengan tempoh jam minimum Tclk yang diberikan berdasarkan formula:Tr=Tx 10%.

Nilai anggaran yang diperoleh melalui tempoh jam biasanya ketat kerana parameter parasit pakej atau pemuatan komponen akan sangat memperlahankan masa naik/turun semula jadi dalam transistor.

Dalam kerja praktikal, dalam kebanyakan situasi, pereka litar tidak menyediakan maklumat tentangTrkepada jurutera susun atur PCB yang hanya menerima beberapa permintaan samar dari segi kawalan isometrik pembezaan. Kaedah ketiga sudah pasti menyediakan satu skim yang ringkas kepada jurutera susun atur PCB selagi frekuensi jam tertinggi pada talian isyarat diperoleh. Frekuensi jam tertinggi dianggap sebagai parameter reka bentuk yang paling boleh dipercayai bagi pereka litar dan ia biasanya dibekalkan kepada jurutera susun atur PCB pada permulaan reka bentuk PCB.

Kaedah ketiga biasanya menghasilkan senarai nilai rujukan dalam kategori kawalan kelewatan relatif antara pasangan pembezaan, seperti yang ditunjukkan dalam jadual di bawah.

| Frekuensi Jam/ns | Frekuensi Jam/MHz | Kategori Kelewatan Relatif/ps | Panjang Talian Transmisi/mil |

| 3.75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1.25 | 800 | 6.3 | 35 |

Pengesahan Simulasi

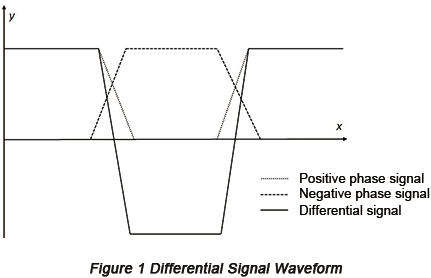

Ambil isyarat pembezaan DQS (Data Strobe) antara TSM320 dan MT41J256M16 sebagai contoh, Cadenceperisian simulasidigunakan untuk menghantar isyarat DOS ke memori DRR3 bagi mensimulasikan cip kawalan memori, menganalisis pengaruhnya terhadap masa penetapan dan pengekalan isyarat data serta mengesahkan analisis di atas. Litar simulasi ditunjukkan dalam Rajah 2 di bawah.

Berdasarkan Rajah 2, voltan rujukan pin keluaran ialah 1.5V; cip kawalan memori disambungkan terus dengan cip memori melalui mod ODT (On-Die Termination) dengan talian penghantaran sepanjang 800mil; impedans berbeza ialah 100Ω dan frekuensi jam simulasi ialah 800MHz. Satu talian penghantaran 50Ω disambung secara siri dengan terminal fasa positif DQS untuk mensimulasikan fenomena ketakselarasan pasangan berbeza. Dalam keadaan pasangan berbeza isometrik, panjang talian penghantaran terminal tunggal 50Ω ialah 0mil.

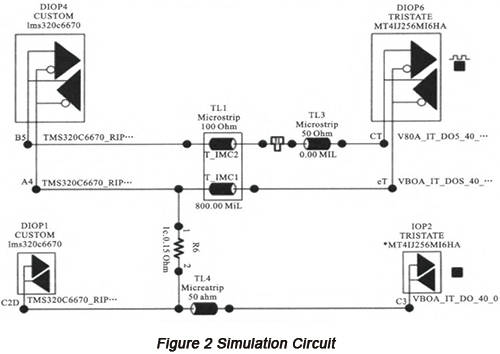

Simulasi dijalankan ke atas litar isometrik pembezaan. Rajah 3 menggambarkan isyarat keluaran pada terminal fasa positif bagi isyarat pembezaan. Melalui pengukuran, masa naik adalah kira-kira 216ps manakala masa turun 219ps jadi masa naik/turun minimumTrsepatutnya 216ps.

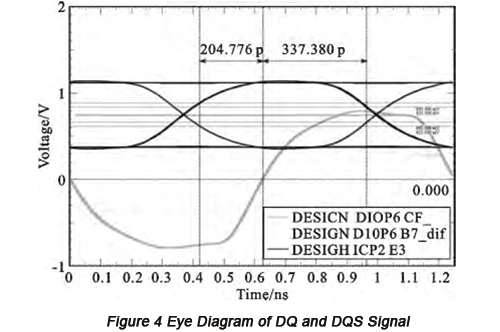

Rajah 4 ialah rajah mata bagi isyarat data DQ dan isyarat penggating DQS melalui simulasi dengan masa penetapan 205ps dan masa pegangan 337ps. Menurut kadar peralihan isyarat DQS dan DQ melalui simulasi dan berdasarkan manual data, masa penetapan minimum isyarat data oleh terminal penerima dikehendaki 85ps dan masa pegangan minimum ialah 95ps. Oleh itu, lebihan ukuran masa penetapan minimum ialah 120ps dan masa pegangan ialah 242ps.

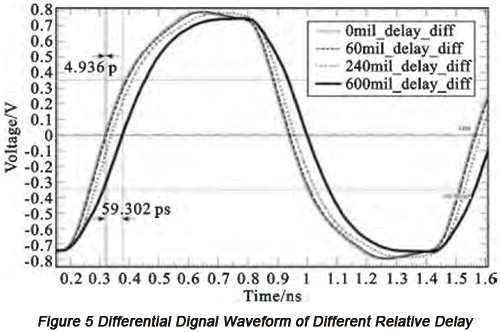

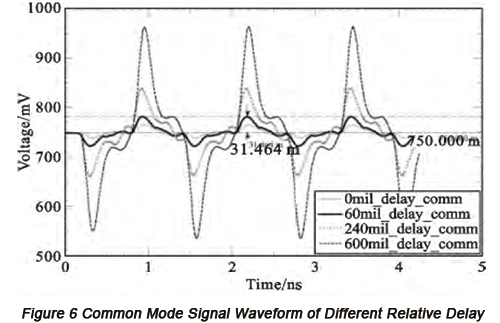

Keadaan kewujudan 0.05Trpenempatan fasa, 0.2Trpenempatan fasa dan 0.5Trpenempatan fasa pada terminal fasa positif perlu dipertimbangkan. Litar boleh disimulasikan dengan panjang talian penghantaran satu terminal yang masing-masing ditetapkan kepada 60mil, 240mil dan 600mil. Bentuk gelombang isyarat pembezaan dan bentuk gelombang isyarat mod sepunya melalui simulasi sebanyak 4 kali ditunjukkan dalam Rajah 5 dan 6.

Berdasarkan Rajah 5, herotan adalah minimum apabila kelewatan relatif ialah 0.05Trdan 0.2Trberlaku. Terutamanya apabila kelewatan relatif ialah 0.05Tr, hanya penempatan kira-kira 5ps daripada isyarat pembezaan kepada bentuk gelombang isyarat pembezaan tanpa kelewatan relatif supaya penubuhan isyarat data berlebihan ukuran meningkat kira-kira 5ps dengan masa pengekalan berlebihan ukuran berkurang sebanyak 5ps. Walaupun masa pengekalan berlebihan ukuran berkurang, jumlah penempatan ini adalah terlalu kecil berbanding masa pengekalan 242ps. Penjujukan masa boleh dielakkan. Untuk keadaan apabila kelewatan relatif ialah 0.5Tr, penempatan bentuk gelombang isyarat DQS telah mencapai kira-kira 60ps. Walaupun penempatan ini masih tergolong dalam kategori ukuran berlebihan, perhatian yang mencukupi harus diberikan.

Berdasarkan Rajah 6, peningkatan penempatan fasa menyebabkan turun naik berkala yang ketara pada gelombang dan peningkatan julat secara beransur-ansur. Apabila kelewatan relatif masing-masing ialah 0.05Tr, 0.2Trdan 0.5Tr, nilai puncak yang diukur bagi isyarat mod sepunya masing-masing ialah 61mV, 176mV dan 430mV, di mana nilai tertinggi adalah tujuh kali ganda daripada yang terendah. Julat turun naik terbesar masing-masing ialah 4.3%, 12% dan 29%.

Kesimpulannya, keputusan simulasi adalah serasi dengan keputusan yang diperoleh melalui analisis rajah fungsi matematik. Apabila kelewatan relatif antara pasangan pembezaan adalah kurang daripada 0.05Tr, pengaruh terhadap isyarat adalah agak kecil.

Tempoh jam minimum bagi isyarat keluaran pada terminal keluaran digunakan untuk menganggar kategori kawalan lengahan relatif. Berdasarkan manual komponen, tempoh jam minimum bagi komponen ialah 1.25ns dengan frekuensi jam 800MHz. Menurut Jadual 1, lengahan relatif perlu dikawal dalam 6.3ps dengan panjang talian penghantaran 35mil. Jelas sekali, nilai ini adalah jauh lebih kecil daripada kategori kawalan lengahan relatif 0.05Trmelalui simulasi. Oleh itu, kategori kawalan kelewatan relatif yang dianggarkan adalah agak konservatif, yang lebih khusus daripada keputusan simulasi.

Sumber yang Berguna

•Penyelidikan mengenai Reka Bentuk PCB Berkelajuan Tinggi dalam Sistem Aplikasi Tertanam

•Cara Mereka Bentuk Sata Imej untuk PCB Kelajuan Tinggi

•Cabaran Reka Bentuk PCB Berkelajuan Tinggi terhadap Keutuhan Isyarat dan Penyelesaiannya

•Simulasi PCB Menggunakan OrCAD PSpice

•Perkhidmatan Pembuatan PCB Ciri Penuh daripada PCBCart - Pelbagai Pilihan Nilai Tambah

•Perkhidmatan Pemasangan PCB Termaju daripada PCBCart - Bermula dari 1 unit