ด้วยการพัฒนาเทคโนโลยีบรรจุภัณฑ์ของชิ้นส่วนอิเล็กทรอนิกส์ไปสู่ความมีขนาดเล็ก น้ำหนักเบา และประสิทธิภาพสูง ทำให้แนวโน้มการพัฒนาของชิ้นส่วนอิเล็กทรอนิกส์มุ่งไปสู่การเพิ่มความหนาแน่นของฟังก์ชันในชิ้นส่วน และการลดระยะห่างระหว่างขั้วอินพุตและขั้วเอาต์พุต ซึ่งแสดงให้เห็นได้ชัดเจนที่สุดโดยเทคโนโลยีการประกอบอัตโนมัติที่มีลักษณะเด่นคือเทคโนโลยีการติดตั้งแบบผิวหน้า (SMT)ในการดำเนินการติดตั้งชิ้นส่วนแบบติดตั้งบนผิวหน้า ขั้นตอนแรกคือการผลิตแผ่นรอง (pad) ที่สอดคล้องกันบนแผ่น PCB เพื่อให้ได้แผ่น PCB ที่มีโครงสร้าง จากนั้นจึงใช้เทคโนโลยีการพิมพ์ผ่านสเตนซิลเพื่อเคลือบครีมประสานบนผิวหน้าของแผ่นรอง PCB สุดท้ายทำการให้ความร้อนเพื่อเปลี่ยนครีมประสานให้กลายเป็นของเหลว ซึ่งจะก่อตัวเป็นสะพานประสานระหว่างขาของชิ้นส่วนกับแผ่นรอง PCB ภายใต้อิทธิพลของซอลเดอร์มาสก์บน PCB ครีมประสานที่หลอมละลายจะถูกจำกัดให้อยู่ในบริเวณแผ่นรองประสานที่สอดคล้องกันเพื่อป้องกันการลัดวงจรระหว่างจุดประสาน ทำให้สามารถประกอบชิปบน PCB ได้โดยอัตโนมัติ ตามประเภทแพ็กเกจที่แตกต่างกัน แผ่นรองประสานทรงกลมและทรงสี่เหลี่ยมจะถูกเลือกใช้เป็นหลัก กล่าวคือBGA (บอลกริดอาร์เรย์)และแพ็คเกจ QFN (quad flat no-lead) หากคุณต้องการทราบข้อมูลเพิ่มเติมเกี่ยวกับ BGA มีเพียงสี่ขั้นตอนก็เพียงพอแล้ว

เมื่อเปรียบเทียบกับคอมโพเนนต์อื่นที่มีแพ็กเกจประเภทต่างกัน แพ็กเกจ QFN ถูกออกแบบมาให้บัดกรีโดยตรงบนแผ่น PCB หรือ FPC โดยสามารถระบายความร้อนได้ดีกว่าเนื่องจากมีแผ่นโลหะเปลือยอยู่ด้านล่าง นอกจากนี้ แพ็กเกจ QFN ยังมีสมรรถนะทางไฟฟ้าที่ยอดเยี่ยมเพราะขาของมันสั้นกว่าคอมโพเนนต์ที่มีแพ็กเกจแบบยื่นออกมา ดังนั้น การออกแบบแผ่นรอง QFN บน PCB จึงมีความสำคัญอย่างยิ่งเพื่อให้สามารถคงไว้และรับประกันความน่าเชื่อถือและสมรรถนะสูงของ PCB ได้

เนื่องจากขนาดของขา QFN และระยะห่างระหว่างขามีขนาดค่อนข้างเล็ก จึงอาจทำให้เกิดสะพานประสานหรือการบัดกรีหลอกได้เนื่องจากปริมาณการพิมพ์ครีมประสานที่ไม่แม่นยำ ดังนั้นจึงควรออกแบบขนาดแผ่นรองของ PCB ให้เหมาะสมโดยอ้างอิงจากความหนาของสเตนซิล (h0) มีประโยชน์อย่างมากต่ออัตราความสำเร็จของการบัดกรี สมมติว่าองศาการเปียกของดีบุกบัดกรีบนแผ่นรองบัดกรี (θa) คือ 30° และมุมเปียกของดีบุกบัดกรีบนซอลเดอร์มาสก์ (θr) มีค่าเท่ากับ 160° หากละเลยความขรุขระของผิวแผ่นรอง มุมการเปียกสามารถถือได้โดยประมาณว่าเป็นมุมรุกหรือมุมถอยของเส้นสัมผัสสามเฟส ตามกระบวนการบัดกรีจริงของชิ้นส่วน QFN การควบคุมเส้นโค้งอุณหภูมิของการบัดกรีรีโฟลว์อย่างเหมาะสม ภายใต้สภาวะอุดมคติที่ดีบัดกรีหลอมละลายอย่างเต็มที่และผิวแผ่นรองถูกทำให้เปียก สามารถทั้งรับประกันประสิทธิภาพการบัดกรีและช่วยให้ชิ้นส่วนไปถึงสภาวะสมดุลการประกอบบัดกรีอัตโนมัติได้ หากแผ่นรองได้รับการออกแบบอย่างเหมาะสม สภาวะอุดมคติของข้อต่อบัดกรีไม่เพียงตอบสนองความต้องการด้านสมรรถนะทางไฟฟ้าของ PCB และการเชื่อมต่อทางกลเท่านั้น แต่ยังหลีกเลี่ยงความล้มเหลวของข้อต่อบัดกรี เช่น การลัดวงจรด้วยดีบัดกรีและการบัดกรีหลอกได้ ดังนั้น สภาวะของข้อต่อบัดกรีจึงต้องเป็นไปตามสมการต่อไปนี้:

a. เมื่อจุดบัดกรีภายใน QFN ถูกกระจายตัวอย่างสมบูรณ์บนแผ่นรอง PCB แล้วθa≤θj(Zยู)≤θr,θj(0)=30°x3(0)=x4(0)=Dx4

b. เมื่อดีบุกนอกตัวถัง QFN กำลังขยายตัวบนแผ่นด้านข้าง

(1)θj(Zu)=θs3+90°θ4(0)=30°θ3(0)=30°

(2)x3(0)=x4(0)=Dx4(0),x3(Zu)=0.

ในสูตรนี้θs3เท่ากับθaซึ่งทั้งสองอย่างเป็นมุมเปียกของดีบุกบัดกรีบนแผ่นรองด้านข้าง

ในทิศทางแนวตั้ง สมการดุลสถิตของของเหลวที่เชื่อมต่อกันคือ:

พdLy(x3(0)-x4(0)+Lx)+ดับเบิลยูz-[ที(x3(0)-x4(0)+Lx)(บาปθ2(0)+ไซน์θ1(0))+TLy(บาปθ3(0)+ไซน์θ4(0))]-ρgV0=0

ความเข้มของความดันที่ด้านล่างของข้อต่อประสาน (Pd) คือ:Pd=ที(x3(0)-x4(0)+Lx)(บาปθ2(0)+ไซน์θ1(0))+TLy(บาปθ3(0)+ไซน์θ4(0))+ρgV0-ดับเบิลยูz]/[Ly(x3(0)-x4(0)+Lx)]

ในสูตรเหล่านี้ρหมายถึงความหนาแน่นของของเหลวของดีบุกบัดกรี; T หมายถึงแรงตึงผิวของของเหลวบริเวณรอยบัดกรี;x3(0) และx4(0) หมายถึงการเลื่อนหลุดของปลายทั้งสองด้านของรอยประสานแบบเหลวที่แผ่นรองบัดกรีด้านล่างθ1(0) และθ2(0) หมายถึงมุมสัมผัสทั้งสองด้านที่เกิดจากผิวระหว่างของเหลว-ก๊าซทั้งสองด้านของรอยบัดกรีและพื้นผิวแผ่นรองด้านล่าง ขณะที่θ3(0) และθ4(0) หมายถึงมุมสัมผัสที่ปลายทั้งสองด้านซึ่งเกิดจากผิวระหว่างของเหลว-ก๊าซทั้งสองด้านV0หมายถึงปริมาณของจุดบัดกรีดับเบิลยูzหมายถึงแรงที่แผ่นรองสัมผัสกดลงบนปลายชิปและจุดเชื่อมประสานในทิศทางตั้งฉาก

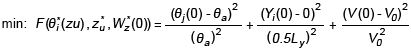

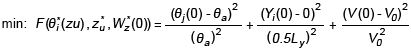

ภายใต้ขอบเขตของสมการ (1) และ (2) เส้นโค้งกรอบของข้อต่อบัดกรีสามารถทำให้เงื่อนไขขอบเขตที่ปลายด้านบนของข้อต่อบัดกรีเทียบเท่ากับเงื่อนไขเริ่มต้นได้ โดยอาศัยวิธีที่มีประสิทธิผลของการหาคำตอบสำหรับปัญหาค่าเริ่มต้น เนื่องจากคำตอบของปัญหาค่าเริ่มต้นไม่สามารถตอบสนองต่อข้อกำหนดที่ว่าzเท่ากับ 0 จะถูกแปลงให้เป็นปัญหาที่เทียบเท่ากันในแง่ของการทำให้ฟังก์ชันวัตถุประสงค์มีค่าน้อยที่สุด ซึ่งแสดงไว้ในสมการ (3)

ฟังก์ชันวัตถุประสงค์ที่ถูกย่อให้เล็กที่สุดนี้สามารถนำมาใช้เพื่อกำหนดขนาดการออกแบบที่เหมาะสมที่สุดของแผ่นรองDx4.

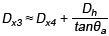

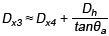

นอกจากนี้ ยังต้องคำนึงถึงลักษณะทางเรขาคณิตของมุมการหุ้มดีบุกของแผ่นรอง PCB ด้วย ในทำนองเดียวกัน ขนาดการขยายของแผ่นรองควรเป็นไปตามสมการด้านล่างประมาณนี้:

ในสมการนี้Dhหมายถึงความหนาของแผ่นรองด้านข้างที่เปิดเผยอยู่นอกชิป ผ่านการปรับให้เหมาะสมของตัวแปรแฝง ทำให้ข้อกำหนดค่าความคลาดเคลื่อนที่คาดหวังเป็นไปตามฟังก์ชันวัตถุประสงค์ และได้ขนาดการออกแบบของแผ่นรองทั้งด้านในและด้านนอกDx4&Dx3) สามารถคำนวณได้โดยมีการตอบสนองความต้องการของค่าด้านล่างสุด

วิธีการนี้ช่วยให้สามารถออกแบบแผ่นรองที่เหมาะสมสำหรับ QFN ได้เป็นอย่างดี เพื่อให้ได้สมรรถนะทางไฟฟ้าสูงทั้งสำหรับชิ้นส่วนนี้และแผงวงจรพิมพ์ (PCB) จากนั้น ด้วยความเป็นมืออาชีพและคุณสมบัติที่ผ่านมาตรฐานความสามารถในการประกอบPCBCart สามารถเปลี่ยนการออกแบบในอุดมคติของคุณให้กลายเป็นความจริงได้