PCB ถูกเพิ่มไปยังตะกร้าสินค้าของคุณเรียบร้อยแล้ว

การประมวลผลไอโซเมตริกแบบเชิงอนุพันธ์และการตรวจสอบด้วยการจำลองสำหรับการออกแบบ PCB ความเร็วสูง

สัญญาณที่ส่งผ่านสายสัญญาณแบบดิฟเฟอเรนเชียลประกอบด้วยองค์ประกอบโหมดดิฟเฟอเรนเชียลและองค์ประกอบโหมดร่วมของสัญญาณ

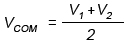

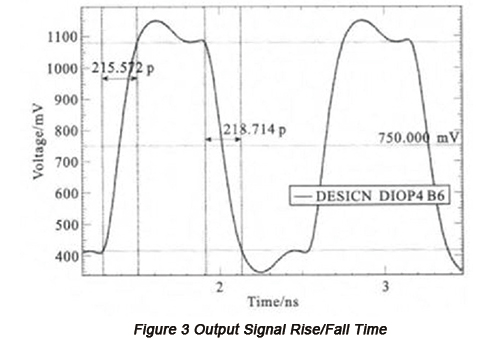

ปริมาณของสัญญาณดิฟเฟอเรนเชียลหมายถึงความแตกต่างระหว่างสัญญาณสองตัวตามสูตรVแตกต่าง=V1-V2ปริมาณของสัญญาณโหมดร่วมหมายถึงครึ่งหนึ่งของผลรวมของสัญญาณสองตัวตามสมการต่อไปนี้ ดังนั้น การเปลี่ยนแปลงของแรงดันไฟฟ้าในสายเดี่ยวจึงส่งผลกระทบต่อสัญญาณโหมดดิฟเฟอเรนเชียลและสัญญาณโหมดคอมมอนพร้อมกันอย่างแน่นอน จากนั้นจึงใช้ซอฟต์แวร์กราฟในการวาดแผนภาพฟังก์ชันทางคณิตศาสตร์เพื่อศึกษาผลกระทบต่อสัญญาณโหมดดิฟเฟอเรนเชียลและสัญญาณโหมดคอมมอนแยกจากกัน เพื่อความสะดวกในการวิจัย สามารถวิเคราะห์สัญญาณได้โดยการจำลองให้เป็นคลื่นรูปสี่เหลี่ยมคางหมูที่มีเวลาเพิ่มขึ้นและเวลาลดลงเท่ากัน

ดังนั้น การเปลี่ยนแปลงของแรงดันไฟฟ้าในสายเดี่ยวจึงส่งผลกระทบต่อสัญญาณโหมดดิฟเฟอเรนเชียลและสัญญาณโหมดคอมมอนพร้อมกันอย่างแน่นอน จากนั้นจึงใช้ซอฟต์แวร์กราฟในการวาดแผนภาพฟังก์ชันทางคณิตศาสตร์เพื่อศึกษาผลกระทบต่อสัญญาณโหมดดิฟเฟอเรนเชียลและสัญญาณโหมดคอมมอนแยกจากกัน เพื่อความสะดวกในการวิจัย สามารถวิเคราะห์สัญญาณได้โดยการจำลองให้เป็นคลื่นรูปสี่เหลี่ยมคางหมูที่มีเวลาเพิ่มขึ้นและเวลาลดลงเท่ากัน

• อิทธิพลต่อสัญญาณดิฟเฟอเรนเชียล

สัญญาณขั้วเฟสบวก สัญญาณขั้วเฟสลบ และสัญญาณดิฟเฟอเรนเชียลของคู่สายดิฟเฟอเรนเชียลจะแสดงดังภาพที่ 1 ด้านล่าง โดยที่เส้นทึบแสดงถึงคลื่นสัญญาณดิฟเฟอเรนเชียล

หากมีการวางเฟสจากขั้วเฟสบวกไปยังขั้วเฟสลบ จะเกิดการเปลี่ยนแปลงของความแตกต่างระหว่างสัญญาณขั้วเฟสบวกและสัญญาณขั้วเฟสลบที่ขอบขาขึ้นหรือขอบขาลง และการเปลี่ยนแปลงนี้จะเปลี่ยนไปตามการเปลี่ยนแปลงของเฟสทีรใช้แทนระยะเวลาที่สั้นกว่าระหว่างเวลาขาขึ้นและเวลาขาลง สามารถระบุได้ว่าเมื่อการจัดวางเฟสมีค่าน้อยกว่าสองในสิบของTrการบิดเบือนสัญญาณมีขนาดค่อนข้างเล็ก และการเพิ่มตำแหน่งเฟสทำให้เกิดการบิดเบือนอย่างรุนแรงของรูปคลื่นเชิงผลต่าง เมื่อการวางตำแหน่งเฟสเกินทีrบริเวณที่ไม่เป็นโมโนโทนิกจะเกิดขึ้นบนรูปคลื่น ที่นี่บริเวณที่ไม่เป็นโมโนโทนิกเป็นเส้นตรง อย่างไรก็ตาม สำหรับสัญญาณในทางปฏิบัติ เนื่องจากการสะท้อน อาจเกิดการขึ้นลงขนาดใหญ่ในบริเวณที่ไม่เป็นโมโนโทนิก พร้อมกับการก่อตัวของพัลส์รบกวนซึ่งนำไปสู่การทริกเกอร์ผิดพลาด ซึ่งควรหลีกเลี่ยง นอกจากนี้ ขอบด้านบนของรูปคลื่นเชิงอนุพันธ์จะช้าลงเมื่อการวางเฟสเพิ่มขึ้น ซึ่งอาจทำให้เวลาการตั้งค่าของสัญญาณข้อมูลไม่เพียงพอ และอาจทำให้เวลาการคงสภาพของสัญญาณนาฬิกาไม่เพียงพอ

• อิทธิพลต่อสัญญาณโหมดร่วม

การจัดวางเฟสของสัญญาณขั้วเดี่ยวจะไม่ส่งผลต่อรูปคลื่นดิฟเฟอเรนเชียล แต่จะเปลี่ยนรูปคลื่นของสัญญาณโหมดร่วม เมื่อมีการจัดวางเฟสที่สัญญาณขั้วบวก การเปลี่ยนแปลงของรูปคลื่นจะเกิดขึ้นกับสัญญาณโหมดร่วม สามารถระบุได้ว่าช่วงของความผันผวนมีความสัมพันธ์กับปริมาณการจัดวางเฟส เมื่อปริมาณการจัดวางเฟสมีค่าเท่ากับ 0.05ทีร, 0.1ทีr, 0.2ทีrและ 0.5ทีรช่วงความผันผวนของโหมดร่วมจะเท่ากับ 5%, 10%, 20% และ 50% ของช่วงความผันผวนเดิมตามลำดับ เมื่อเฟสเพิ่มขึ้นถึงทีrหรือมากกว่านั้น ความผันผวนจะเพิ่มขึ้นเป็นประมาณ 100% ซึ่งเป็นช่วงความผันผวนที่สูงที่สุด การเปลี่ยนแปลงของสัญญาณโหมดร่วมอาจทำให้เกิดปัญหา EMI และเนื่องจากสัญญาณโหมดร่วมมักจะไม่ถูกตรวจรับที่ปลายทางภายใต้เงื่อนไขหลายอย่าง การสะท้อนจะเกิดขึ้นที่ปลายทางรับ ทำให้เกิดการสั่นของสัญญาณ ดังนั้น ช่วงความผันผวนของสัญญาณโหมดร่วมจึงควรถูกลดให้เหลือน้อยที่สุดเท่าที่จะเป็นไปได้

โดยสรุปแล้ว ความหน่วงสัมพัทธ์ที่มากเกินไประหว่างคู่ดิฟเฟอเรนเชียลอาจทำให้เกิดการทริกเกอร์สัญญาณที่ผิดพลาด การสะท้อนสัญญาณ EMI และปัญหาลำดับเวลา อย่างไรก็ตาม ระดับอิทธิพลของสัญญาณความหน่วงสัมพัทธ์นั้นขึ้นอยู่กับปัจจัยสเกลที่สอดคล้องกับสัญญาณTrเมื่อปัจจัยสเกลเท่ากับ 0.05 การบิดเบือนของสัญญาณดิฟเฟอเรนเชียลสามารถมองข้ามได้เกือบทั้งหมด อย่างไรก็ตาม สำหรับสัญญาณโหมดร่วม เมื่อปัจจัยสเกลเท่ากับ 0.05 การแปรผันของแรงดันไฟฟ้าของสัญญาณโหมดร่วมสามารถควบคุมให้อยู่ที่ประมาณ 5% จากนั้น แม้ในกรณีที่เกิดการสะท้อนเต็มที่ แรงดันสะท้อนที่ซ้อนทับบนสายสัญญาณจะมีค่าเพียง 10% ของการแปรผันเดิม ซึ่งโดยทั่วไปถือว่าเป็นค่าที่ยอมรับได้ ดังนั้น ในกระบวนการของการออกแบบแผงวงจรพิมพ์ความเร็วสูงในกฎระเบียบการเดินสาย สามารถตั้งค่าความหน่วงสัมพัทธ์ของสายสัญญาณดิฟเฟอเรนเชียลให้เป็น 0.05ทีrซึ่งสามารถตอบสนองความต้องการด้านความสมบูรณ์ของสัญญาณ

การกำหนดประเภทของความล่าช้าเชิงสัมพัทธ์

จากการวิเคราะห์ข้างต้น กุญแจสำคัญในการกำหนดหมวดหมู่ไอโซเมตริกเชิงอนุพันธ์ กล่าวคือ การกำหนดค่าหน่วงสัมพัทธ์ของคู่ดิฟเฟอเรนเชียล อยู่ที่การกำหนดTrหมายถึงค่าที่เล็กที่สุดระหว่างเวลาสูงและเวลาต่ำของสัญญาณดิฟเฟอเรนเชียล เอาต์พุตของเวลาเพิ่มขึ้น (rise time) และเวลาลดลง (fall time) แท้จริงแล้วเป็นผลลัพธ์จากการผสมผสานกันของอิมพีแดนซ์และค่าคาปาซิแตนซ์ ดังนั้น เวลาเพิ่มขึ้น/เวลาลดลงที่ไม่มีโหลดจึงเป็นเวลาเพิ่มขึ้น/เวลาลดลงที่มีอยู่โดยเนื้อแท้

สามารถใช้สามวิธีต่อไปนี้เพื่อหาค่าของทีr:

•เวลาเพิ่มขึ้น/ลดลงสามารถหาได้โดยตรงจากคู่มือของอุปกรณ์ อย่างไรก็ตาม ในสถานการณ์ส่วนใหญ่จะไม่มีการระบุพารามิเตอร์นี้ไว้

•มูลค่าTรสามารถได้มาจากคีย์เวิร์ด Ramp ในโมเดล IBIS (Input/Output Buffer Informational Specification) ของคอมโพเนนต์ พารามิเตอร์เวลาเพิ่มขึ้น/ลดลงภายใต้คีย์เวิร์ด Ramp โดยทั่วไปจะถูกวัดที่พอร์ตเอาต์พุตซึ่งต่อกับตัวต้านทาน 50Ω ซึ่งมักจะเป็นช่วงเวลา 20% ถึง 80% ของแรงดันไฟฟ้าสุดท้าย เนื่องจากพารามิเตอร์เหล่านี้ได้มาโดยไม่คำนึงถึงอิทธิพลของแพ็กเกจ จึงเข้มงวดสำหรับเราที่จะใช้เวลาเพิ่มขึ้น/ลดลงเป็นค่าทีร.

•มูลค่าของทีrสามารถประมาณค่าได้ตามความถี่สัญญาณนาฬิกาต่ำสุดหรือความถี่สัญญาณนาฬิกาสูงสุดของสัญญาณเอาต์พุต เนื่องจากขอบขาขึ้นแบบกระจายมีค่าประมาณ 10% ของความถี่สัญญาณนาฬิกาในระบบดิจิทัลความเร็วสูงส่วนใหญ่ ค่าทีrสามารถประมาณค่าได้ด้วยคาบสัญญาณนาฬิกาขั้นต่ำ Tclk ที่กำหนด โดยอิงตามสูตร:ทีร=Tคลิกx 10%

ค่าประมาณที่ได้จากคาบสัญญาณนาฬิกามักจะเข้มงวด เนื่องจากพารามิเตอร์寄生ของแพ็กเกจหรือโหลดของอุปกรณ์ต่าง ๆ จะทำให้เวลาเพิ่มขึ้น/ลดลงโดยธรรมชาติในทรานซิสเตอร์ช้าลงอย่างมาก

ในการทำงานจริง ในสถานการณ์ส่วนใหญ่ นักออกแบบวงจรจะไม่ให้ข้อมูลเกี่ยวกับTรถึงวิศวกรออกแบบเลย์เอาต์ PCB ที่ได้รับเพียงข้อกำหนดที่คลุมเครือเกี่ยวกับการควบคุมไอโซเมตริกของสัญญาณดิฟเฟอเรนเชียล วิธีที่สามนี้มอบแนวทางที่เรียบง่ายให้กับวิศวกรออกแบบเลย์เอาต์ PCB อย่างไม่ต้องสงสัย ตราบใดที่สามารถทราบความถี่สัญญาณนาฬิกาสูงสุดบนสายสัญญาณได้ ความถี่สัญญาณนาฬิกาสูงสุดถือเป็นพารามิเตอร์การออกแบบที่น่าเชื่อถือที่สุดสำหรับผู้ออกแบบวงจร และโดยทั่วไปจะถูกส่งมอบให้กับวิศวกรออกแบบเลย์เอาต์ PCB ตั้งแต่เริ่มต้นการออกแบบ PCB

วิธีที่สามมักจะนำไปสู่รายการค่ามาตรฐานภายในหมวดการควบคุมความหน่วงสัมพัทธ์ระหว่างคู่ดิฟเฟอเรนเชียล ดังแสดงในตารางด้านล่าง

| ความถี่สัญญาณนาฬิกา/ns | ความถี่สัญญาณนาฬิกา/เมกะเฮิรตซ์ | หมวดความหน่วงสัมพัทธ์/พิโควินาที | ความยาวสายส่ง/มิล |

| 3.75 | 266 | 18.8 | ๑๐๕ |

| 3 | 333 | 15 | 84 |

| 2.5 | ๔๐๐ | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1.25 | 800 | 6.3 | 35 |

การตรวจสอบการจำลอง

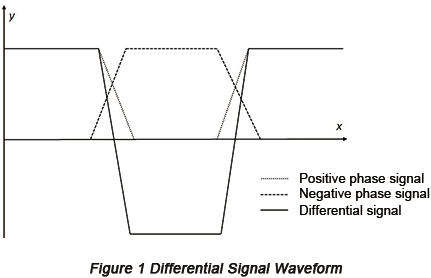

ยกตัวอย่างสัญญาณดิฟเฟอเรนเชียล DQS (Data Strobe) ระหว่าง TSM320 และ MT41J256M16, Cadenceซอฟต์แวร์จำลองถูกนำมาใช้เพื่อส่งสัญญาณ DOS ไปยังหน่วยความจำ DRR3 เพื่อจำลองชิปควบคุมหน่วยความจำ วิเคราะห์ผลกระทบต่อเวลาเซตอัปและโฮลด์ของสัญญาณข้อมูล และยืนยันการวิเคราะห์ข้างต้น วงจรจำลองแสดงดังในรูปที่ 2 ด้านล่าง

จากรูปที่ 2 แรงดันอ้างอิงของขาเอาต์พุตคือ 1.5V; ชิปควบคุมหน่วยความจำเชื่อมต่อโดยตรงกับชิปหน่วยความจำผ่านโหมด ODT (On-Die Termination) ด้วยสายส่งความยาว 800 mil; ค่าความต้านทานเชิงผลต่างเท่ากับ 100Ω และความถี่สัญญาณนาฬิกาจำลองเท่ากับ 800MHz มีการต่อสายส่ง 50Ω อนุกรมกับขั้วเฟสบวกของสัญญาณ DQS เพื่อจำลองปรากฏการณ์ความคลาดเคลื่อนของคู่สายเชิงผลต่าง ในกรณีที่เป็นคู่สายเชิงผลต่างที่มีความยาวเท่ากัน ความยาวของสายส่งแบบขั้วเดี่ยว 50Ω จะเท่ากับ 0 mil

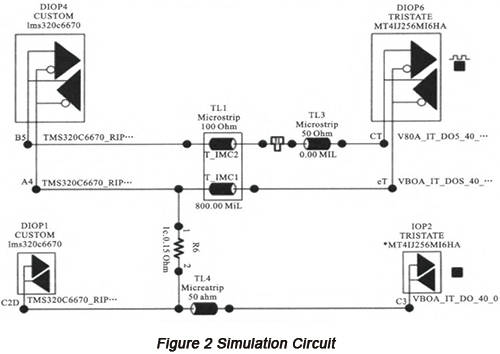

มีการจำลองวงจรไอโซเมตริกแบบดิฟเฟอเรนเชียล รูปที่ 3 แสดงสัญญาณเอาต์พุตที่ขั้วเฟสบวกของสัญญาณดิฟเฟอเรนเชียล จากการวัดพบว่าเวลาขาขึ้นประมาณ 216ps ในขณะที่เวลาขาลง 219ps ดังนั้นเวลาเพิ่มขึ้น/ลดลงขั้นต่ำทีรควรเป็น 216ps.

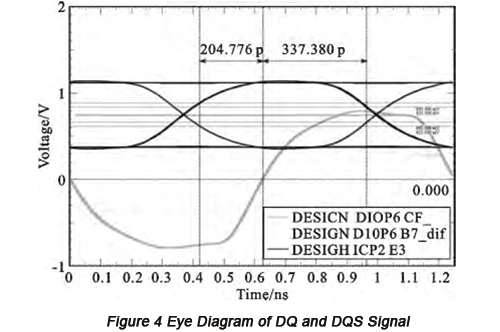

รูปที่ 4 เป็นไดอะแกรมตา (eye diagram) ของสัญญาณข้อมูล DQ และสัญญาณเกต DQS จากการจำลอง โดยมีเวลาเซตตัว (establishment time) 205ps และเวลาโฮลด์ (holding time) 337ps ตามอัตราการเปลี่ยนสถานะของสัญญาณ DQS และ DQ จากการจำลองและจากคู่มือข้อมูล เวลาตั้งตัวขั้นต่ำของสัญญาณข้อมูลที่ขั้วรับต้องการคือ 85ps และเวลาโฮลด์ขั้นต่ำคือ 95ps ดังนั้น ค่าความเผื่อของเวลาตั้งตัวขั้นต่ำคือ 120ps และของเวลาโฮลด์คือ 242ps

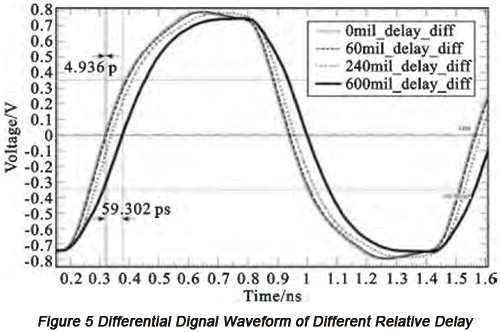

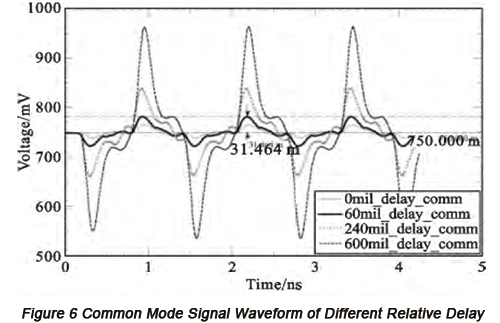

สถานการณ์ของการมีอยู่ของ 0.05ทีrการจัดวางเฟส 0.2ทีrการจัดวางเฟสและ 0.5Tรต้องพิจารณาการวางเฟสที่ขั้วเฟสบวก วงจรสามารถจำลองได้โดยใช้ความยาวสายส่งแบบขั้วเดียวที่ตั้งค่าไว้เป็น 60 mil, 240 mil และ 600 mil ตามลำดับ รูปคลื่นสัญญาณดิฟเฟอเรนเชียลและรูปคลื่นสัญญาณโหมดร่วมจากการจำลองจำนวน 4 ครั้งแสดงไว้ในรูปที่ 5 และรูปที่ 6

จากรูปที่ 5 การบิดเบือนมีค่าน้อยที่สุดเมื่อค่าหน่วงสัมพัทธ์เท่ากับ 0.05Tรและ 0.2ทีรเกิดขึ้น โดยเฉพาะอย่างยิ่งเมื่อความล่าช้าเชิงสัมพัทธ์เท่ากับ 0.05ทีรโดยมีการจัดวางเพียงประมาณ 5ps จากสัญญาณดิฟเฟอเรนเชียลไปยังรูปคลื่นสัญญาณดิฟเฟอเรนเชียลโดยไม่มีดีเลย์สัมพัทธ์ ทำให้เวลาการสร้างสัญญาณข้อมูลที่เกินค่ามาตรฐานเพิ่มขึ้นประมาณ 5ps ในขณะที่เวลาโฮลด์ที่เกินค่ามาตรฐานลดลง 5ps แม้ว่าเวลาโฮลด์ที่เกินค่ามาตรฐานจะลดลง แต่ปริมาณการจัดวางนี้มีค่าน้อยมากเมื่อเทียบกับเวลาโฮลด์ 242ps จึงสามารถหลีกเลี่ยงการจัดลำดับเวลาได้ สำหรับสถานการณ์ที่ดีเลย์สัมพัทธ์เท่ากับ 0.5Trตำแหน่งของรูปคลื่นสัญญาณ DQS ได้ถึงประมาณ 60ps แล้ว แม้ว่าตำแหน่งนี้ยังคงอยู่ในหมวดของการวัดเกิน แต่ก็ควรให้ความสนใจอย่างเพียงพอ

จากรูปที่ 6 การเพิ่มขึ้นของการจัดวางเฟสทำให้เกิดการแปรผันแบบเป็นคาบอย่างชัดเจนบนคลื่นและการเพิ่มขึ้นของระยะอย่างค่อยเป็นค่อยไป เมื่อค่าหน่วงเวลาเชิงสัมพัทธ์มีค่าเท่ากับ 0.05Tr, 0.2ทีรและ 0.5ทีrค่าพีคที่วัดได้ของสัญญาณโหมดร่วมมีค่าเท่ากับ 61mV, 176mV และ 430mV ตามลำดับ โดยค่าที่สูงที่สุดมีค่ามากกว่าค่าที่ต่ำที่สุดถึงเจ็ดเท่า ช่วงความผันผวนสูงสุดมีค่าเท่ากับ 4.3%, 12% และ 29% ตามลำดับ

โดยสรุปแล้ว ผลการจำลองมีความสอดคล้องกับผลลัพธ์ที่ได้จากการวิเคราะห์แผนภาพฟังก์ชันทางคณิตศาสตร์ เมื่อค่าหน่วงเวลาเชิงสัมพัทธ์ระหว่างคู่ดิฟเฟอเรนเชียลมีค่าน้อยกว่า 0.05Tรอิทธิพลต่อสัญญาณค่อนข้างน้อย

คาบสัญญาณนาฬิกาต่ำสุดของสัญญาณเอาต์พุตที่ขั้วเอาต์พุตถูกนำมาใช้เพื่อประเมินหมวดการควบคุมดีเลย์สัมพัทธ์ ตามคู่มือของคอมโพเนนต์ คาบสัญญาณนาฬิกาต่ำสุดของคอมโพเนนต์คือ 1.25ns ที่ความถี่นาฬิกา 800MHz ตามตารางที่ 1 ดีเลย์สัมพัทธ์ควรถูกควบคุมให้อยู่ภายใน 6.3ps โดยมีความยาวของสายส่งเท่ากับ 35mil เห็นได้ชัดว่าค่านี้มีขนาดเล็กกว่าหมวดการควบคุมของดีเลย์สัมพัทธ์ที่ 0.05 อย่างมากTrผ่านการจำลอง ดังนั้น หมวดการควบคุมความล่าช้าเชิงสัมพัทธ์ที่ประเมินไว้จึงมีลักษณะค่อนข้างอนุรักษ์นิยม ซึ่งมีความเฉพาะเจาะจงมากกว่าผลการจำลอง

แหล่งข้อมูลที่เป็นประโยชน์

•การวิจัยการออกแบบ PCB ความเร็วสูงในระบบประยุกต์แบบฝังตัว

•วิธีออกแบบระนาบอิมเมจสำหรับแผงวงจรพิมพ์ความเร็วสูง

•ความท้าทายด้านความถูกต้องของสัญญาณในการออกแบบแผงวงจรพิมพ์ความเร็วสูงและแนวทางแก้ไข

•การจำลองแผงวงจรพิมพ์ด้วย OrCAD PSpice

•บริการผลิตแผงวงจรพิมพ์ (PCB) แบบครบทุกฟังก์ชันจาก PCBCart - ตัวเลือกเสริมเพิ่มมูลค่าหลากหลาย

•บริการประกอบแผงวงจรพิมพ์ขั้นสูงจาก PCBCart - เริ่มต้นเพียง 1 ชิ้น