ด้วยการพัฒนาที่กำลังจะมาถึงของวิทยาศาสตร์และเทคโนโลยีอิเล็กทรอนิกส์ ระบบอิเล็กทรอนิกส์ที่ประกอบด้วยชิป IC กำลังพัฒนาอย่างรวดเร็วไปสู่ขนาดใหญ่ การย่อส่วน และความเร็วสูง ในขณะเดียวกัน ก็เกิดปัญหาตามมาว่าการย่อขนาดของระบบอิเล็กทรอนิกส์ทำให้ความหนาแน่นของการเดินสายวงจรเพิ่มขึ้น ในขณะที่ความถี่สัญญาณเพิ่มขึ้นอย่างต่อเนื่อง และเวลาการเปลี่ยนสถานะขอบสัญญาณสั้นลง เมื่อค่าหน่วงของการเชื่อมต่อสัญญาณมากกว่าเวลาการเปลี่ยนสถานะของสัญญาณ 10% สายสัญญาณบนบอร์ดจะแสดงลักษณะของสายส่ง ทำให้ปัญหาต่าง ๆ เช่น การสะท้อนสัญญาณและการครอสทอล์กเด่นชัดมากขึ้น การเกิดขึ้นของปัญหาความเร็วสูงได้นำมาซึ่งความท้าทายที่ยิ่งใหญ่ต่อการออกแบบฮาร์ดแวร์ และหากการออกแบบบางอย่างที่ถือว่าถูกต้องในมุมมองของลอจิกไม่ได้รับการจัดการอย่างเหมาะสม การออกแบบทั้งหมดอาจล้มเหลว ดังนั้น วิธีการแก้ปัญหาของวงจรความเร็วสูงจึงกลายเป็นหนึ่งในปัจจัยสำคัญที่กำหนดความสำเร็จของระบบ

หลักการของการสะท้อนและอิทธิพลของมัน

• หลักการของการสะท้อน

สาเหตุโดยตรงของการสะท้อนอยู่ที่ความไม่เข้ากันของอิมพีแดนซ์ของสายส่ง ซึ่งทำให้พลังงานสัญญาณไม่ถูกดูดซับอย่างสมบูรณ์ที่ปลายทาง ปัญหาการสะท้อนสะท้อนให้เห็นถึงคุณภาพสัญญาณของเครือข่ายเดี่ยว ซึ่งเกี่ยวข้องกับคุณสมบัติทางกายภาพของเส้นทางสัญญาณของเครือข่ายเดี่ยวและเส้นทางย้อนกลับ โดยปกติ คุณสมบัติทางกายภาพของการเดินลายวงจร PCBมีอิทธิพลอย่างมากต่อสายส่ง โดยหลัก ๆ แล้วรวมถึงวัสดุของลายวงจร ความกว้างของลายวงจร ความหนาของลายวงจร ระยะห่างระหว่างลายวงจรอื่น ๆ กับระนาบ และค่าคงที่ไดอิเล็กทริกของวัสดุที่อยู่ติดกัน เมื่อสัญญาณถูกส่งผ่านไปตามเครือข่ายเดี่ยว จะเกิดการเปลี่ยนแปลงอิมพีแดนซ์ชั่วขณะของสายเชื่อมต่อขึ้น หากอิมพีแดนซ์ของสายเชื่อมต่อที่สัญญาณรับรู้คงที่อยู่ตลอด จะคงสภาพไร้ความเพี้ยนไว้ได้ หากอิมพีแดนซ์ของสายเชื่อมต่อที่สัญญาณรับรู้มีการเปลี่ยนแปลง จะเกิดความเพี้ยนพร้อมกับการสะท้อนที่จุดซึ่งมีการเปลี่ยนแปลง สัญญาณสะท้อนจะถูกส่งกลับไปยังด้านส่งของสัญญาณและจะสะท้อนกลับไปกลับมาซ้ำอีก จนกว่าจะลดขนาดลงตามการลดลงของพลังงาน ในที่สุด แรงดันและกระแสของสัญญาณจะเข้าสู่สภาวะคงที่

• การคำนวณการสะท้อน

เมื่อสัญญาณถูกส่งไปข้างหน้าตามสายส่ง จะเกิดอิมพีแดนซ์ชั่วขณะขึ้นได้ตลอดเวลา หากอิมพีแดนซ์ที่สัญญาณรับรู้มีค่าคงที่ สัญญาณจะถูกส่งต่อไปข้างหน้าได้ตามปกติ ตราบใดที่อิมพีแดนซ์ที่รับรู้มีการเปลี่ยนแปลง ไม่ว่าสาเหตุใดก็ตาม จะทำให้เกิดการสะท้อนเสมอ ดัชนีสำคัญที่ใช้วัดปริมาณการสะท้อนคือสัมประสิทธิ์การสะท้อน ซึ่งแสดงถึงอัตราส่วนระหว่างแรงดันไฟฟ้าสะท้อนกับแรงดันไฟฟ้าของสัญญาณเดิม สัมประสิทธิ์การสะท้อนสามารถนิยามได้ตามสมการ .

.

ในสูตรนี้ Z1หมายถึงอิมพีแดนซ์หลังการเปลี่ยนแปลง ในขณะที่ Z0อิมพีแดนซ์ก่อนการเปลี่ยนแปลง สมมติว่าอิมพีแดนซ์ลักษณะของการเดินลายบน PCB คือ 50Ω ในกระบวนการส่งสัญญาณ พบตัวต้านทานค่า 150Ω จากนั้นค่าสัมประสิทธิ์การสะท้อนจะเท่ากับ (150-50)/(150+50)=1/2 (ในกรณีนี้ ไม่ได้พิจารณาอิทธิพลของความจุ寄生และความเหนี่ยวนำ寄生 โดยถือว่าตัวต้านทานเป็นตัวต้านทานเชิงอุดมคติบริสุทธิ์) ผลลัพธ์นี้บ่งชี้ว่าพลังงานครึ่งหนึ่งของสัญญาณเดิมถูกสะท้อนกลับไปยังขั้วต้นทาง หากแรงดันของสัญญาณส่งเท่ากับ 5V แรงดันสะท้อนจะเท่ากับ 2.5V

• อิทธิพลของการสะท้อน

1). การบิดเบือนสัญญาณที่เกิดจากการสะท้อน

หากสายสัญญาณไม่ได้รับการเทอร์มิเนตอย่างถูกต้อง พัลส์สัญญาณจากด้านขับจะสะท้อนกลับที่ขั้วรับ เมื่อสัญญาณสะท้อนมีความแรงมาก รูปคลื่นที่ซ้อนกันอาจเปลี่ยนสภาวะลอจิกซึ่งนำไปสู่ผลกระทบที่ไม่คาดคิด ทำให้เกิดการบิดเบือนของรูปทรงสัญญาณ เมื่อการบิดเบือนเห็นได้ชัดเจนมากขึ้น ก็อาจทำให้เกิดข้อผิดพลาดจำนวนมากและทำให้การออกแบบล้มเหลว ในขณะเดียวกัน สัญญาณที่มีการบิดเบือนจะมีความไวต่อสัญญาณรบกวนมากขึ้น ซึ่งจะทำให้การออกแบบล้มเหลวได้เช่นกัน

2). การเกินเป้าหมายและต่ำกว่าเป้าหมายที่เกิดจากการสะท้อน

โอเวอร์ชูตหมายถึงค่าพีคแรกหรือค่าหุบแรกที่เกินกว่าระดับแรงดันไฟฟ้า สำหรับขอบขาขึ้น หมายถึงค่าพีคแรกที่สูงกว่าระดับแรงดันไฟฟ้าสูงสุด ในขณะที่สำหรับขอบขาลง หมายถึงค่าหุบแรกที่ต่ำกว่าระดับแรงดันไฟฟ้าต่ำสุด การเกิดโอเวอร์ชูตมากเกินไปอาจทำให้ไดโอดป้องกันเสียหาย ส่งผลให้เกิดความล้มเหลวของอุปกรณ์ก่อนเวลาอันควร อันเดอร์ชูตหมายถึงค่าหุบถัดไปหรือค่าพีคถัดไปที่อาจสร้างสัญญาณนาฬิกาเทียม ทำให้ระบบอ่านและเขียนข้อมูลผิดพลาด

3). การสั่น

การสั่นเป็นอาการที่เกิดจากการสะท้อนเช่นกัน ด้วยคุณสมบัติเดียวกับการโอเวอร์ชูต การโอเวอร์ชูตและอันเดอร์ชูตซ้ำ ๆ ภายในหนึ่งรอบสัญญาณนาฬิกาเรียกว่าการสั่น ซึ่งเป็นผลมาจากพลังงานส่วนเกินที่เกิดจากการสะท้อน ไม่สามารถถูกดูดซับได้ทันเวลาในวงจร

วิธีการลดการสะท้อน

องค์ประกอบหลักที่ทำให้เกิดการสะท้อนประกอบด้วย รูปร่างเรขาคณิตของการเดินสาย (ความกว้าง ความยาว มุมของการเลี้ยว) การเปลี่ยนระดับชั้นของการเดินสายเครือข่ายเดียวกัน การส่งผ่านผ่านคอนเน็กเตอร์ ความไม่ต่อเนื่องระหว่างเพาเวอร์และกราวด์ โครงสร้างทอพอโลยีที่ไม่ถูกต้อง และความไม่เข้ากันของปลายเครือข่าย วิธีการหลักในการลดการสะท้อนจะถูกนำเสนอในส่วนถัดไป

• การเพิ่มระดับความถี่ของระบบ

อัตราการเปลี่ยนผ่านของขอบสัญญาณจะถูกลดลงในสถานการณ์ที่เป็นไปได้ เพื่อให้การสะท้อนของสายส่งเข้าสู่สภาวะคงตัวก่อนที่สัญญาณจะเชื่อมต่อกับสายส่ง ด้านหนึ่งต้องเป็นไปตามข้อกำหนดด้านการออกแบบ อีกด้านหนึ่งควรเลือกใช้คอมโพเนนต์ที่มีความเร็วต่ำเพื่อหลีกเลี่ยงการปะปนกันระหว่างสัญญาณประเภทต่าง ๆ

• การเพิ่มประสิทธิภาพการประมวลผลสัญญาณ

เนื่องจากมีข้อกำหนดที่เข้มงวดในด้านลำดับเวลา จึงจำเป็นต้องกำหนดส่วนประกอบและโหนดที่อาจก่อให้เกิดปัญหาความเร็วสูงล่วงหน้า ต้องปรับข้อกำหนดต่าง ๆ ที่เกี่ยวข้องกับการจัดวางส่วนประกอบและการเดินสาย และในที่สุดจะมีการควบคุมดัชนีการออกแบบด้านความสมบูรณ์ของสัญญาณ วิธีการประมวลผลหลักประกอบด้วย:

1).ค่อนข้างบางแผงวงจรพิมพ์ถูกนำมาใช้เพื่อลดพารามิเตอร์寄生ของรูทะลุ

2).ควรจัดจำนวนชั้นให้เหมาะสม โดยควรใช้ชั้นกลางให้เต็มที่ในการตั้งชิลด์เพื่อให้การกราวด์ที่อยู่ติดกันทำได้ดียิ่งขึ้น ซึ่งจะช่วยลดค่าความเหนี่ยวนำ寄生ได้อย่างมีประสิทธิภาพ ทำให้ความยาวการส่งสัญญาณสั้นลง และเพิ่มการครอสทอล์กระหว่างสัญญาณอย่างมาก

3).ควรควบคุมรูปทรงเรขาคณิตของลายสัญญาณบน PCB โดยลดจำนวนมุมหักเลี้ยวและลดจุดไม่ต่อเนื่องของอิมพีแดนซ์บนเส้นทางเดินสัญญาณให้เหลือน้อยที่สุด โดยเฉพาะอย่างยิ่งสำหรับการเดินลายในวงจรความถี่สูง ควรใช้เส้นตรงให้มากที่สุด เมื่อจำเป็นต้องมีมุมหักเลี้ยว สามารถใช้เส้นหักเป็นมุมหรือส่วนโค้ง 45° ซึ่งจะช่วยลดการแผ่รังสีภายนอกของสัญญาณความถี่สูงและการคัปปลิงระหว่างสัญญาณความถี่สูง

4).ควรจัดวางการเดินสายสัญญาณสำคัญให้อยู่ในระนาบเดียวกันเพื่อลดการใช้รูทะลุที่ไม่จำเป็น

5).ควรรับประกันความสมบูรณ์ของระนาบเพื่อให้มีเส้นทางการไหลกลับที่มีอิมพีแดนซ์ต่ำสำหรับสายสัญญาณ โดยมีจุดมุ่งหมายเพื่อลดการคัปปลิงอิมพีแดนซ์โหมดร่วมและสัญญาณรบกวนจากการสวิตช์โหมดร่วม เพื่อลดหรือขจัดปัญหาความสมบูรณ์ของสัญญาณที่เกี่ยวข้องกับระบบจ่ายไฟ

6).การประยุกต์ใช้โครงสร้างเชิงทอพอโลยีของการกำหนดเส้นทางที่ถูกต้อง

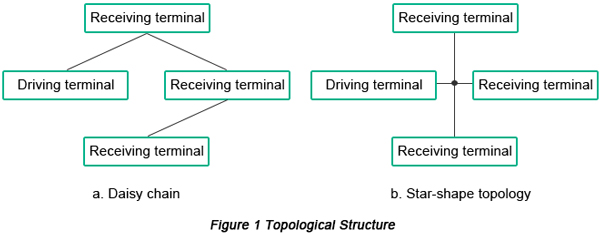

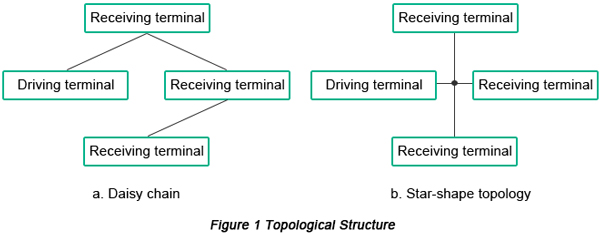

โครงสร้างเชิงทอพอโลยีของการเดินสายสัญญาณ หมายถึง ลำดับการเดินสายและโครงสร้างของเส้นสัญญาณ ในวงจรใช้งานจริง มักมีกรณีที่แหล่งขับสัญญาณเพียงตัวเดียวขับโหลดหลายตัว และแหล่งขับสัญญาณกับโหลดเหล่านั้นสอดคล้องกับโครงสร้างทอพอโลยี โครงสร้างทอพอโลยีที่แตกต่างกันจะส่งผลต่อสัญญาณแตกต่างกันอย่างชัดเจน โดยทั่วไป โครงสร้างทอพอโลยีพื้นฐานสองแบบที่ใช้ในการเดินสายบนแผ่น PCB คือ โครงสร้างแบบเดซี่เชน (daisy chain) และโครงสร้างแบบดาว (star-shape topology) ดังแสดงในรูปที่ 1 ด้านล่าง

a. เดซี่เชน

การเดินสายเริ่มต้นจากเทอร์มินัลขับสัญญาณและไปยังแต่ละเทอร์มินัลรับสัญญาณตามลำดับ หากมีการใช้ตัวต้านทานอนุกรมเพื่อเปลี่ยนคุณสมบัติของสัญญาณ ตำแหน่งของตัวต้านทานอนุกรมควรอยู่ใกล้กับเทอร์มินัลขับสัญญาณให้มากที่สุด ในแง่ของการควบคุมสัญญาณรบกวนฮาร์มอนิกระดับสูง การเดินสายแบบเดซี่เชนให้ผลการเดินสายที่ดีที่สุด อย่างไรก็ตาม การเดินสายประเภทนี้มีความสามารถในการเดินสายต่ำที่สุด น้อยกว่า 100% ในการออกแบบจริง ความยาวของกิ่งสายในเดซี่เชนควรสั้นให้มากที่สุด พื้นที่การเดินสายของโครงสร้างทอพอโลยีนี้มีขนาดเล็ก และสามารถใช้ตัวต้านทานเพียงตัวเดียวเพื่อให้รองรับการเทอร์มิเนชันได้ นอกจากนี้ โครงสร้างการเดินสายประเภทนี้ยังทำให้การรับสัญญาณที่เทอร์มินัลรับสัญญาณต่าง ๆ ไม่พร้อมเพรียงกัน

b. โทโพโลยีแบบดาว

การกำหนดเส้นทางประเภทนี้สามารถหลีกเลี่ยงการไม่ซิงโครไนซ์ของสัญญาณนาฬิกาได้อย่างมีประสิทธิภาพ แต่มีข้อเสียคือแต่ละแขนงจำเป็นต้องใช้ตัวต้านทานปลายสาย ค่าแรงต้านของตัวต้านทานปลายสายควรสอดคล้องกับอิมพีแดนซ์ลักษณะของสายส่ง สำหรับระบบที่สัญญาณต่าง ๆ มีความต้องการมาถึงที่ขั้วรับพร้อมกัน โทโพโลยีแบบดาวเป็นรูปแบบที่เหมาะสมที่สุด

• วิธีการยุติ

ควรรักษาค่าความต้านทานลักษณะเฉพาะบนเส้นทางการส่งสัญญาณให้คงที่ กล่าวคือ ค่าสัมประสิทธิ์การสะท้อนต้องเป็น 0 ซึ่งหมายความว่าไม่มีการสะท้อนบนเส้นทางการส่งสัญญาณ สถานการณ์นี้เรียกว่าความเข้ากันได้ของอิมพีแดนซ์ ในขณะนี้สัญญาณจะส่งจากกราวด์อุดมคติไปยังปลายทาง โดยทั่วไป ความยาวของสายส่งควรสอดคล้องกับเงื่อนไข .

.

ในอสมการนี้ L หมายถึงความยาวของสายส่งตรหมายถึงเวลาที่เพิ่มขึ้นของสัญญาณขั้วต้นทางtpd1หมายถึงความล่าช้าในการส่งผ่านโหลดต่อความยาวหนึ่งหน่วยบนสายส่ง เมื่อการส่งผ่านระดับสัญญาณแบบบูรณาการเกิดขึ้นก่อนที่สัญญาณสะท้อนจะมาถึงปลายทางไกล จำเป็นต้องใช้เทคโนโลยีการแมตช์ที่ปลายสาย หลักการต่อปลายสายของสายส่งได้แก่: หากสัมประสิทธิ์การสะท้อนของโหลดหรือสัมประสิทธิ์การสะท้อนของแหล่งจ่ายเป็นศูนย์ การสะท้อนจะถูกกำจัด โดยทั่วไปมีสองกลยุทธ์ที่ใช้กันคือ ทำให้ความต้านทานแหล่งจ่ายเข้ากันได้กับความต้านทานของสายส่ง ซึ่งเรียกว่าการเทอร์มิเนตที่ต้นทาง และทำให้ความต้านทานโหลดเข้ากันได้กับความต้านทานของสายส่ง ซึ่งเรียกว่าการเทอร์มิเนตที่ปลายทาง

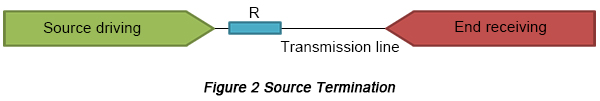

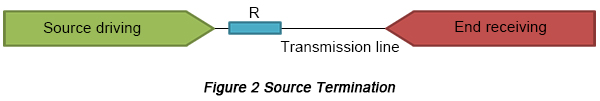

1). การยุติแหล่งที่มา

การปิดปลายทางที่ต้นทาง (Source termination) ส่วนใหญ่เป็นวิธีการปิดปลายแบบอนุกรม โดยการต่อรีซิสเตอร์แบบอนุกรมเข้าไปในสายส่ง ณ ตำแหน่งที่อยู่ใกล้กับด้านต้นทาง ค่ารีซิสเตอร์อนุกรมรวมกับความต้านทานของขั้วขับต้องเท่ากับค่าความต้านทานของสายส่ง หลักการของการปิดปลายแบบอนุกรมในการกำจัดแรงดันสะท้อนจากด้านโหลด คือการหยุดการสะท้อนครั้งที่สองของสายส่ง ดังแสดงในรูปที่ 2

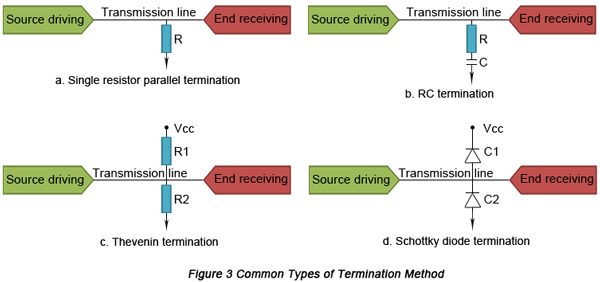

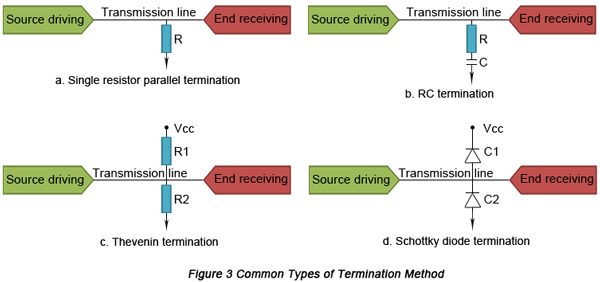

2). การสิ้นสุดปลายสาย

หลักการสำคัญของการปิดปลายสัญญาณ (end termination) คือการเพิ่มตัวต้านทานแบบดึงขึ้น (pull-up) หรือดึงลง (pull-down) ที่ตำแหน่งใกล้กับขั้วโหลดเพื่อให้เกิดการแมตช์อิมพีแดนซ์ การปิดปลายสัญญาณโดยทั่วไปสามารถแบ่งออกเป็น การปิดปลายแบบตัวต้านทานเดี่ยวขนาน (single resistor parallel termination), การปิดปลายแบบ RC (RC termination), การปิดปลายแบบเธเวนิน (Thevenin termination) และการปิดปลายแบบไดโอดชอตกี (Schottky diode termination) ดังแสดงในรูปที่ 3

ค่าความต้านทานในการปิดปลายแบบขนานด้วยตัวต้านทานตัวเดียวจะเท่ากับอิมพีแดนซ์ของสายส่ง ค่าในตัวต้านทานสองตัวของการปิดปลายแบบเธเวนินควรเป็นไปตามสูตร:Z0=R1อ2/(R1+R2)ค่าความจุไฟฟ้าในเทอร์มิเนชัน RC เป็นไปตามสูตร:C=3T/Z0ซึ่งทีหมายถึงเวลาขาขึ้นของสัญญาณ ในขณะที่ Z0หมายถึงอิมพีแดนซ์ของสายส่ง

จากมุมมองด้านการออกแบบระบบ ควรเลือกใช้การปิดปลายแบบขนานเป็นอันดับแรก เนื่องจากสามารถลดสัญญาณรบกวน EMI และ RFI ได้มากที่สุดเมื่อเทียบกับวิธีการปิดปลายอีกสามแบบ ตามสภาพการใช้งานจริงจึงเลือกใช้วิธีการปิดปลายที่เหมาะสม และเมื่อจำเป็นควรทำการออกแบบด้วยการจำลองระบบ

บทสรุป

ในการออกแบบแผงวงจรพิมพ์ความเร็วสูงข้อกำหนดเบื้องต้นที่ประสบความสำเร็จ ได้แก่ การจัดวางและการวางเส้นทางที่เหมาะสม การหลีกเลี่ยงการเลี้ยวและการใช้ via ทะลุที่ไม่จำเป็น ความต่อเนื่องของอิมพีแดนซ์ ระนาบอ้างอิงสัญญาณแบบบูรณาการ และการต่อลงกราวด์ที่ยอดเยี่ยม เพื่อเพิ่มประสิทธิภาพการออกแบบและความสมบูรณ์ของสัญญาณ และให้ได้มาซึ่งความเข้ากันได้ทางแม่เหล็กไฟฟ้าที่สูงขึ้น ควรดำเนินการตรวจสอบการจำลองการออกแบบ ซึ่งช่วยให้นักออกแบบสามารถจัดการกับข้อบกพร่องในการออกแบบได้ทันท่วงที และชดเชยข้อบกพร่องในการออกแบบ PCB

แหล่งข้อมูลที่เป็นประโยชน์

•เคล็ดลับการออกแบบความเร็วสูง

•ความท้าทายด้านความถูกต้องของสัญญาณในการออกแบบแผงวงจรพิมพ์ความเร็วสูงและแนวทางแก้ไข

•การวิเคราะห์ความถูกต้องของสัญญาณและการออกแบบ PCB บนวงจรผสมดิจิทัล-อนาล็อกความเร็วสูง

•บริการผลิตแผงวงจรพิมพ์ (PCB) แบบครบวงจรจาก PCBCart - ตัวเลือกเสริมที่เพิ่มมูลค่าหลากหลาย

•บริการประกอบแผงวงจรขั้นสูงจาก PCBCart - เริ่มต้นเพียง 1 ชิ้น

.

.

.

.