In high‑speed electronics, multi‑layer PCBs deliver greater density, better signal integrity, and stronger performance for complex applications. Yet their compact routing, tightly stacked layers, and high‑frequency signals also raise serious electromagnetic interference (EMI) risks. Uncontrolled EMI degrades signal quality, creates crosstalk, triggers system instability, and leads to failure in EMC compliance tests such as FCC, CE, or CISPR. Reducing EMI is not an optional extra—it is a core requirement for reliable, certifiable, and market‑ready designs.

This article presents practical, engineering‑proven methods to minimize EMI in multi‑layer PCB layouts, covering layer stacking, grounding, routing, filtering, shielding, and validation. By following these guidelines, you can build layouts that control radiation, contain noise, and maintain stable performance in real‑world electromagnetic environments.

Understand EMI Basics in Multi-Layer PCBs

Electromagnetic interference (EMI) describes unwanted electromagnetic energy that disrupts circuit operation. Electromagnetic compatibility (EMC) means a device functions properly in its environment without producing unacceptable interference to other equipment. In multi‑layer boards, EMI often arises from:

High‑speed signals with fast edge rates that generate strong high‑frequency harmonics

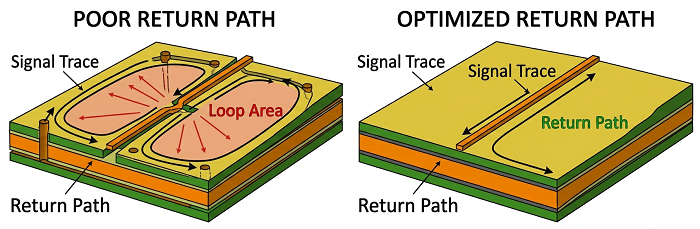

Large current loops formed by poor signal return paths

Crosstalk between closely spaced parallel traces

Unstable power distribution and noise on power rails

Improper grounding that creates radiating loops

Floating conductors, unused pins, or long cables that act as antennas

EMI propagates in two main ways: through radiation (air‑borne coupling) and conduction (along wires or cables). Effective EMI reduction targets both paths at the layout stage.

Optimize Layer Stack‑Up for Low EMI

Layer stack‑up is the foundation of EMI control in multi‑layer PCBs. A well‑designed stack‑up shortens return paths, contains electric and magnetic fields, and reduces noise coupling between layers.

Use Continuous Reference Planes

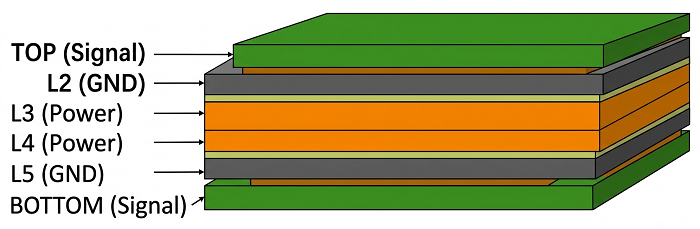

Every signal layer should have an adjacent ground or power plane to provide a low‑inductance return path. This structure confines electromagnetic fields and drastically reduces radiation.

For a 4‑layer board, recommended stack‑up: Signal → GND → Power → Signal

For a 6‑layer board, recommended stack‑up: Signal → GND → Power → Power → GND → Signal

Solid, unbroken planes are far better than split or fragmented planes. Avoid gaps, slots, or excessive voids in ground and power layers, as these force return currents to detour and increase loop area.

Pair Power and Ground Planes Closely

Place power planes directly adjacent to ground planes with thin dielectric spacing—ideally less than 0.254 mm (10 mil). This forms a natural, high‑frequency decoupling capacitor that stabilizes voltage, lowers impedance, and suppresses noise across a broad frequency range.

Avoid Isolated Signal Layers

Never place a signal layer between two other signal layers without an intervening ground plane. Such “isolated” signal layers suffer severe crosstalk and poor field containment, raising EMI significantly.

Master Grounding Strategies

Grounding is the single most effective way to control EMI. Poor grounding creates loops, common‑impedance noise, and radiating structures.

Use Multi‑Point Grounding for High Frequencies

For circuits above 1 MHz, multi‑point grounding to a continuous ground plane is superior. It lowers impedance at high frequencies and prevents large ground loops. Low‑frequency circuits may use single‑point grounding to avoid circulating currents.

Add Ground Stitching Vias

Use multiple ground vias near signal vias that switch layers. These “stitching vias” maintain a continuous return path, prevent field leakage at layer transitions, and stabilize impedance. For high‑speed designs, keep ground via spacing below 12.7 mm (0.5 inch).

Eliminate Ground Loops

Design return paths to be short, direct, and overlap with signal paths. Large ground loops act as loop antennas that radiate strongly. Keep high‑speed traces and their return paths tightly coupled.

Control Routing to Minimize Crosstalk and Radiation

Trace routing directly affects EMI. Careful routing reduces coupling, shortens antennas, and preserves signal integrity.

Follow the 3W Rule

Maintain trace spacing of at least three times the trace width. This reduces capacitive and inductive crosstalk between adjacent traces. For noise‑sensitive or high‑speed signals, use wider spacing.

Route Critical Signals on Inner Layers

Route clocks, high‑speed data lanes, and noisy signals on inner layers sandwiched between ground planes. This stripline structure provides excellent shielding and contains EM fields.

Avoid Routing Near Board Edges

Traces near board edges radiate more strongly and are more vulnerable to external interference. Keep high‑speed traces at least one dielectric thickness away from the edge.

Use Differential Pairs

For critical high‑speed interfaces, use tightly coupled, length‑matched differential pairs. They cancel common‑mode noise, reduce radiation, and improve immunity.

Reduce Trace Length

Shorter traces mean smaller antennas and lower radiation. Minimize the length of clock lines, oscillator traces, and fast‑edge signals.

Use Decoupling and Filtering Effectively

Decoupling capacitors and EMI filters suppress noise at its source before it spreads across the board or radiates outward.

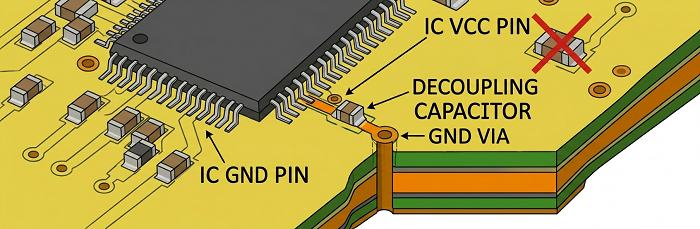

Place Decoupling Capacitors Close to ICs

Mount high‑frequency capacitors (such as 0.1 μF) within 2.54 mm (100 mil) of IC power pins. Use short, wide traces or direct via connections to minimize parasitic inductance. Combine small capacitors for high frequencies and larger bulk capacitors for low‑frequency stabilization.

Apply Ferrite Beads and Filters

Place ferrite beads at power inputs to attenuate high‑frequency noise while passing DC. For I/O ports and power lines, add π‑filters or LC filters to block conducted EMI and prevent cables from becoming radiating antennas.

Shielding and Component Placement

Strategic shielding and component placement separate noise sources from sensitive circuits.

Separate Noisy and Sensitive Circuits

Place switching regulators, clocks, and RF circuits away from analog circuits, sensors, and low‑level receivers. Use ground planes or guard traces to create isolation barriers.

Use Component‑Level Shielding

Cover oscillators, RF modules, and switching circuits with metal shielding cans. Ensure shields connect securely to the ground plane with multiple vias to form a continuous Faraday cage.

Guard Rings and Ground Fills

Surround sensitive or noisy traces with grounded guard rings. Use ground copper pours on outer layers and stitch them to internal ground planes to enhance containment. Avoid floating copper fills—they can worsen EMI.

PCB Material Selection

Material properties influence high‑frequency performance and EMI.

Choose laminates with stable dielectric constant (Dk) to preserve impedance control.

Use thinner dielectrics between power and ground to increase capacitance and reduce noise.

For very high‑speed designs, consider low‑loss materials to reduce signal attenuation and radiation.

Validate EMI Performance

Even the best layout requires verification.

Perform pre‑compliance testing with near‑field probes to detect hotspots during prototyping.

Conduct formal EMC tests in accredited labs for radiated emissions, conducted emissions, and immunity.

Iterate the layout based on test results to fix resonance, radiation, or coupling issues.

Common Mistakes to Avoid

Ignoring signal return paths and allowing large loops

Splitting ground planes unnecessarily

Placing decoupling capacitors too far from ICs

Routing high‑speed signals parallel for long distances

Leaving unused pins, test points, or traces floating

Delaying EMI testing until the final design stage

Conclusion

Reducing EMI in multi‑layer PCB layouts requires systematic planning across stack‑up, grounding, routing, filtering, and shielding. When implemented early in the design cycle, these methods significantly improve EMC, reduce rework, and speed up certification.

For professional, high‑reliability multi‑layer PCBs built with EMI‑optimized design and manufacturing standards, choose a partner with deep experience in electromagnetic compatibility and high‑performance fabrication.

PCBCart specializes in advanced multi‑layer PCB manufacturing with full support for low‑EMI layout practices, high‑quality materials, and strict process control. Whether you are developing consumer electronics, industrial equipment, or high‑speed digital systems, PCBCart delivers boards that combine performance, reliability, and compliance. With PCBCart, you can turn your EMI‑optimized layout into a production‑ready PCB that performs consistently in real‑world environments.

Helpful Resources

• Ensuring First-Time Success in PCB EMC Design

• High-Speed Layout Tips

• Strategies to the Design of Crosstalk between Two Parallel Micro-strip Lines on PCB

• High-Speed PCB Design Challenges on Signal Integrity and Their Solutions