Gegenwärtig führt die rasante Entwicklung der Internettechnologie zu einer umfassenden Nutzung von E-Mail, Online-Zahlungen und persönlicher Kommunikation. Vor diesem Hintergrund ist Informationssicherheit zu einem zentralen Forschungsthema auf der ganzen Welt geworden. Die PKI-Technologie (Public Key Infrastructure) bietet Sicherheitsdienste durch den Einsatz der Theorie und Technologie öffentlicher Schlüssel. Die PCIE-Technologie (Peripheral Component Interface Express) hat als dritte Generation des I/O-Bus-Standards, der serielle Datenübertragung und Punkt-zu-Punkt-Verschaltung einsetzt, breite Anwendung in Hochgeschwindigkeitsgeräten gefunden. Im Bereich des digitalen Systementwurfs führt eine relativ hohe Taktfrequenz zu Problemen in Bezug auf Signalintegrität, Stromversorgungsintegrität und Übersprechen, und herkömmliches PCB-Design kann die Anforderungen an die Systemstabilität nicht mehr erfüllen.

Dieser Artikel bietet ein PCB-Designschema für eine Hochgeschwindigkeits-Passwortkarte auf Basis von PCIe unter Ausnutzung der Vorteile der hochgeschwindigen seriellen PCIe-Übertragung.

Gesamtkonzept

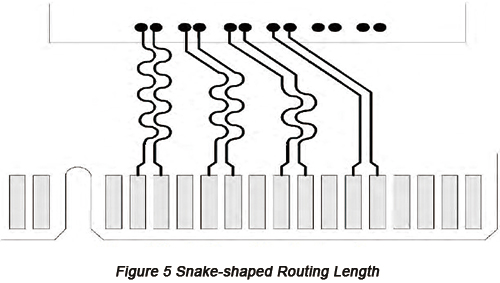

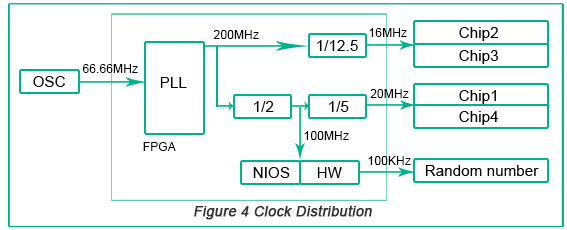

Der FPGA-Chip EP4CGX50CF23C6N aus der Cyclone-IV-GX‑Serie von Altera wird in diesem Design eingesetzt. Er integriert ein PCIE-IP-Hardcore-Modul und realisiert das Design einer Passwortkarte für vier Hochgeschwindigkeits-Datenübertragungen. Vier Chiptypen – Chip 1, Chip 2, Chip 3 und Chip 4 – können jeweils die Algorithmen SM1, SM2/SM3, SM4 und SSF33 implementieren und die Funktionen der Initialisierung der Passwortkarte, der Verwaltung von geheimen Schlüsseln, der Sicherung und Wiederherstellung sowie des Berechtigungsmanagements ausführen. Passwortkarten werden in PCs eingesetzt, über den PCIE-Steckplatz mit dem Mainboard im PC verbunden und vom PC gesteuert. Das IP-Hardcore im FPGA wird zur Implementierung von PCIE verwendet, wodurch die Kommunikation zwischen dem PCIE-Kern, dem SRAM-Cache und dem Steuerungsmodul ermöglicht wird. Als Steuerzentrum implementiert NiosII die Softwarefunktion der Passwortkarte. Gleichzeitig realisiert ein zusätzlicher Passwortchip die Kommunikation zwischen den einzelnen Schnittstellenmodulen und der Passwortkarte. Die Hardwarestruktur der Passwortkarte ist in Abbildung 1 unten dargestellt.

Hochgeschwindigkeits‑PCB-Design

• Stackup und Layout

Das Stackup-Design ist das wichtigste Problem, das berücksichtigt werden muss, und ein vernünftiges Stackup-Design kann die EMI‑Strahlung (elektromagnetische Störung) unterdrücken, die transiente Spannung auf der Stromversorgungs- oder Masseebene so gering wie möglich halten und das elektromagnetische Feld von Signal und Versorgung abschirmen. Im Allgemeinen werden bei der Hochgeschwindigkeits-Digitalschaltungsentwicklung mehrlagige Leiterplatten und mehrere Versorgungsspannungen eingesetzt.PCB-Stacking-Designwird auf der Grundlage umfassender Elemente implementiert, einschließlich der Taktfrequenz der Schaltung,Herstellungskosten für Leiterplatten, Pin-Dichte, Fertigungszeitraum und Zuverlässigkeit. Außerdem sollten die Lagen einer Multilayer-Platine symmetrisch aufgebaut sein und die Gesamtzahl der Lagen sollte eine gerade Zahl sein, da ein asymmetrisches Stapeldesign zu Verzug der Leiterplatte führt. Die in diesem Artikel entworfene Passwortkarte wird über den PCIE-Steckplatz mit dem PC verbunden, und die Größe und Form der Leiterplatte ist festgelegt, mit einer Höhe von etwa 67 mm und einer Länge von etwa 174 mm, wobei sich am unteren Rand die PCIE-X4-Schnittstellenpins befinden. Aufgrund der hohen Bauteildichte und der dichten Leiterführung wird die Anzahl der PCB-Lagen auf 6 festgelegt, mit der Verteilung Signallage, Versorgungslage, Signallage, Versorgungslage, Masse-Lage, Signallage. Dieses Design umfasst 3 Signallagen, 1 Masse-Lage und 2 Versorgungslagen und stellt damit die für die Signalintegrität erforderliche Umgebung bereit.

Nach der Festlegung des PCB-Stackings sollten die Bauteilgruppen und das Layout umgesetzt werden. Zunächst muss die Position der Bauteile entsprechend den Abmessungen und dem Muster der Leiterplatte festgelegt werden, wobei Leitungsverbindungen, funktionale Aufteilung sowie Ordnung und Ästhetik zwischen den Bauteilen zu berücksichtigen sind. Anschließend müssen die Bauteile entsprechend den unterschiedlichen Spannungsstufen der Bauteile sinnvoll verteilt werden, um Spannungsleitungen so kurz wie möglich zu halten, was die Störeinflüsse von Netzrauschen verringern und die Stabilität der Stromversorgung erhöhen kann. Bei der Platzierung von Chips ist auf das Verhältnis zwischen deren Hilfsschaltung und dem Chip selbst sowie auf die Platzierung des Quarzoszillators hinter den Taktpins zu achten. Hochrauschende Bauteile sollten nicht in der Nähe des Quarzoszillators platziert werden und sollten sich in der Nähe ihrer Treiberbauteile befinden. Darüber hinaus muss bei der Platzierung der Versorgungs- und Signalpins jedes Chips deren Positionierung berücksichtigt und ihre Lage und Ausrichtung anhand der angeschlossenen Leitungen angepasst werden. Da das Längen-Breiten-Verhältnis der Passwortkarte größer als 2:1 ist und die Positionen des PCIE-Steckplatzes, der Befestigungslöcher und der Anzeige-LED festgelegt sind, muss bei der Bauteilanordnung zunächst die Platzierung der festen Bauteile berücksichtigt werden. Außerdem sollte aufgrund der großen Anzahl von Verbindungsleitungen zwischen Bauteilen und FPGA die Bauteilanordnung mit dem FPGA als Zentrum vor der Festlegung der Positionen anderer Bauteile erfolgen, sodass der Platz auf der Ober- und Unterseite der Leiterplatte effektiv genutzt werden kann, um ausreichend Abstand zwischen den Bauteilen sowie zwischen Bauteilen und Positionierungslöchern zu gewährleisten.

• Leistungsdesign

InHochgeschwindigkeits-Leiterplattendesign, das Design des Stromversorgungssystems steht in direktem Zusammenhang mit dem Erfolg des gesamten Systems. Das durch Stromversorgung und Masse erzeugte Rauschen sollte auf ein Minimum reduziert werden, um die Zuverlässigkeit der Produkte sicherzustellen. Die Anwendung eines Stromverteilungsschemas in Form von Lagen bedeutet, dass die Versorgung über das Metall auf der gesamten Lage verteilt wird, wodurch die Versorgungsimpedanz und das Rauschen verringert und die Zuverlässigkeit erhöht werden. Da bei Leiterplatten mehrere Versorgungsspannungen berücksichtigt werden müssen, sollte ein Mehrfach-Stromversorgungslagen-Design angewendet werden, das in der Lage ist, die Kopplungsstörung durch gemeinsame Impedanz als Rauschschleife zu eliminieren. Der Einsatz von Entkopplungskapazitäten kann das Problem der Stromversorgungsintegrität lösen, da Kondensatoren nur auf der Unter- oder Oberseite der Leiterplatte platziert werden können; auf dieser Grundlage sollten die Leitungen, die die Entkopplungskondensatoren verbinden, kurz und breit sein. Entsprechend dem Chipmaterial kann der durch die Versorgungsleitungen fließende Strom berechnet und die Leiterbahnbreite bestimmt werden. Je breiter die Leiterbahnen sind, desto mehr Strom können sie führen. Die experimentelle Formel lautet wie folgt:W(Zeilenbreite: mm) ≥L(mm/A) xIch(aktuell: A)

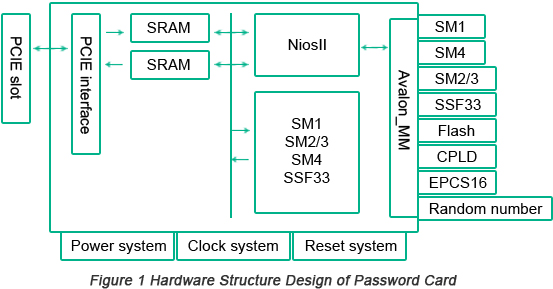

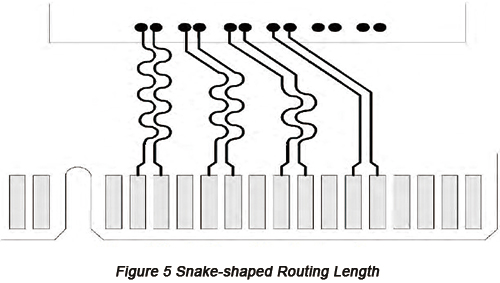

Mehrere Spannungen auf der Leiterplatte (PCB) beziehen eine oder zwei Arten von Versorgungsspannungen über die Backplane vom Netzteil, die anschließend in weitere für die Bauteile benötigte Spannungen umgewandelt werden. Die Spannungswandlung ist in zwei Architekturen unterteilt: zentrale Stromversorgungsarchitektur und verteilte Stromversorgungsarchitektur. Erstere bedeutet, dass die Versorgung von einer unabhängigen Stromquelle bereitgestellt und dann in alle benötigten Spannungen umgewandelt wird, während letztere eine mehrstufige Spannungswandlung bezeichnet. Da die zentrale Stromversorgungsarchitektur Nachteile wie hohe Kosten und großen Leiterplattenbedarf aufweist, wird in diesem Design die verteilte Stromversorgungsarchitektur eingesetzt. Die Kryptografiekarte verwendet 6 Spannungen, darunter 12 V, 3,3 V, 5 V, 2,5 V, 1,2 V und 1,8 V. Dieses Design beginnt mit der Nutzung der 3,3-V- und 12-V-Versorgung im PCIE-Steckplatz; anschließend kann die 3,3-V-Spannung über einen Spannungswandlungs-Chip 5 V und 1,8 V erzeugen, um das Steckmodul und Chip 3 zu versorgen. Danach wird die 12-V-Spannung in 2,5 V umgewandelt, um FPGA und Chip 4 zu versorgen. Schließlich wird die 2,5-V-Spannung in 1,2 V umgewandelt, um FPGA und Chip 2 zu versorgen. Die verteilte Stromversorgungsarchitektur der Kryptografiekarte ist in Abbildung 2 unten dargestellt.

• Durchsteckmontage-Design

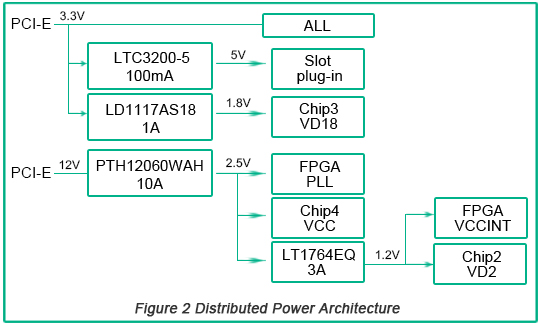

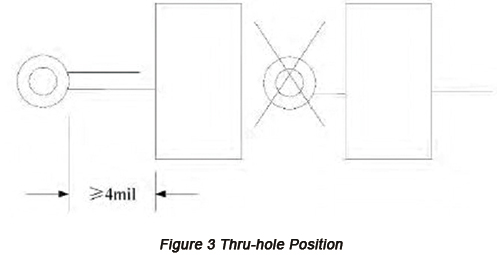

Im Prozess der Gestaltung des Layouts fürmehrlagige LeiterplattenBei hoher Dichte sollten Durchkontaktierungen eingesetzt werden, um Signale von einer Lage zur anderen zu übertragen und so die elektrische Verbindung zwischen den Lagen bereitzustellen. Das Positionsdesign der Durchkontaktierungen muss mit großer Sorgfalt erfolgen. Durchkontaktierungen dürfen nicht auf Pads platziert werden, und für die Verbindung kann eine einzelne Leiterbahn verwendet werden, da es sonst zu Problemen wie Tombstone-Effekt und unzureichender Lötung kommt. Auf das Pad der Durchkontaktierung muss Lötstoppmaske mit einem Abstand von 4 mil aufgebracht werden, und Durchkontaktierungen dürfen nicht im Zentrum des Pads von Chip-Bauteilen auf der Lötseite platziert werden. Die Position der Durchkontaktierungen ist in Abbildung 3 unten dargestellt.

Außerdem darf die Position der Durchkontaktierungen nicht zu nah an den Goldfingern liegen, deren Steckseite eine Fase aufweisen sollte. Damit Leiterplatten in den PCIe-Steckplatz eingesteckt werden können, kann an den beiden Seitenkanten der Steckkarte eine Fase von (1–1,5)×45° vorgesehen werden.

• Hochgeschwindigkeits-Signalführung

Im Routing-Prozess muss die Verteilung sinnvoll angepasst werden, um die Anzahl der Verbindungsleitungen zu minimieren und dadurch Übersprechen zu reduzieren. Beim Routing von Hochgeschwindigkeits-Digitalsignalen sollte die Signalleitungsebene in der Nähe von Mehrfachstromversorgungsebenen weit von der Leistungsreferenzfläche entfernt sein, um die Entstehung eines Rückpfads durch den Signalstrom zu vermeiden.

Da die Taktfrequenz von Hochgeschwindigkeitsschaltungen relativ hoch ist, beeinflussen Jitter, Drift und Verzerrungen das System stark, sodass beim Hochgeschwindigkeits‑PCB‑Design eine geringe Signalwellenstörung erforderlich ist. Daher sollten das Problem der Taktverteilung und das Routing zuerst berücksichtigt werden. Das Routing von Hochgeschwindigkeits‑Taktsignalen muss umgesetzt werden, und die Leitungsführung der Haupttaktsignalleitungen muss so kurz wie möglich, geradlinig und frei von Durchkontaktierungen und Stromversorgungsanteilen sein, um Übersprechen zwischen Takt und Versorgung zu verhindern. Wenn mehrere Takte mit unterschiedlichen Frequenzen auf derselben Leiterplatte verwendet werden, dürfen zwei Taktleitungen mit unterschiedlichen Frequenzen nicht parallel geführt werden. Für mehrere Bauteile, die Taktsignale mit derselben Frequenz verwenden, kann das Netz jedoch in Spinnen‑, Baum‑ oder Verzweigungstopologie verteilt werden.

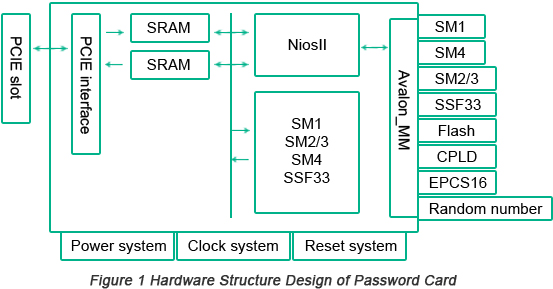

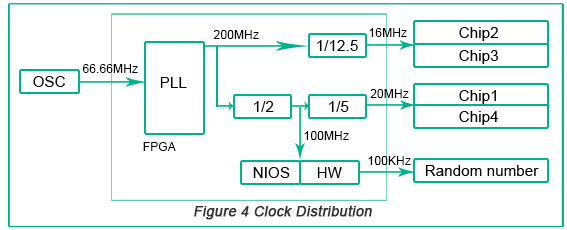

Auf der hochgeschwindigen kryptographischen Karte erhält das FPGA einen 66,66‑MHz‑Takt über den Quarzoszillator auf der Leiterplatte. Nach einer Schleifenführung über die internen PLLs im FPGA wird ein 200‑MHz‑Basistakt erzeugt, der als Schnittstelle für Chip 2 und Chip 3 zur Taktbereitstellung dient. Anschließend wird ein 100‑MHz‑Takt über die interne Frequenzteilerschaltung bereitgestellt, der als Arbeitstakt für den NiosII‑Softcore und die Hardware‑Schaltung im FPGA verwendet wird. Die geteilte Frequenz von 16 MHz ist der Arbeitstakt für Chip 2 und Chip 3, während die geteilte Frequenz von 20 MHz der Arbeitstakt für Chip 1 und Chip 4 ist. Die Taktverteilung ist in Abbildung 4 unten dargestellt.

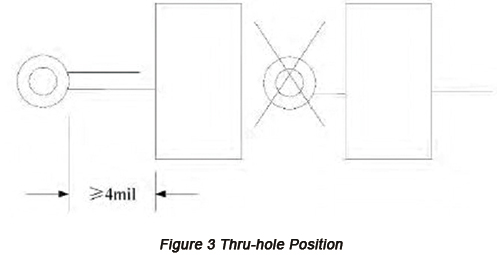

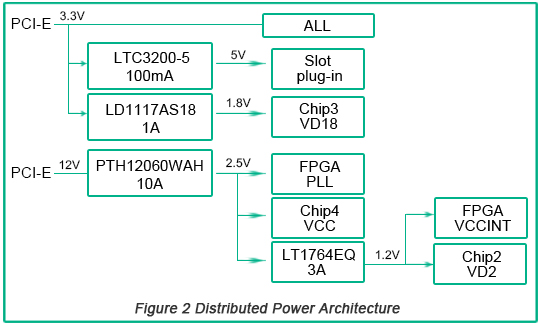

Die Hochgeschwindigkeits-Signalübertragung zwischen dem PCIE-Steckplatz und dem PC wird durch die Hochgeschwindigkeits-Kryptografiekarte mittels differentieller Leiterbahnen realisiert, um Probleme hinsichtlich der Signalintegrität zu vermeiden. Allgemein gesprochen werden zwischen differentiellen Signalleitungen keine Masseleitungen platziert, da sonst der Kopplungseffekt zwischen den differentiellen Signalen zerstört würde. Nach der Führung der differentiellen Signalleitungen wird um die Hochgeschwindigkeitssignale der Leiterplatte Kupfer platziert, wobei der verbleibende freie Raum vollständig mit Masseleitungen gefüllt wird, um die EMV-Festigkeit der Schaltung zu erhöhen. Der Schlüssel vonLeiterplattenroutingbesteht darin, die Symmetrie von differentiellen Paaren aufrechtzuerhalten. Wenn die Länge der differentiellen Paare nicht übereinstimmt, werden die Genauigkeit des Datenlesens und -schreibens beeinträchtigt und die Datenübertragungsrate verringert. Um die Gültigkeit des Datenlesens des Systems innerhalb desselben Zeitraums sicherzustellen, muss der Verzögerungsunterschied zwischen differentiellen Signalen innerhalb eines zulässigen Bereichs gehalten werden und die Leitungsführungslänge muss strikt identisch sein. Daher kann eine schlangenförmige Leitungsführung angewendet werden, um dieses Problem durch Anpassung der Laufzeitverzögerung zu lösen. In diesem Design erfolgt die Kommunikation zwischen PC und Kryptografiekarte über PCIe, und die Übertragung und der Empfang von Hochgeschwindigkeitssignalen werden über differentielle Paarsignale realisiert, wobei die Länge der Leiterplattenführung innerhalb von 25 mil kontrolliert wird. Das Abgleichsdiagramm der schlangenförmigen Leitungsführungslänge ist in Abbildung 5 dargestellt.