In der Hochgeschwindigkeitselektronik,mehrlagige Leiterplatteneine höhere Dichte, bessere Signalintegrität und stärkere Leistung für komplexe Anwendungen ermöglichen. Dennoch führen ihre kompakte Leiterführung, eng gestapelten Lagen undHochfrequenzsignaleauch ernsthafte Risiken durch elektromagnetische Störungen (EMI) mit sich bringen. Unkontrollierte EMI verschlechtert die Signalqualität, erzeugt Übersprechen, löst Systeminstabilität aus und führt zum Nichtbestehen von EMV‑Konformitätstests wie FCC, CE oder CISPR. Die Reduzierung von EMI ist kein optionales Extra – sie ist eine zentrale Voraussetzung für zuverlässige, zertifizierbare und marktreife Designs.

Dieser Artikel stellt praxisnahe, ingenieurserprobte Methoden zur Minimierung von EMI in mehrlagigen PCB‑Layouts vor und behandelt dabei Lagenaufbau, Erdung, Leiterführung, Filterung, Abschirmung und Validierung. Wenn Sie diese Richtlinien befolgen, können Sie Layouts erstellen, die Abstrahlung kontrollieren, Störungen eindämmen und eine stabile Leistung in realen elektromagnetischen Umgebungen aufrechterhalten.

Grundlagen der EMV in mehrlagigen Leiterplatten verstehen

Elektromagnetische Störungen (EMI) beschreiben unerwünschte elektromagnetische Energie, die den Betrieb von Schaltungen beeinträchtigt. Elektromagnetische Verträglichkeit (EMV) bedeutet, dass ein Gerät in seiner Umgebung ordnungsgemäß funktioniert, ohne unzulässige Störungen bei anderen Geräten zu verursachen. In mehrlagigen Leiterplatten entsteht EMI häufig durch:

Hochgeschwindigkeitssignale mit schnellen Flankenanstiegszeiten, die starke Hochfrequenzobertöne erzeugen

Große Stromschleifen, die durch schlechte Signalrückführungswege entstehen

Übersprechen zwischen eng beieinanderliegenden parallelen Leiterbahnen

Instabile Stromverteilung und Störungen auf den Stromschienen

Unsachgemäße Erdung, die abstrahlende Schleifen erzeugt

Schwebende Leiter, unbenutzte Pins oder lange Kabel, die als Antennen wirken

EMI breitet sich auf zwei Hauptwegen aus: durch Strahlung (luftgebundene Kopplung) und durch Leitung (entlang von Drähten oder Kabeln). Eine wirksame EMI-Reduzierung zielt bereits in der Layoutphase auf beide Wege ab.

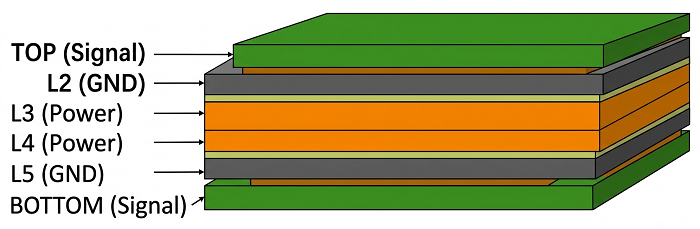

Optimieren Sie den Lagenaufbau für geringe EMI

Lagenaufbauist die Grundlage der EMI-Kontrolle in mehrlagigen Leiterplatten. Ein gut gestalteter Lagenaufbau verkürzt Rückstrompfade, hält elektrische und magnetische Felder zurück und reduziert die Geräuschkopplung zwischen den Lagen.

Verwenden Sie kontinuierliche Bezugsebenen

Jede Signalleitungsebene sollte eine angrenzende Masse- oder Versorgungsebene haben, um einen niederinduktiven Rückstrompfad bereitzustellen. Diese Struktur begrenzt elektromagnetische Felder und reduziert die Abstrahlung drastisch.

Für ein4-lagige Leiterplatteempfohlener Lagenaufbau: Signal → GND → Power → Signal

Für ein6‑lagige Leiterplatteempfohlener Lagenaufbau: Signal → GND → Power → Power → GND → Signal

Solide, durchgehende Ebenen sind deutlich besser als geteilte oder fragmentierte Ebenen. Vermeiden Sie Lücken, Schlitze oder übermäßige Hohlräume in Masse- und Versorgungsebenen, da diese Rückströme zu Umwegen zwingen und die Schleifenfläche vergrößern.

Leistungs- und Masseflächen eng koppeln

Platzieren Sie Leistungsflächen direkt angrenzend an Masseflächen mit dünnem Dielektrikum – idealerweise weniger als 0,254 mm (10 mil). Dies bildet einen natürlichen Hochfrequenz-Entkopplungskondensator, der die Spannung stabilisiert, die Impedanz verringert und Rauschen über einen breiten Frequenzbereich unterdrückt.

Vermeiden Sie isolierte Signalschichten

Platzieren Sie niemals eine Signallage zwischen zwei anderen Signallagen ohne eine dazwischenliegende Massefläche. Solche „isolierten“ Signallagen weisen starke Übersprechstörungen und eine schlechte Feldbegrenzung auf, was die EMV erheblich verschlechtert.

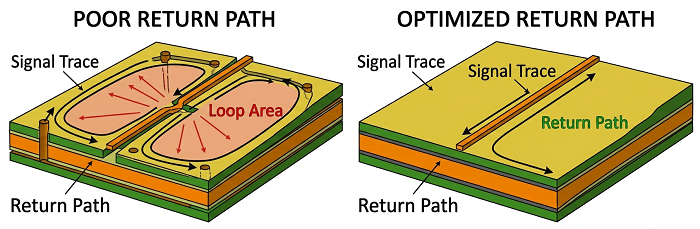

Beherrsche Erdungsstrategien

Erdung ist die mit Abstand wirksamste Methode zur Kontrolle von EMI. Schlechte Erdung erzeugt Schleifen, gemeinschaftliche Impedanzstörungen und abstrahlende Strukturen.

Verwenden Sie Mehrpunkt-Erdung für hohe Frequenzen

Für Schaltungen über 1 MHz ist eine Mehrpunkt-Erdung an eine durchgehende Massefläche überlegen. Sie verringert die Impedanz bei hohen Frequenzen und verhindert große Masseschleifen. Niederfrequente Schaltungen können eine Einpunkt-Erdung verwenden, um Umlaufströme zu vermeiden.

Fügen Sie Masse-Verbindungs-Vias hinzu

Verwenden Sie mehrere Massevias in der Nähe von Signalvias, die die Lage wechseln. Diese „Stitching-Vias“ erhalten einen kontinuierlichen Rückstrompfad, verhindern Feldleckagen an Lagenübergängen und stabilisieren die Impedanz. Für Hochgeschwindigkeitsdesigns sollte der Abstand zwischen Massevias unter 12,7 mm (0,5 Zoll) liegen.

Beseitigung von Erdschleifen

Gestalten Sie Rückstrompfade kurz, direkt und überlappend zu den Signalpfaden. Große Masseschleifen wirken als Schleifenantennen, die stark abstrahlen. Halten Sie Hochgeschwindigkeitsleitungen und ihre Rückstrompfade eng gekoppelt.

Steuerung der Leiterbahnführung zur Minimierung von Übersprechen und Abstrahlung

Die Leiterbahnführung wirkt sich direkt auf die elektromagnetische Verträglichkeit (EMV) aus. Sorgfältiges Routing verringert die Kopplung, verkürzt Antennen und erhält die Signalintegrität.

Befolge die 3W-Regel

Halten Sie einen Leiterbahnabstand von mindestens dem Dreifachen der Leiterbahnbreite ein. Dies verringert die kapazitive und induktive Übersprechung zwischen benachbarten Leiterbahnen. Verwenden Sie für rauschempfindliche oder hochfrequente Signale einen größeren Abstand.

Führen Sie kritische Signale auf Innenlagen

Führen Sie Taktleitungen, Hochgeschwindigkeits-Datenleitungen und störende Signale auf Innenlagen, die zwischen Masseflächen eingebettet sind. Diese Stripline-Struktur bietet eine hervorragende Abschirmung und hält elektromagnetische Felder eingeschlossen.

Vermeiden Sie Leitungsführung in der Nähe von Platinenrändern

Leiterbahnen in der Nähe von Platinenrändern strahlen stärker ab und sind anfälliger für äußere Störeinflüsse. Halten Sie Hochgeschwindigkeitsleiterbahnen mindestens eine Dielektrikumdicke vom Rand entfernt.

Differenzpaare verwenden

Für kritische Hochgeschwindigkeitsschnittstellen verwenden Sie eng gekoppelte, längenabgestimmte differentielle Paare. Sie unterdrücken Gleichtaktstörungen, verringern Abstrahlung und verbessern die Störfestigkeit.

Leitungslänge reduzieren

Kürzere Leiterbahnen bedeuten kleinere Antennen und geringere Abstrahlung. Minimieren Sie die Länge von Taktleitungen, Oszillator-Leiterbahnen und Signalen mit schnellen Flanken.

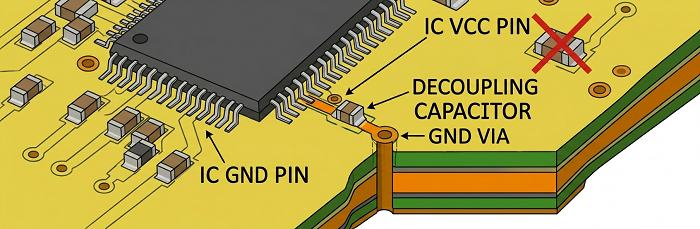

Verwenden Sie Entkopplung und Filterung effektiv

Entkopplungskondensatoren und EMI-Filter unterdrücken Störungen an ihrer Quelle, bevor sie sich über die Leiterplatte ausbreiten oder nach außen abstrahlen.

Entkopplungskondensatoren in der Nähe der ICs platzieren

Montieren Sie Hochfrequenzkondensatoren (z. B. 0,1 μF) innerhalb von 2,54 mm (100 mil) von den IC-Versorgungspins. Verwenden Sie kurze, breite Leiterbahnen oder direkte Via-Verbindungen, um parasitäre Induktivitäten zu minimieren. Kombinieren Sie kleine Kondensatoren für hohe Frequenzen und größere Bulk-Kondensatoren für die niederfrequente Stabilisierung.

Ferritperlen und Filter anwenden

Platzieren Sie Ferritperlen an den Stromeingängen, um Hochfrequenzrauschen zu dämpfen, während Gleichstrom passieren kann. Fügen Sie für I/O‑Ports und Versorgungsleitungen π‑Filter oder LC‑Filter hinzu, um leitungsgeführte EMI zu blockieren und zu verhindern, dass Kabel zu abstrahlenden Antennen werden.

Abschirmung und Bauteilplatzierung

Strategische Abschirmung und die Platzierung von Komponenten trennen Lärmquellen von empfindlichen Schaltungen.

Rauschen und empfindliche Schaltkreise trennen

Platzieren Sie Schaltregler, Taktgeber und HF‑Schaltungen entfernt von Analogschaltungen, Sensoren und niederpegeligen Empfängern. Verwenden Sie Masseflächen oder Schutzleiterbahnen, um Isolationsbarrieren zu schaffen.

Verwenden Sie Abschirmungen auf Komponentenebene

Decken Sie Oszillatoren, HF-Module und Schaltkreise mit Metallschirmgehäusen ab. Stellen Sie sicher, dass die Schirmungen über mehrere Vias sicher mit der Massefläche verbunden sind, um einen durchgehenden Faradayschen Käfig zu bilden.

Schutzringe und Masseflächen

Umgib empfindliche oder störanfällige Leiterbahnen mit geerdeten Schutzringen. Verwende Massekupferflächen auf den Außenlagen und verbinde sie mit den internen Masseflächen, um die Abschirmung zu verbessern. Vermeide schwebende Kupferflächen – sie können die EMV verschlechtern.

Auswahl von Leiterplattenmaterial

Materialeigenschaften beeinflussen die Hochfrequenzleistung und die elektromagnetische Verträglichkeit (EMV).

Wählen Sie Laminate mit einer stabilen Dielektrizitätskonstante (Dk), um die Impedanzkontrolle zu gewährleisten.

Verwenden Sie dünnere Dielektrika zwischen Stromversorgung und Masse, um die Kapazität zu erhöhen und das Rauschen zu verringern.

Für sehr hochfrequente Designs sollten Sie verlustarme Materialien in Betracht ziehen, um Signalabschwächung und Abstrahlung zu reduzieren.

EMI-Leistung validieren

Selbst das beste Layout erfordert eine Überprüfung.

Führen Sie Pre-Compliance-Tests mit Nahfeldsonden durch, um Hotspots während der Prototypenphase zu erkennen.

Führen Sie formale EMV-Tests in akkreditierten Laboren für gestrahlte Störaussendungen, leitungsgebundene Störaussendungen und Störfestigkeit durch.

Iterieren Sie das Layout auf der Grundlage der Testergebnisse, um Resonanz-, Strahlungs- oder Kopplungsprobleme zu beheben.

Häufige Fehler, die Sie vermeiden sollten

Ignorieren von Signalrückwegen und Zulassen großer Schleifen

Unnötiges Aufteilen von Masseflächen

Entkopplungskondensatoren zu weit von ICs platzieren

Hochgeschwindigkeitssignale über lange Strecken parallel führen

Ungenutzte Pins, Testpunkte oder Leiterbahnen offen lassen

Die Verschiebung der EMV-Prüfung bis zur endgültigen Designphase

Fazit

Die Reduzierung von EMI in mehrlagigen Leiterplattenlayouts erfordert eine systematische Planung in Bezug auf Stack-up, Erdung, Leiterführung, Filterung und Abschirmung. Wenn diese Methoden früh im Designzyklus umgesetzt werden, verbessern sie die EMV erheblich, verringern den Nacharbeitsaufwand und beschleunigen die Zertifizierung.

Für professionelle, hochzuverlässige mehrlagige Leiterplatten, die nach EMI‑optimierten Design- und Fertigungsstandards hergestellt werden, wählen Sie einen Partner mit umfassender Erfahrung in elektromagnetischer Verträglichkeit und Hochleistungsfertigung.

PCBCartist auf die fortschrittliche Fertigung von mehrlagigen Leiterplatten spezialisiert und bietet umfassende Unterstützung für EMV‑arme Layout‑Praktiken, hochwertige Materialien und strenge Prozesskontrolle. Ganz gleich, ob Sie Unterhaltungselektronik, Industrieanlagen oder Hochgeschwindigkeits‑Digitalsysteme entwickeln – PCBCart liefert Leiterplatten, die Leistung, Zuverlässigkeit und Normenkonformität vereinen. Mit PCBCart können Sie Ihr EMV‑optimiertes Layout in eine produktionsreife Leiterplatte umsetzen, die in realen Umgebungen zuverlässig und konsistent arbeitet.

Hilfreiche Ressourcen

•Sicherstellung eines erfolgreichen ersten Durchlaufs im PCB-EMV-Design

•Tipps für High-Speed-Layout

•Strategien für die Auslegung des Übersprechens zwischen zwei parallelen Mikrostreifenleitungen auf Leiterplatten

•Herausforderungen bei der Signalintegrität im High-Speed-PCB-Design und deren Lösungen