In den letzten Jahren waren eine Miniaturisierung, Integration und Modularisierung elektronischer Produkte zu beobachten, was zu einer Erhöhung der Bestückungsdichte elektronischer Bauteile und zu einer Verringerung der effektiven Wärmeabstrahlfläche geführt hat. Daher sind das thermische Design von Hochleistungselektronikbauteilen und Wärmeableitungsprobleme auf Leiterplattenebene zu weit verbreiteten Themen unter Elektronikingenieuren geworden. Für FPGA‑Systeme (Field Programmable Gate Array) ist die Wärmeableitung eine der entscheidenden Technologien, die bestimmen, ob der Chip in der Lage ist, normal zu arbeiten. Das Ziel vonThermisches Design von Leiterplattenbesteht darin, die Temperatur von Bauteilen und Leiterplatte durch geeignete Maßnahmen und Methoden zu senken, damit das System bei einer geeigneten Temperatur arbeitet. Trotz zahlreicher Maßnahmen zur Wärmeableitung von Leiterplatten müssen einige Anforderungen berücksichtigt werden, wie etwa die Kosten der Wärmeableitung und die Praktikabilität. Dieser Artikel stellt Wärmeauslegungsmethoden für Leiterplatten vor, die von einem FPGA-System gesteuert werden, basierend auf der Analyse praktischer Probleme der Wärmeableitung, um die hervorragende Wärmeableitungsfähigkeit der FPGA-System-Steuerplatine sicherzustellen.

FPGA-Systemsteuerungsplatine und Wärmeableitungsproblem

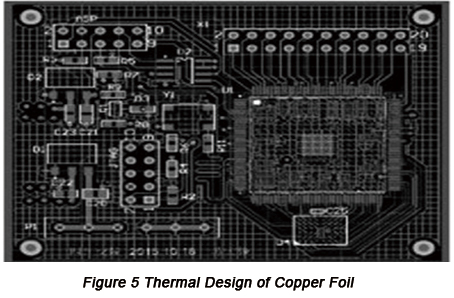

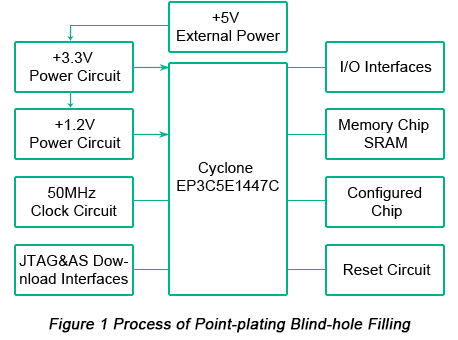

Die in diesem Artikel verwendete FPGA-Systemsteuerplatine besteht hauptsächlich aus dem Steuerchip FPGA (EP3C5E144C7 mit QFP-Gehäuse der Cyclone-III-Serie von Altera®), +3,3V- und +1,2V-Stromversorgungsschaltungen, 50-MHz-Taktschaltung, Reset-Schaltung, JTAG- und AS-Download-Schnittstellenschaltung, SRAM-Speicher- und E/A-Schnittstelle. Die Struktur der FPGA-Systemsteuerplatine ist in Abbildung 1 unten dargestellt.

Wärmequellen der durch ein FPGA-System gesteuerten Leiterplatte stammen aus:

• Zahlreiche Arten von Stromversorgungen für die Steuerplatine, wie +5 V, +3,3 V und +1,2 V, sowie Leistungsmodule erzeugen bei längerem Betrieb eine große Menge an Wärme. Leistungsmodule funktionieren in der Regel nicht ordnungsgemäß, wenn nicht geeignete Maßnahmen wirksam ergriffen werden.

• Die Taktfrequenz des FPGA auf der Steuerplatine beträgt 50 MHz bei hoher Dichte der Leiterplattenverdrahtung. Die steigenden Anforderungen an die Systemintegrität führen zu einem hohen Systemstromverbrauch, und es sollten notwendige Maßnahmen zur Wärmeableitung für den FPGA-Chip getroffen werden.

• Das Leiterplatten-Substrat erzeugt selbst Wärme. Der Kupferleiter gehört zu denGrundmaterialien von Leiterplattenund Kupferleiterstromkreise erzeugen Wärme durch den Austausch von Strom und Energieverbrauch.

Basierend auf der Analyse der Wärmequellen des von der FPGA-Steuerplatine kontrollierten Schaltkreissystems müssen notwendige Maßnahmen zur Wärmeableitung an der FPGA-Steuerplatine ergriffen werden, um die Stabilität und Zuverlässigkeit des gesamten Systems zu erhöhen.

Thermisches Design von Leiterplatten, gesteuert durch FPGA-Chip

1. Thermisches Design von Leistung

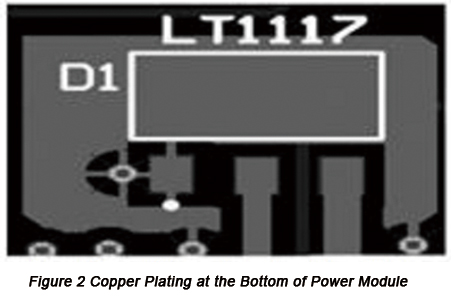

Die FPGA-Systemsteuerplatine ist mit einer externen Gleichstromversorgung (DC) von +5 V verbunden, die einen Strom von mehr als 1 A liefern muss. Als Stromversorgungsmodul wird der LDO-Chip LT1117 (im kleinen SOT-23-SMD-Gehäuse) ausgewählt, der in der Lage ist, die +5-V-Gleichstromversorgung in eine +3,3-V-VCCIO-Schnittstellenspannung und eine +1,2-V-VCCINT-VCORE umzuwandeln.

Gemäß der obigen Analyse werden im Prozess der Leistungsstromkreisentwicklung zwei LT1117-Chips benötigt, um die Spannungsanforderungen von +3,3 V und +1,2 V des FPGA zu erfüllen. Maßnahmen zur Wärmeableitung der Leistungsmodule im Prozess des PCB-Designs umfassen die folgenden Aspekte:

• Um eine schnelle Wärmeableitung des Leistungsmoduls sicherzustellen, das den FPGA-Chip mit Strom versorgt, sollte bei Bedarf ein Kühlkörper am LDO-Chip angebracht werden.

• Da das Leistungsmodul nach längerem Betrieb Wärme erzeugt, muss ein bestimmter Abstand zwischen benachbarten Leistungsmodulen eingehalten werden. Der Abstand zwischen zwei LDO-Chips LT1117 sollte 20 mm oder mehr betragen.

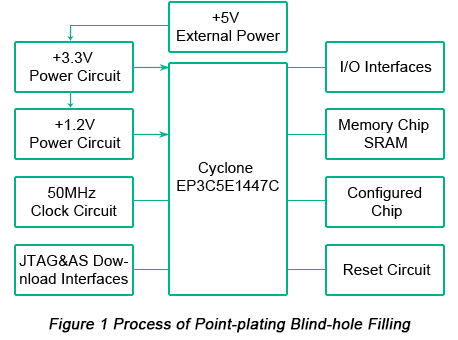

• Um zur Wärmeableitung beizutragen, sollte an der Stelle des LDO-Chips LT1117, wie in Abbildung 2 gezeigt, eine eigenständige Kupferbeschichtung vorgenommen werden.

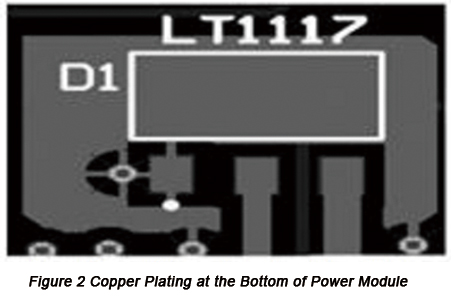

2. Thermisches Design von Durchkontaktierungen

Am unteren Rand von Bauteilen mit hoher Wärmeentwicklung auf Leiterplatten (PCBs) oder in deren Nähe sollten einige leitfähige Metall-Vias platziert werden. Thermische Entwärmungs-Vias sind kleine, die Leiterplatte durchdringende Löcher mit einem Durchmesser im Bereich von 0,4 mm bis 1 mm und einem Abstand zwischen den Vias im Bereich von 1 mm bis 1,2 mm. Die die Leiterplatte durchdringenden Vias sorgen dafür, dass die Energie an der Vorderseite schnell auf andere Wärmeableitungsschichten übertragen wird, sodass die Bauteile auf der heißen Seite der Leiterplatte sofort abgekühlt werden, die Wärmeabstrahlfläche effektiv vergrößert und der Widerstand verringert wird. Schließlich kann die Leistungsdichte der Leiterplatte verbessert werden. Das thermische Design der Durchkontaktierungen ist in Abbildung 3 unten dargestellt.

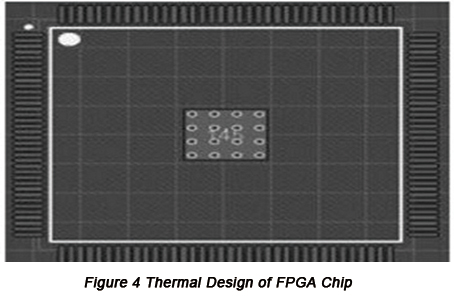

3. Thermisches Design des FPGA-Chips

Die Wärmeentwicklung des FPGA-Chips stammt hauptsächlich aus dem dynamischen Energieverbrauch wie dem Energieverbrauch der VCORE- und I/O-Spannung, dem von Speicher, interner Logik und System erzeugten Energieverbrauch sowie dem Energieverbrauch, der durch den FPGA beim Ansteuern anderer Module (z. B. Video-, Funkmodule) entsteht. Beim Entwurf des FPGA-Chip-QFP-Gehäuses wird in der Mitte des FPGA-Chips eine Kupferfolie mit einer Größe von 4,5 mm × 4,5 mm hinzugefügt und es werden mehrere Wärmeableitpads vorgesehen. Bei Bedarf kann ein Kühlkörper hinzugefügt werden. Das thermische Design des FPGA-Chips ist in Abbildung 4 unten dargestellt.

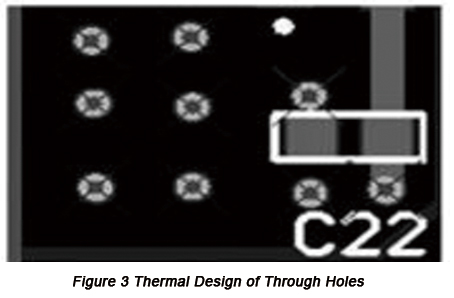

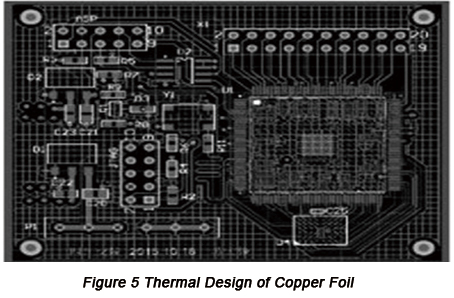

4. Thermisches Design der Kupferbeschichtung

Das Beschichten von Leiterplatten mit Kupfer kann sowohl die Störfestigkeit der Schaltungen erhöhen als auch die Wärmeableitung der Leiterplatten verbessern. Das auf Altium Designer Summer 09 basierende PCB-Design weist in der Regel zwei Arten von Kupferbeschichtung auf: vollflächige Kupferbeschichtung und gitterförmige Kupferbeschichtung. Die vollflächige, streifenförmige Kupferbeschichtung hat den Nachteil, dass bei langem Betrieb der Leiterplatte viel Wärme entsteht, wodurch sich die streifenförmige Kupferfolie ausdehnen und ablösen kann. Um daher eine hervorragende Wärmeableitungsfähigkeit der Leiterplatte zu erreichen, sollte die Kupferbeschichtung in Gitterform ausgeführt und mit dem Masse-Netzwerk der Schaltung verbunden werden, sodass sowohl die Abschirmwirkung des Systems als auch die Wärmeableitungsleistung verbessert werden. Das thermische Design der Kupferbeschichtung ist in Abbildung 5 unten dargestellt.