En la actualidad, el rápido desarrollo de la tecnología de Internet ha dado lugar a la amplia aplicación del correo electrónico, el pago en línea y la comunicación personal. En este contexto, la seguridad de la información se ha convertido en un tema de investigación crucial en todo el mundo. La tecnología PKI (Infraestructura de Clave Pública) proporciona servicios de seguridad mediante el uso de la teoría y la tecnología de clave pública. La tecnología PCIE (Peripheral Component Interface Express) ha recibido una amplia aplicación en dispositivos de alta velocidad como el estándar de bus de E/S de tercera generación que aplica la transmisión de datos en serie y la tecnología de interconexión punto a punto. En el campo del diseño de sistemas digitales, una frecuencia de reloj relativamente alta provoca algunos problemas en cuanto a la integridad de la señal, la integridad de la potencia y la diafonía, y el diseño tradicional de PCB no logra satisfacer los requisitos de estabilidad del sistema.

Este artículo ofrece un esquema de diseño de PCB para una tarjeta de contraseña de alta velocidad basada en PCIe, de acuerdo con las ventajas de la transmisión serie de alta velocidad de PCIe.

Esquema general de diseño

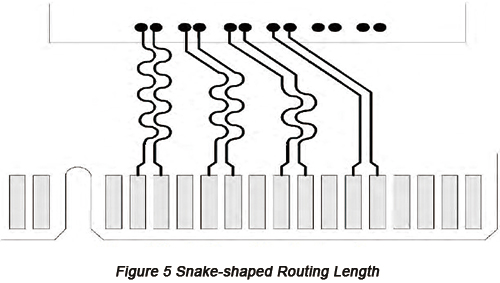

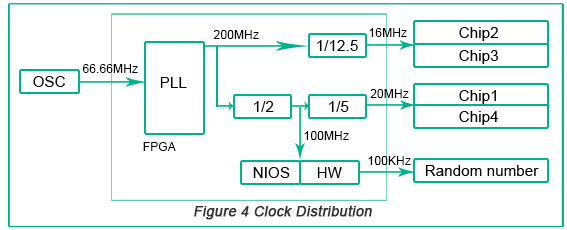

En este diseño se aplica el chip FPGA EP4CGX50CF23C6N perteneciente a la familia Cyclone IV GX, diseñado por Altera, que integra el módulo IP hardcore de PCIE e implementa el diseño de una tarjeta de contraseña de transmisión de datos de alta velocidad de 4 canales. Cuatro tipos de chips, chip 1, chip 2, chip 3 y chip 4, son capaces de implementar respectivamente los algoritmos SM1, SM2/SM3, SM4 y SSF33, así como las funciones de inicialización de la tarjeta de contraseña, administración de claves secretas, copia de seguridad y recuperación, y gestión de autorizaciones. Las tarjetas de contraseña se aplican en PC, se conectan a la placa base del PC a través de la ranura PCIE y son controladas por el PC. El IP hardcore en el FPGA se utiliza para implementar PCIE, lo que permite la comunicación entre el núcleo PCIE y la memoria caché SRAM y el módulo de control. Como centro de control, NiosII implementa la función del software de la tarjeta de contraseña. Al mismo tiempo, un chip de contraseña adicional implementa la comunicación entre cada módulo de interfaz y la tarjeta de contraseña. El diseño de la estructura de hardware de la tarjeta de contraseña se ilustra en la Figura 1 a continuación.

Diseño de PCB de alta velocidad

• Apilamiento y diseño

El diseño del apilado es el problema más importante que debe tenerse en cuenta, y un diseño de apilado razonable puede inhibir la radiación EMI (Interferencia Electromagnética), haciendo que el voltaje transitorio en el plano de alimentación o en la capa de tierra sea lo más pequeño posible y blindando el campo electromagnético de la señal y la alimentación. Generalmente, en el diseño de circuitos digitales de alta velocidad se utilizan placas multicapa y múltiples fuentes de alimentación.Diseño de apilamiento de PCBse implementa en función de elementos integrales que incluyen la frecuencia de reloj del circuito,Costo de fabricación de PCB, densidad de pines, período de fabricación y fiabilidad. Además, las capas de la placa multicapa deben mantenerse simétricas y el número de capas debe ser par, ya que un diseño de apilamiento asimétrico provocará alabeo de las placas. La tarjeta de contraseña diseñada en este artículo se conecta al PC a través de la ranura PCIE y el tamaño y la forma de la placa de circuito están fijados con una altura de aproximadamente 67 mm y una longitud de aproximadamente 174 mm, configurando un pin de interfaz PCIE X4 en la parte inferior. Como resultado de la alta densidad de componentes y el enrutamiento grueso, el número de capas de PCB se selecciona como 6 capas con la distribución de capa de señal, capa de alimentación, capa de señal, capa de alimentación, capa de tierra, capa de señal. Este diseño contiene 3 capas de señal, 1 capa de tierra y 2 capas de alimentación, proporcionando el entorno requerido para la integridad de la señal.

Tras la determinación del apilado de la PCB, deben implementarse los grupos de componentes y el diseño. En primer lugar, la posición de los componentes debe programarse de acuerdo con las dimensiones y el patrón de la PCB, teniendo en cuenta la conexión de líneas, la partición funcional y la armonía y estética entre los componentes. Luego, los componentes deben distribuirse razonablemente según los diferentes niveles de tensión de los componentes para que los cables de alimentación sean lo más cortos posible, lo que permite reducir la interferencia del ruido de alimentación y aumentar la estabilidad de la fuente de alimentación. La colocación de los chips debe prestar atención a la relación entre su circuito auxiliar y el propio chip, así como a la colocación del cristal oscilador detrás de los pines de reloj. Debe evitarse colocar componentes de alto ruido alrededor del cristal oscilador y estos deben situarse cerca de sus componentes de accionamiento. Además, la colocación de cada pin de alimentación y de señal de los chips debe considerarse ajustando sus posiciones y orientación en función de las líneas conectadas.

Dado que la relación entre la longitud y la anchura de la tarjeta de contraseña es superior a 2:1 y que las posiciones de la ranura PCIE, los orificios de montaje y los LED indicadores están fijadas, en el diseño de componentes debe considerarse primero la disposición de los componentes fijos. Además, debido al gran número de líneas de conexión entre los componentes y el FPGA, la disposición de los componentes debe realizarse tomando el FPGA como centro antes de determinar las posiciones de los demás componentes, de modo que se pueda utilizar eficazmente el espacio superior e inferior de la PCB para dejar suficiente espacio entre los componentes y entre estos y los orificios de posicionamiento.

• Diseño de energía

Endiseño de placas de circuito de alta velocidad, el diseño del sistema de alimentación está directamente relacionado con el éxito de todo el sistema. El ruido generado por la alimentación y la tierra debe reducirse al mínimo para garantizar la fiabilidad de los productos. La aplicación del esquema de distribución de potencia en el método de capas se refiere a que la alimentación se distribuye a través del metal en toda la capa, disminuyendo la impedancia de la alimentación y el ruido y aumentando la fiabilidad. Debido a que la PCB implica múltiples alimentaciones, debe aplicarse un diseño de capas de alimentación múltiples, capaz de eliminar la interferencia de acoplamiento por impedancia común como un bucle de ruido. La aplicación de la capacitancia de desacoplo es capaz de resolver el problema de la integridad de la alimentación, ya que el condensador solo puede colocarse en la capa inferior o superior de la PCB, sobre cuya base los conductores que conectan los condensadores de desacoplo deben ser cortos y anchos. De acuerdo con el material del chip, se puede calcular la corriente que pasa a través de las líneas de alimentación y se puede determinar el ancho de las pistas. Cuanto más anchas sean las pistas, más corriente pueden transportar. La fórmula experimental se ilustra como:W(ancho de línea: mm) ≥L(mm/A) xYo(actual: A)

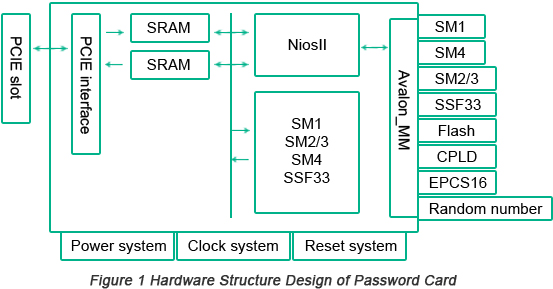

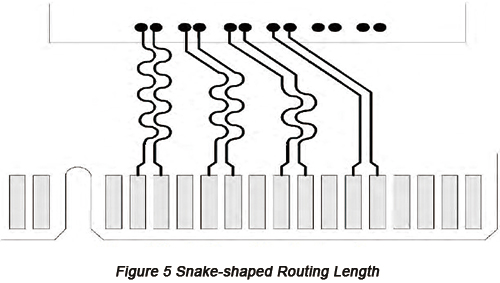

Múltiples fuentes de alimentación en la PCB obtienen uno o dos tipos de energía de la placa de alimentación mediante la placa posterior y luego dicha energía se convierte en otras tensiones requeridas por los componentes. La conversión de energía se divide en dos arquitecturas: arquitectura de alimentación centralizada y arquitectura de alimentación distribuida. La primera se refiere a que la energía es suministrada por una fuente de alimentación independiente y luego se convierte en todo tipo de tensiones requeridas, mientras que la segunda se refiere a la conversión de energía en múltiples etapas. Debido a que la arquitectura de alimentación centralizada presenta desventajas de alto costo y gran área de PCB, en este diseño se aplica la arquitectura de alimentación distribuida. La tarjeta criptográfica utiliza 6 tensiones, incluyendo 12 V, 3,3 V, 5 V, 2,5 V, 1,2 V y 1,8 V. Este diseño comienza con la participación de las tensiones de 3,3 V y 12 V en la ranura PCIE y luego la tensión de 3,3 V es capaz de generar 5 V y 1,8 V mediante un chip de conversión de voltaje, suministrando energía para el módulo enchufable y el chip 3. A continuación, la tensión de 12 V se convierte en 2,5 V para alimentar el FPGA y el chip 4. Finalmente, la tensión de 2,5 V se convierte en 1,2 V para alimentar el FPGA y el chip 2. La arquitectura de alimentación distribuida de la tarjeta criptográfica se muestra en la Figura 2 a continuación.

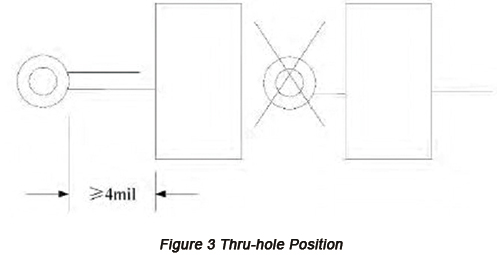

• Diseño de orificio pasante

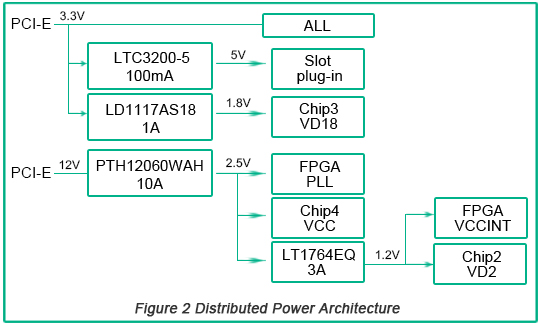

En el proceso de diseño de la maquetación paraplacas de circuito impreso multicapacon alta densidad, se deben aplicar orificios pasantes, transmitiendo la señal de una capa a otra para proporcionar comunicación eléctrica entre capas. El diseño de la posición de los orificios pasantes debe realizarse con mucho cuidado. Los orificios pasantes no deben colocarse sobre la almohadilla y se puede aplicar una sola línea impresa para la conexión, de lo contrario se producirán problemas como efecto “tombstone” y soldadura insuficiente. Debe recubrirse máscara de soldadura sobre la almohadilla del orificio pasante con una distancia establecida de 4 mil, y los orificios pasantes no deben colocarse en el centro de la almohadilla para los componentes de chip en el lado de soldadura. La posición de los orificios pasantes se ilustra en la Figura 3 a continuación.

Además, la posición del orificio pasante no debe estar demasiado cerca del conector tipo “goldfinger”, cuyo lado de inserción debe incluir un chaflán. Para que las placas de circuito se puedan insertar en la ranura PCIE, se puede diseñar un chaflán de (1~1.5)x45° en los dos bordes laterales de la placa de inserción.

• Enrutamiento de señales de alta velocidad

En el proceso de enrutamiento, la distribución debe ajustarse de manera razonable para minimizar las líneas de conexión y así reducir la diafonía. En el proceso de enrutamiento de señales digitales de alta velocidad, el enrutamiento de la capa de señal cercana a la capa de múltiples alimentaciones debe mantenerse alejado de la superficie de referencia de potencia para evitar la generación de una trayectoria de retorno por la corriente de señal.

Dado que la frecuencia de la señal de reloj en circuitos de alta velocidad es relativamente alta, el jitter, la deriva y la deformación influyen en gran medida en el sistema, por lo que el diseño de PCB de alta velocidad requiere una pequeña interferencia en la forma de onda de la señal. Por lo tanto, el problema de la distribución y el ruteo del reloj debe considerarse en primer lugar. El ruteo debe implementarse en las señales de reloj de alta velocidad y el trazado de las líneas de señal del reloj principal debe ser lo más corto posible, recto y sin orificios pasantes ni partes de alimentación, a fin de evitar la diafonía entre el reloj y la alimentación. Cuando se aplican múltiples relojes con diferentes frecuencias en la misma PCB, dos líneas de reloj con diferentes frecuencias no deben mantenerse en paralelo. Sin embargo, para múltiples componentes que utilizan señales de reloj con la misma frecuencia, la red puede distribuirse en forma de araña, en árbol o en rama.

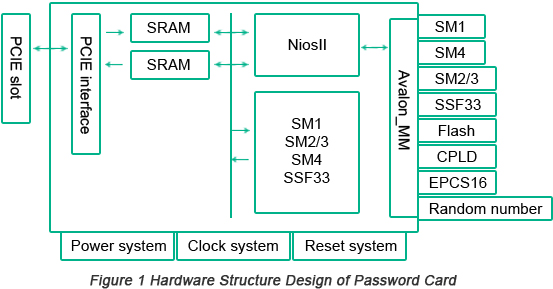

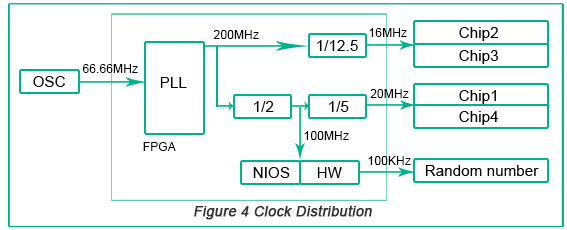

En la tarjeta criptográfica de alta velocidad, el FPGA obtiene una señal de reloj de 66,66 MHz a través del oscilador de cristal en la PCB. Después de un bucle con los bloqueos internos del FPGA, se genera un reloj básico de 200 MHz como interfaz para que el chip 2 y el chip 3 operen con ese reloj. Luego, se proporciona un reloj de 100 MHz mediante el circuito interno de división de frecuencia, que sirve como núcleo blando NiosII y como reloj de trabajo del circuito de hardware dentro del FPGA. La frecuencia dividida de 16 MHz es el reloj de trabajo para el chip 2 y el chip 3, mientras que la frecuencia dividida de 20 MHz es el reloj de trabajo para el chip 1 y el chip 4. La distribución de reloj se muestra en la Figura 4 a continuación.

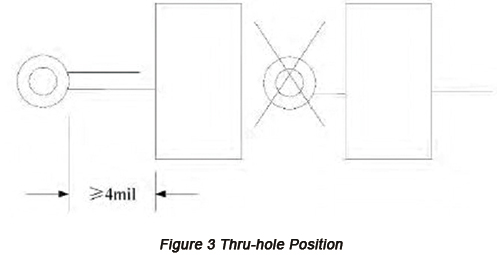

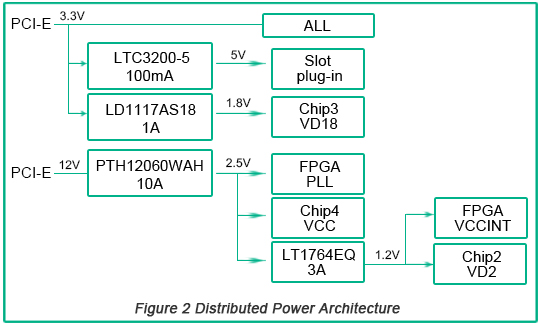

La transmisión de señales de alta velocidad entre la ranura PCIE y el PC se implementa mediante una tarjeta criptográfica de alta velocidad utilizando el enrutamiento de pares diferenciales para evitar problemas relacionados con la integridad de la señal. En términos generales, no se colocan cables de tierra entre las señales de pares diferenciales, de lo contrario se destruiría el efecto de acoplamiento entre dichas señales. Después del enrutamiento de las señales de pares diferenciales, se coloca cobre alrededor de las señales de alta velocidad de la PCB y el espacio libre se rellena completamente con cables de tierra para aumentar la capacidad EMI del circuito. La clave deEnrutamiento de PCBes mantener la simetría de los pares diferenciales. Si la longitud de los pares diferenciales no es compatible, se verá afectada la precisión de lectura y escritura de datos y disminuirá la velocidad de transmisión de datos. Para garantizar la validez del sistema en la lectura de datos dentro del mismo período, la diferencia de retardo entre las señales diferenciales debe mantenerse dentro de un rango permitido y la longitud del ruteo debe ser estrictamente la misma. Por lo tanto, se puede aplicar un ruteo en forma de serpentina para resolver este problema ajustando el retardo de tiempo. En este diseño, la comunicación se implementa mediante PC a través de PCIE y la tarjeta criptográfica, y la transmisión y recepción de señales de alta velocidad se implementan mediante señales de par diferencial con la longitud del ruteo en la PCB controlada dentro de 25 mil. El diagrama de coincidencia de la longitud del ruteo en serpentina se muestra en la Figura 5.