À l’heure actuelle, le développement rapide des technologies Internet s’accompagne d’une utilisation massive du courrier électronique, du paiement en ligne et de la communication personnelle. Dans ce contexte, la sécurité de l’information est devenue un thème de recherche crucial dans le monde entier. La technologie PKI (Public Key Infrastructure) fournit des services de sécurité en s’appuyant sur la théorie et la technologie de la clé publique. La technologie PCIE (Peripheral Component Interface Express) a trouvé de larges applications dans les dispositifs à haute vitesse en tant que norme de bus d’E/S de troisième génération, utilisant la transmission de données série et la technologie d’interconnexion point à point. Dans le domaine de la conception de systèmes numériques, une fréquence d’horloge relativement élevée entraîne certains problèmes en termes d’intégrité du signal, d’intégrité de l’alimentation et de diaphonie, et la conception traditionnelle de PCB ne parvient pas à satisfaire aux exigences de stabilité du système.

Cet article propose un schéma de conception de PCB pour une carte à mot de passe haute vitesse basée sur PCIe, en s’appuyant sur les avantages de la transmission série haute vitesse de PCIe.

Schéma de conception global

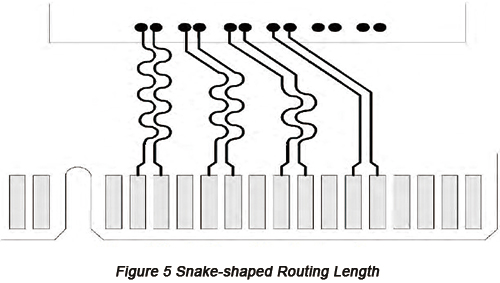

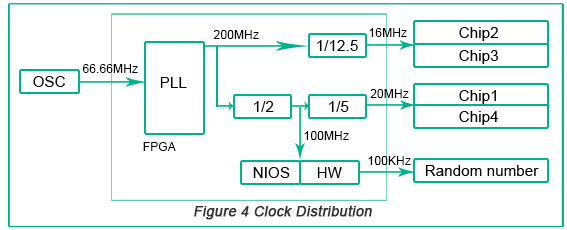

La puce FPGA EP4CGX50CF23C6N appartenant à la famille Cyclone IV GX conçue par Altera est utilisée dans cette conception, intégrant un module IP PCIE dur et réalisant la conception d’une carte de mot de passe pour transmission de données à haute vitesse à 4 voies. Quatre types de puces, puce 1, puce 2, puce 3 et puce 4, sont capables de mettre en œuvre respectivement les algorithmes SM1, SM2/SM3, SM4 et SSF33, ainsi que les fonctions d’initialisation de la carte de mot de passe, de gestion de clé secrète, de sauvegarde et de restauration, et de gestion des autorisations. Les cartes de mot de passe sont utilisées dans les PC, connectées à la carte mère des PC via un emplacement PCIE et contrôlées par les PC. L’IP dur dans le FPGA est utilisée pour implémenter le PCIE, permettant la communication entre le cœur PCIE, le cache SRAM et le module de contrôle. En tant que centre de contrôle, NiosII implémente la fonction logicielle de la carte de mot de passe. Parallèlement, une puce de mot de passe supplémentaire met en œuvre la communication entre chaque module d’interface et la carte de mot de passe. La conception de la structure matérielle de la carte de mot de passe est illustrée à la Figure 1 ci-dessous.

Conception de PCB haute vitesse

• Empilage et routage

La conception de l’empilage est le problème le plus important à prendre en compte, et une conception d’empilage raisonnable peut inhiber le rayonnement EMI (interférences électromagnétiques), en rendant la tension transitoire sur le plan d’alimentation ou la couche de masse aussi faible que possible et en blindant le champ électromagnétique du signal et de l’alimentation. En général, les circuits imprimés multicouches et les alimentations multiples sont utilisés dans la conception de circuits numériques à haute vitesse.Conception d’empilage de PCBest mis en œuvre sur la base d’éléments complets, y compris la fréquence d’horloge du circuit,Coût de fabrication des circuits imprimés, densité de broches, période de fabrication et fiabilité. De plus, les couches d’une carte multicouche doivent rester symétriques et le nombre de couches doit être pair, car une conception d’empilement asymétrique provoquera le gauchissement des cartes. La carte à mot de passe conçue dans cet article est connectée au PC via un slot PCIE et la taille ainsi que la forme du circuit imprimé sont fixes, avec une hauteur d’environ 67 mm et une longueur d’environ 174 mm, configurant un connecteur PCIE X4 au bas. En raison de la forte densité de composants et du routage épais, le nombre de couches du PCB est fixé à 6, avec la répartition suivante : couche de signal, couche d’alimentation, couche de signal, couche d’alimentation, couche de masse, couche de signal. Cette conception comprenant 3 couches de signal, 1 couche de masse et 2 couches d’alimentation fournit l’environnement requis pour l’intégrité du signal.

Après la détermination de l’empilement du PCB, les groupes de composants et l’implantation doivent être réalisés. Tout d’abord, la position des composants doit être définie conformément aux dimensions et au motif du PCB, en tenant compte du routage, du partitionnement fonctionnel ainsi que de l’alignement et de l’esthétique entre les composants. Ensuite, les composants doivent être répartis de manière raisonnable en fonction des différents niveaux de tension des composants afin de rendre les pistes d’alimentation aussi courtes que possible, ce qui permet de réduire les interférences dues au bruit d’alimentation et d’augmenter la stabilité de celle-ci. Le placement des circuits intégrés doit prêter attention à la relation entre chaque puce et son circuit auxiliaire, ainsi qu’au placement de l’oscillateur à quartz derrière les broches d’horloge. Les composants à fort bruit doivent être évités à proximité de l’oscillateur à quartz et placés près de leurs composants de commande. En outre, le placement de chaque broche d’alimentation et de signal des puces doit être pris en compte, avec ajustement de leurs positions et orientations en fonction des pistes qui y sont connectées. Étant donné que le rapport longueur/largeur de la carte à mot de passe est supérieur à 2:1 et que les positions du connecteur PCIE, des trous de fixation et des LED d’indication sont fixes, l’implantation des composants fixes doit être prise en considération en premier lors de l’implantation des composants. De plus, en raison du grand nombre de lignes de connexion entre les composants et le FPGA, l’implantation des composants doit être réalisée en prenant le FPGA comme centre avant de déterminer les positions des autres composants, de manière à utiliser efficacement l’espace supérieur et inférieur du PCB afin de laisser suffisamment d’espace entre les composants ainsi qu’entre les composants et les trous de positionnement.

• Conception de l’alimentation

Dansconception de circuits imprimés à haute vitessela conception du système d’alimentation est directement liée au succès de l’ensemble du système. Le bruit généré par l’alimentation et la masse doit être réduit au minimum afin de garantir la fiabilité des produits. L’application du schéma de distribution de puissance dans la méthode par couches signifie que l’alimentation est distribuée à travers le métal sur toute la couche, ce qui diminue l’impédance et le bruit de l’alimentation et augmente la fiabilité. Étant donné que plusieurs alimentations sont concernées par le PCB, une conception à couches d’alimentations multiples doit être appliquée, capable d’éliminer le couplage d’impédance commune comme une boucle de bruit. L’application de la capacité de découplage est capable de résoudre le problème d’intégrité de l’alimentation, puisque les condensateurs ne peuvent être placés que sur la couche inférieure ou supérieure du PCB, sur la base de quoi les fils reliant les condensateurs de découplage doivent être courts et larges. Selon le matériau de la puce, le courant traversant les lignes d’alimentation peut être calculé et la largeur des pistes peut être déterminée. Plus les pistes sont larges, plus elles peuvent transporter de courant. La formule expérimentale est illustrée comme suit :W(largeur de ligne : mm) ≥L(mm/A) xJe(actuel : A)

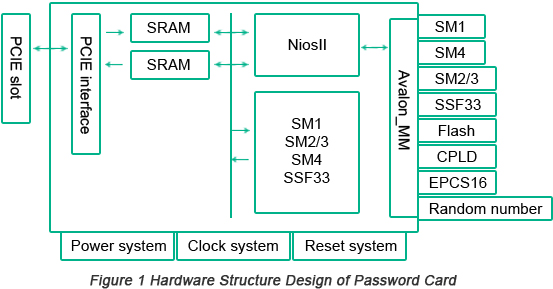

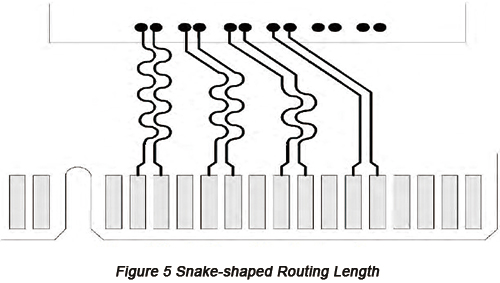

Plusieurs alimentations sur le PCB obtiennent un ou deux types d’alimentation à partir de la carte d’alimentation via la carte arrière, puis cette alimentation est convertie en d’autres tensions requises par les composants. La conversion de l’alimentation est divisée en deux architectures : l’architecture d’alimentation centralisée et l’architecture d’alimentation distribuée. La première signifie que l’alimentation est fournie par une source d’alimentation indépendante puis convertie en toutes sortes de tensions requises, tandis que la seconde correspond à une conversion d’alimentation en plusieurs étages. En raison des inconvénients de l’architecture d’alimentation centralisée, à savoir un coût élevé et une grande surface de PCB, l’architecture d’alimentation distribuée est appliquée dans cette conception. La carte cryptographique utilise 6 alimentations, incluant 12 V, 3,3 V, 5 V, 2,5 V, 1,2 V et 1,8 V. Cette conception commence par l’utilisation des alimentations 3,3 V et 12 V présentes dans le slot PCIE, puis l’alimentation 3,3 V permet de générer les alimentations 5 V et 1,8 V via une puce de conversion de tension, fournissant l’alimentation pour la carte enfichable et la puce 3. Ensuite, l’alimentation 12 V est convertie en 2,5 V pour alimenter le FPGA et la puce 4. Enfin, l’alimentation 2,5 V est convertie en 1,2 V pour alimenter le FPGA et la puce 2. L’architecture d’alimentation distribuée de la carte cryptographique est illustrée à la Figure 2 ci-dessous.

• Conception à trous traversants

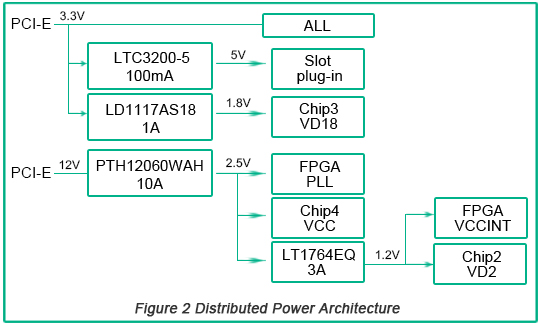

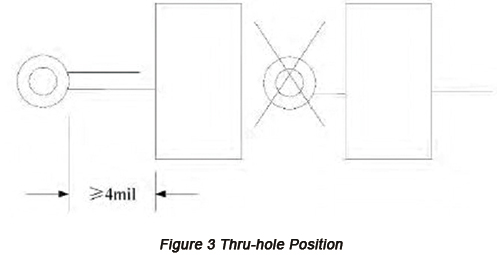

Dans le processus de conception de la mise en page pourcircuits imprimés multicouchesavec une haute densité, des trous traversants doivent être appliqués, transmettant le signal d’une couche à une autre afin d’assurer la communication électrique entre les couches. La conception de l’implantation des trous traversants doit être réalisée avec beaucoup de soin. Les trous traversants ne doivent pas être placés sur les pastilles et une seule piste imprimée peut être utilisée pour la connexion, sous peine de provoquer des problèmes tels que l’effet « tombstone » et un apport de soudure insuffisant. Un vernis épargne doit être appliqué sur la pastille du trou traversant avec une distance fixée à 4 mil, et les trous traversants ne doivent pas être placés au centre de la pastille pour les composants CMS du côté soudure. La position des trous traversants est illustrée à la Figure 3 ci‑dessous.

De plus, la position des trous traversants ne doit pas être trop proche du connecteur à doigts d’or, dont le côté d’insertion doit comporter un chanfrein. Afin de permettre l’insertion des circuits imprimés dans le logement PCIE, un chanfrein de (1~1,5)x45° peut être conçu sur les deux bords latéraux de la carte enfichable.

• Routage de signaux à haute vitesse

Dans le processus de routage, la distribution doit être ajustée de manière raisonnable afin de minimiser les lignes de connexion, de façon à réduire la diaphonie. Dans le processus de routage de signaux numériques à haute vitesse, le routage de la couche de signal proche d’une couche d’alimentation multiple doit être éloigné de la surface de référence d’alimentation afin d’éviter la génération d’un chemin de retour par le courant de signal.

Étant donné que la fréquence du signal d’horloge des circuits à haute vitesse est relativement élevée, le jitter, la dérive et la déformation influencent fortement le système, de sorte que la conception de PCB haute vitesse exige une faible interférence sur les signaux. Par conséquent, le problème de la distribution et du routage de l’horloge doit être considéré en premier lieu. Le routage doit être appliqué aux signaux d’horloge haute vitesse et le tracé des lignes de l’horloge principale doit être aussi court que possible, rectiligne et exempt de vias et de parties d’alimentation afin de prévenir la diaphonie entre l’horloge et l’alimentation. Lorsque plusieurs horloges de fréquences différentes sont utilisées sur le même PCB, deux lignes d’horloge de fréquences différentes ne doivent pas être maintenues parallèles. En revanche, pour plusieurs composants utilisant des signaux d’horloge de même fréquence, le réseau peut être distribué en étoile, en arbre ou en branches.

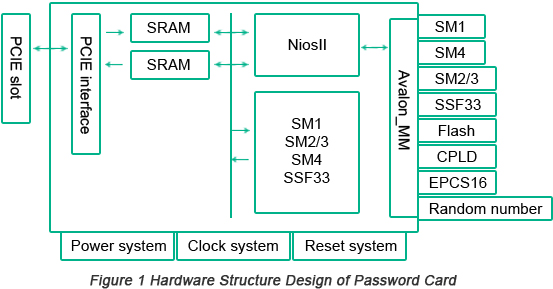

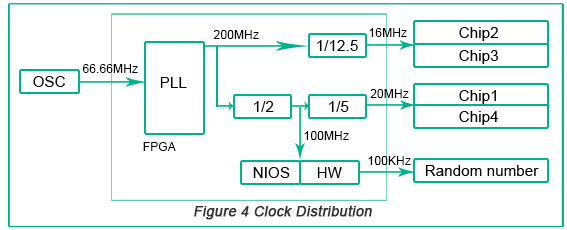

Dans la carte cryptographique à haute vitesse, le FPGA obtient une horloge de 66,66 MHz via l’oscillateur à quartz sur le PCB. Après une boucle avec les verrous internes du FPGA, une horloge de base de 200 MHz est générée comme interface pour que les puces 2 et 3 utilisent cette horloge. Ensuite, une horloge de 100 MHz est fournie par le circuit interne de division de fréquence en tant que cœur logiciel NiosII et horloge de fonctionnement du circuit matériel à l’intérieur du FPGA. La fréquence divisée de 16 MHz est l’horloge de fonctionnement des puces 2 et 3, tandis que la fréquence divisée de 20 MHz est l’horloge de fonctionnement des puces 1 et 4. La distribution de l’horloge est présentée sur la Figure 4 ci-dessous.

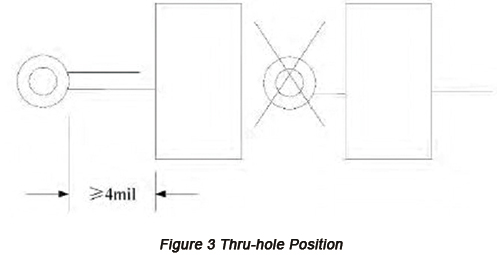

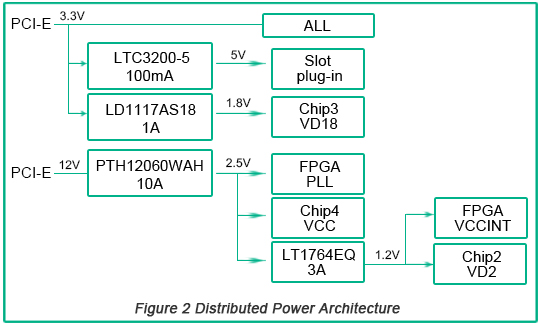

La transmission de signaux à haute vitesse entre le slot PCIE et le PC est réalisée par la carte cryptographique haute vitesse au moyen d’un routage en paires différentielles afin d’éviter les problèmes liés à l’intégrité du signal. De manière générale, aucun fil de masse n’est placé entre les signaux de paires différentielles, faute de quoi l’effet de couplage entre les signaux de paires différentielles serait détruit. Après le routage des signaux de paires différentielles, du cuivre est disposé autour des signaux haute vitesse du PCB et tout l’espace libre est entièrement rempli de fils de masse afin d’augmenter la capacité CEM du circuit. La clé deRoutage de PCBconsiste à maintenir la symétrie des paires différentielles. Si la longueur des paires différentielles n’est pas compatible, la précision de la lecture et de l’écriture des données sera affectée et le débit de transmission des données diminuera. Afin de garantir la validité de la lecture des données par le système sur une même période, la différence de retard entre les signaux différentiels doit être maintenue dans une plage autorisée et la longueur du routage doit être strictement identique. Par conséquent, un routage en forme de serpent peut être appliqué pour résoudre ce problème en ajustant le délai. Dans cette conception, la communication est réalisée entre le PC et la carte cryptographique via PCIE, et l’émission et la réception des signaux à haute vitesse sont mises en œuvre par des signaux en paire différentielle, avec la longueur du routage sur le PCB contrôlée dans une limite de 25 mil. Le schéma de correspondance de la longueur du routage en forme de serpent est illustré à la Figure 5.