Le contexte actuel, rapide et dynamique, dans le monde de l’électronique exige plus que jamais quePCA/PCBAet les conceptions de circuits intégrés soient fiables et fonctionnelles. À mesure que les technologies et les dispositifs se développent à un rythme rapide, en mettant l’accent sur la satisfaction efficace de besoins complexes émergents avec l’IoT, l’IA et la 5G, une pratique axée sur les résultats comme la conception pour la testabilité (DFT) joue un rôle essentiel. À travers cet article, il sera exploré comment la DFT peut être réalisée à l’aide d’outils et de techniques avancés.

Pertinence croissante de la DFT

La conception pour la testabilité, ou DFT (Design for Testability), est un domaine qui se concentre sur l’intégration de fonctionnalités de test dans les conceptions de PCBA et les conceptions de circuits intégrés (IC). Les tests DFT permettent de réduire considérablement les temps de test et d’améliorer la couverture des défauts, tout en diminuant les coûts. À mesure que les conceptions de circuits intégrés deviennent plus complexes en raison des avancées des technologies de procédé 3 nm et des conceptions comptant plusieurs milliards de transistors, la DFT est devenue un domaine essentiel.

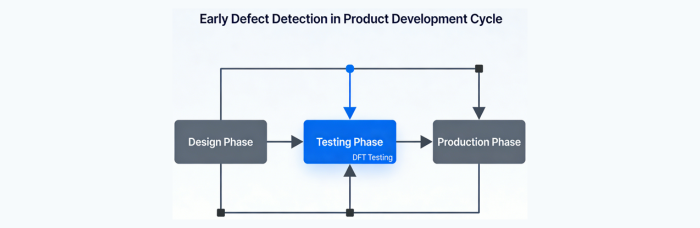

Détection de pannes précoce et efficace

Il serait difficile d’identifier des avantages plus essentiels associés à la DFT que son applicabilité à l’identification des défauts de production austades précoces du développement de produitEn identifiant ces défauts à un stade précoce, il devient facile pour les producteurs de remédier à ces problèmes sans procéder à des refontes, ce qui se traduit ainsi par une grande satisfaction des clients.

Tests efficaces pour des conceptions complexes et à haute densité

Les produits électroniques contemporains comprennent généralement des composants étroitement regroupés avec des opérations à haute vitesse. Ceux-ci posent des défis supplémentaires aux procédures de test conventionnelles. Les techniques de DFT facilitent l’accès aux points de test critiques et améliorent les fonctions de diagnostic. Elles rendent possible l’exécution de tests sur des conceptions complexes.

Réduire les échappées de tests

Bien qu’aucune méthode de test ne garantisse une couverture de défauts à 100 %, la DFT réduit considérablement la probabilité d’échappements de test. Les échappements de test se produisent lorsque des produits défectueux ne sont pas détectés lors de l’étape de test. La réduction de ces occurrences contribue à éviter des réparations coûteuses et à assurer une fiabilité supérieure des produits.

Méthodes DFT avancées pour 2025 et perspectives d’avenir

DFT hiérarchique

La DFT hiérarchique aide à gérer des conceptions de circuits intégrés (CI) très volumineuses. La DFT hiérarchique décompose les grandes conceptions de CI en blocs plus faciles à gérer. Elle permet de tester plusieurs blocs en parallèle, réduisant ainsi considérablement la quantité de données requises et le temps de test. Elle s’avère très utile pour tester de grands CI contenant des milliards de transistors.

DFT conscient de l’énergie

Les méthodes tenant compte de la consommation d’énergie jouent un rôle essentiel dans les tests, car elles aident à éviter la violation des contraintes de puissance optimales. De plus, elles revêtent une importance particulière pour les conceptions alimentées par batterie, notamment les objets connectés (IoT) et les processeurs mobiles.

Test à vitesse réelle

Les tests à vitesse nominale, courants dans les technologies haut débit comme la 5G, impliquent des sections d’auto-test intégré (BIST) fonctionnant à pleine vitesse opérationnelle. Les tests à vitesse nominale aident à détecter les défauts liés au minutage, qui pourraient avoir été manqués à des vitesses de test plus lentes. Ils garantissent ainsi que le composant fonctionnera comme il se doit dans son environnement d’utilisation optimal.

Application des technologies DFT contemporaines

D’ici 2025, le rôle des solutions DFT modernes devient impératif, intégrant l’automatisation, l’intelligence artificielle et les fonctionnalités cloud dans les tests :

Insertion automatique de DFTLa tâche d’interconnexion de la chaîne de scan et des points de test est automatisée, éliminant ainsi toute possibilité d’erreur. Cela réduit la durée du projet.

Analyse des pannes basée sur l’IA :Les outils d’IA utilisent des conceptions pour prédire les régions susceptibles de présenter des défauts et ainsi améliorer considérablement la couverture des défauts.

Simulation de test cloud :Les clouds permettent d’effectuer des simulations impliquant un grand nombre de tests sans nécessiter d’équipements coûteux, car plusieurs opérations peuvent être réalisées simultanément, ce qui réduit ainsi les temps de simulation.

Génération automatique de modèles de test

Les outils ATPG sont essentiels pour répondre aux exigences élevées de couverture de fautes, comme c’est le cas dans les conceptions denses. Ces outils génèrent automatiquement des vecteurs pour tester différents types de fautes. Par conséquent, ils offrent des capacités de test complètes, même pour des conceptions complexes.

Intégration du script de flux de test

Les scripts d’automatisation des processus impliquant la DFT, qui sont intégrés dans le flux global de conception, depuis la synthèse jusqu’au placement-routage, contribuent à réduire les itérations de conception et à mettre un produit plus rapidement sur le marché.

Surveillance des tests en temps réel

Les systèmes de surveillance automatisés offrent aux membres de l’installation un retour d’information en temps réel pendant les tests, afin qu’ils puissent s’adapter et apporter des modifications sur-le-champ. Cela éliminera le temps perdu en débogage et en analyse des défaillances à grande échelle.

Meilleures pratiques pour la mise en œuvre de la DFT

La mise en œuvre efficace du DFT nécessite un ensemble de bonnes pratiques pouvant être formulées pour faire face aux défis posés par les conceptions électroniques avancées d’aujourd’hui :

Intégrer tôt :L’intégration de la planification DFT aux processus de conception initiaux réduit les coûts liés à la refonte et garantit que la planification DFT répond aux critères de conception.

Optimiser le temps et le coût des tests :Des méthodes de compression des données de test et de test en parallèle sont employées pour optimiser les coûts et les délais de test.

Utiliser les normes de l’industrie :Utilisez des normes comme l’IEEE 1149.1 (JTAG) pour les tests de scan de frontière. Les normes industrielles facilitent les tests et le débogage.

Faciliter le travail d’équipe :Il favorise la coopération entre les équipes de conception et de test pour une optimisation plus aisée du DFT. Il aborde les problèmes dans une perspective globale et réduit le temps de résolution des problèmes de jusqu’à 30 %.

Surmonter les défis de la DFT

Bien que la DFT présente des avantages, sa mise en œuvre dans les conceptions modernes comporte des défis, comme indiqué ci-dessous :

Gestion des volumes de données de test :À mesure que les conceptions augmentent, la taille des données de test augmente également. Utilisez des algorithmes de compression de données et des services cloud pour gérer efficacement de grands volumes.

Équilibrer la couverture de test et la consommation d’énergie :Un taux de couverture de tests élevé entraîne une forte consommation d’énergie. Utilisez des méthodes de test économes en énergie qui vous permettent de maintenir la sécurité tout en restant dans des niveaux de consommation d’énergie acceptables.

Vérification de conceptions hétérogènes :Les puces à semi-conducteurs modernes sont de plus en plus susceptibles, par rapport aux conceptions plus anciennes, d’intégrer des composants numériques, analogiques et RF au sein d’une seule puce. Pour vérifier efficacement ces conceptions, les professionnels de l’industrie s’appuient sur des outils et des méthodes de solution DFT pour signaux mixtes.

À mesure que nous avançons dans une ère où le progrès technologique rapide devient plus marqué, l’apprentissage des méthodes avancées de DFT et de leur utilisation efficace devient impératif pour les entreprises qui cherchent à rester à la pointe du monde de l’électronique, hautement concurrentiel. En tirant parti des méthodes de planification en amont et en utilisant des technologies et des outils collaboratifs et avancés, il devient possible pour les experts d’en tirer des bénéfices maximums et d’obtenir des délais de transition plus efficaces ainsi qu’une meilleure rentabilité.

Chez PCBCart, nous nous engageons à vous fournir des services de production et d’assemblage de classe mondiale, tout en respectant les normes de qualité les plus strictes. Nous disposons de connaissances et d’une expertise approfondies qui garantiront que vos conceptions de PCBA et de circuits intégrés non seulement répondent aux normes du marché, mais les surpassent, de sorte que vous créerez quelque chose de véritablement remarquable et couronné de succès. Qu’il s’agisse des technologies IoT, IA ou 5G, aucun défi ne sera trop grand lorsque vous donnerez vie à vos conceptions de nouvelle génération grâce à notre précision et notre qualité inégalées. Laissez-nous vous aider dès aujourd’hui avec une consultation et un prix compétitif pour vos solutions électroniques révolutionnaires.

Obtenez un devis instantané pour un assemblage de PCB de haute qualité

Ressources utiles

•Inspection optique automatisée

•Inspection automatisée par rayons X

•Méthodes d’inspection de l’assemblage de circuits imprimés (PCB)

•Essai électrique

•Premier article

•Vérification DFM gratuite