Al momento, il rapido sviluppo della tecnologia Internet assiste alla massiccia applicazione di email, pagamenti online e comunicazioni personali. In questo contesto, la sicurezza delle informazioni è diventata un tema di ricerca cruciale in tutto il mondo. La tecnologia PKI (Public Key Infrastructure) fornisce servizi di sicurezza utilizzando la teoria e la tecnologia delle chiavi pubbliche. La tecnologia PCIE (Peripheral Component Interface Express) ha trovato ampia applicazione nei dispositivi ad alta velocità come standard di bus di I/O di terza generazione che adotta la trasmissione seriale dei dati e la tecnologia di interconnessione punto a punto. Nel campo della progettazione di sistemi digitali, una frequenza di clock relativamente elevata comporta alcuni problemi dal punto di vista dell’integrità del segnale, dell’integrità della potenza e della diafonia, e la progettazione tradizionale dei PCB non riesce a soddisfare i requisiti di stabilità del sistema.

Questo articolo propone uno schema di progettazione PCB per una scheda di password ad alta velocità basata su PCIE, sfruttando i vantaggi della trasmissione seriale ad alta velocità di PCIE.

Schema di progettazione generale

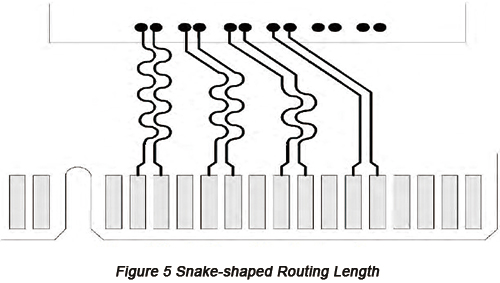

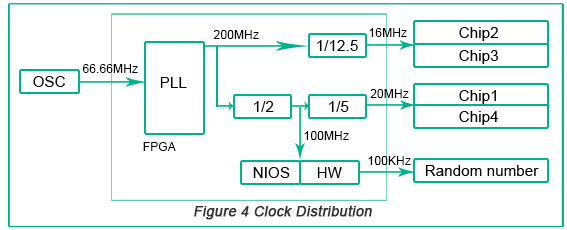

Nel presente progetto viene utilizzato il chip FPGA EP4CGX50CF23C6N appartenente alla serie Cyclone IV GX progettata da Altera, che integra il modulo IP hard core PCIE e realizza la progettazione di una scheda di cifratura per la trasmissione di dati ad alta velocità a 4 canali. Quattro tipi di chip, chip 1, chip 2, chip 3 e chip 4, sono in grado di implementare rispettivamente gli algoritmi SM1, SM2/SM3, SM4 e SSF33 e di realizzare le funzionalità di inizializzazione della scheda di cifratura, gestione delle chiavi segrete, backup e ripristino e gestione delle autorizzazioni. Le schede di cifratura sono utilizzate nei PC, collegate alla scheda madre dei PC tramite lo slot PCIE e controllate dai PC. L’IP hard core nell’FPGA viene utilizzato per implementare il PCIE, consentendo la comunicazione tra il core PCIE, la cache SRAM e il modulo di controllo. In qualità di centro di controllo, NiosII implementa la funzione del software della scheda di cifratura. Nel frattempo, un ulteriore chip di cifratura realizza la comunicazione tra ciascun modulo di interfaccia e la scheda di cifratura. La struttura hardware della scheda di cifratura è illustrata nella Figura 1 seguente.

Progettazione PCB ad alta velocità

• Impilamento e layout

La progettazione dello stackup è il problema più significativo che deve essere preso in considerazione e una progettazione ragionevole dello stackup può inibire le radiazioni EMI (Interferenze Elettromagnetiche), rendendo la tensione transitoria sul piano di alimentazione o sullo strato di massa il più piccola possibile e schermando il campo elettromagnetico del segnale e dell’alimentazione. In generale, nei progetti di circuiti digitali ad alta velocità si utilizzano schede multistrato e alimentazioni multiple.Progettazione dell’impilamento PCBè implementato sulla base di elementi completi, inclusa la frequenza di clock del circuito,Costo di fabbricazione PCB, densità dei pin, periodo di produzione e affidabilità. Inoltre, gli strati del circuito stampato multistrato devono essere mantenuti simmetrici e il numero di strati deve essere pari, poiché un design di impilamento asimmetrico causerà l’imbarcamento delle schede. La scheda password progettata in questo articolo è collegata al PC tramite lo slot PCIE e le dimensioni e la forma del circuito stampato sono fisse, con un’altezza di circa 67 mm e una lunghezza di circa 174 mm, configurando i pin dell’interfaccia PCIE X4 nella parte inferiore. A causa dell’elevata densità dei componenti e dell’elevato spessore delle piste, il numero di strati del PCB è stato scelto pari a 6, con la seguente distribuzione: strato di segnale, strato di alimentazione, strato di segnale, strato di alimentazione, strato di massa, strato di segnale. Questo design contiene 3 strati di segnale, 1 strato di massa e 2 strati di alimentazione, fornendo l’ambiente richiesto per l’integrità del segnale.

Dopo la determinazione dell’impilamento del PCB, occorre procedere alla suddivisione in gruppi dei componenti e al layout. Per prima cosa, la posizione dei componenti deve essere programmata in accordo con le dimensioni e il pattern del PCB, tenendo in considerazione il collegamento delle linee, la suddivisione funzionale e l’ordine e l’estetica tra i componenti. Successivamente, i componenti devono essere distribuiti in modo ragionevole in base ai diversi livelli di tensione dei componenti, così da rendere i cavi di alimentazione il più corti possibile, il che consente di ridurre le interferenze del rumore di alimentazione e aumentare la stabilità dell’alimentazione. Il posizionamento dei chip deve prestare attenzione alla relazione tra il circuito ausiliario e il chip stesso e al posizionamento del cristallo dietro i pin di clock. I componenti ad alto rumore devono essere evitati intorno al cristallo e devono essere vicini ai loro componenti di pilotaggio. Inoltre, il posizionamento di ciascun pin di alimentazione e di segnale dei chip deve essere considerato, con le loro posizioni e direzioni regolate in base alle linee collegate. Poiché il rapporto tra lunghezza e larghezza della password card è superiore a 2:1 e le posizioni dello slot PCIE, dei fori di fissaggio e dei LED di indicazione sono fisse, nel layout dei componenti occorre considerare prima il posizionamento dei componenti fissi. Inoltre, a causa del gran numero di linee di collegamento tra i componenti e l’FPGA, il layout dei componenti deve essere realizzato avendo l’FPGA come centro, prima di definire le posizioni degli altri componenti, in modo che lo spazio superiore e inferiore del PCB possa essere utilizzato in modo efficace, lasciando sufficiente spazio tra i componenti e tra i componenti e i fori di posizionamento.

• Progettazione di alimentazione

Inprogettazione di circuiti stampati ad alta velocità, la progettazione del sistema di alimentazione è direttamente correlata al successo dell’intero sistema. Il rumore generato da alimentazione e massa deve essere ridotto al minimo per garantire l’affidabilità dei prodotti. L’applicazione dello schema di distribuzione dell’alimentazione nel metodo a strati si riferisce al fatto che l’alimentazione è distribuita attraverso il metallo sull’intero strato, riducendo l’impedenza e il rumore dell’alimentazione e aumentando l’affidabilità. Poiché nel PCB sono coinvolte più alimentazioni, si dovrebbe applicare una progettazione multistrato di alimentazione, in grado di eliminare l’interferenza di accoppiamento dovuta all’impedenza comune come anello di rumore. L’applicazione della capacità di disaccoppiamento è in grado di risolvere il problema dell’integrità dell’alimentazione, poiché il condensatore può essere posizionato solo sullo strato inferiore o superiore del PCB; sulla base di ciò, i conduttori che collegano i condensatori di disaccoppiamento devono essere corti e larghi. In base al materiale del chip, è possibile calcolare la corrente che attraversa le linee di alimentazione e determinare la larghezza delle piste. Più le piste sono larghe, maggiore è la corrente che possono trasportare. La formula sperimentale è illustrata come:W(larghezza linea: mm) ≥L(mm/A) xIo(attuale: A)

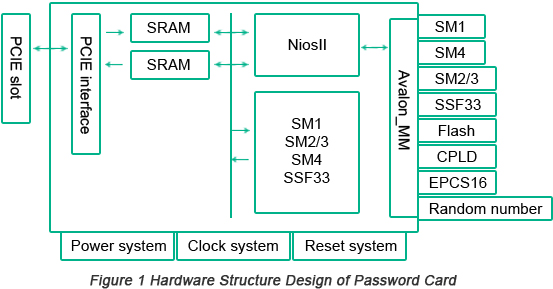

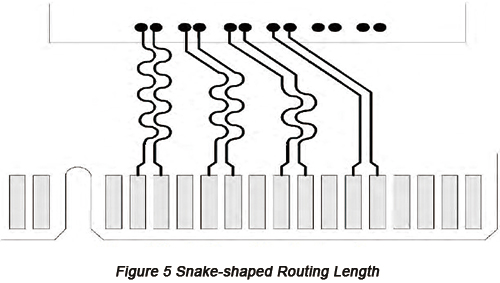

Sulla PCB, più alimentazioni ottengono uno o due tipi di potenza dalla scheda di alimentazione tramite la backplane e l’alimentazione viene poi convertita in altre tensioni richieste dai componenti. La conversione dell’alimentazione è suddivisa in due architetture: architettura di alimentazione centralizzata e architettura di alimentazione distribuita. La prima si riferisce a un’alimentazione fornita da un’unica sorgente indipendente e poi convertita in tutti i tipi di tensioni richieste, mentre la seconda si riferisce a una conversione di potenza a più stadi. Poiché l’architettura di alimentazione centralizzata presenta gli svantaggi di costi elevati e grande area occupata sulla PCB, in questo progetto viene adottata l’architettura di alimentazione distribuita. La scheda crittografica utilizza 6 alimentazioni: 12 V, 3,3 V, 5 V, 2,5 V, 1,2 V e 1,8 V. Questo progetto parte dall’impiego delle alimentazioni a 3,3 V e 12 V presenti nello slot PCIE; quindi, l’alimentazione a 3,3 V è in grado di generare le alimentazioni a 5 V e 1,8 V tramite un chip di conversione di tensione, fornendo alimentazione al modulo plug-in e al chip 3. Successivamente, l’alimentazione a 12 V viene convertita in 2,5 V per alimentare l’FPGA e il chip 4. Infine, l’alimentazione a 2,5 V viene convertita in 1,2 V per alimentare l’FPGA e il chip 2. L’architettura di alimentazione distribuita della scheda crittografica è mostrata nella Figura 2 seguente.

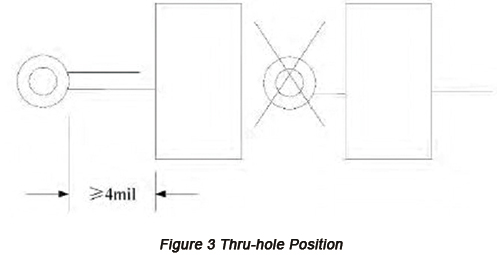

• Design a foro passante

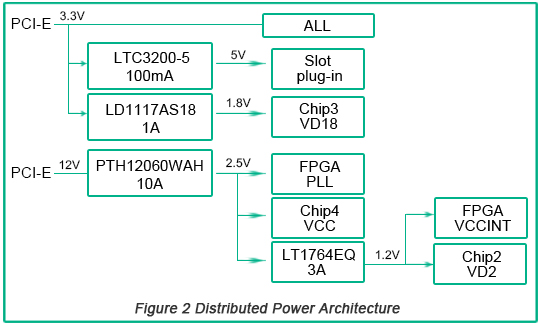

Nel processo di progettazione del layout perPCB multistratocon un'elevata densità, devono essere applicati fori passanti, che trasmettono il segnale da uno strato all'altro per fornire comunicazione elettrica tra gli strati. Il progetto della posizione dei fori passanti deve essere realizzato con molta attenzione. I fori passanti non devono essere posizionati sul pad e una sola pista stampata può essere utilizzata per la connessione, altrimenti si generano problemi come effetto tombstone e insufficiente saldatura. La soldermask deve essere applicata sul pad del foro passante con una distanza impostata a 4 mil e i fori passanti non devono essere posizionati al centro del pad per i componenti a chip sul lato di saldatura. La posizione dei fori passanti è illustrata nella Figura 3 qui sotto.

Inoltre, la posizione dei fori passanti non deve essere troppo vicina al goldfinger, il cui lato di inserzione dovrebbe includere uno smusso. Per consentire l’inserimento delle schede a circuito nello slot PCIE, è possibile progettare uno smusso di (1~1,5)x45° sui due bordi laterali della scheda di inserzione.

• Instradamento di segnali ad alta velocità

Nel processo di instradamento, la distribuzione deve essere regolata in modo ragionevole per ridurre al minimo le linee di collegamento, così da diminuire la diafonia. Nel processo di instradamento di segnali digitali ad alta velocità, il livello di segnale vicino a un livello di alimentazione multipla dovrebbe essere il più lontano possibile dalla superficie di riferimento di alimentazione, al fine di evitare la generazione del percorso di ritorno da parte della corrente di segnale.

Poiché la frequenza del segnale di clock nei circuiti ad alta velocità è relativamente elevata, il jitter, la deriva e la deformazione influiscono notevolmente sul sistema, per cui il progetto PCB ad alta velocità richiede una minima interferenza sulle forme d’onda dei segnali. Pertanto, il problema della distribuzione e del routing del clock deve essere considerato per primo. Il routing deve essere applicato ai segnali di clock ad alta velocità e il tracciato delle linee del segnale di clock principale deve essere il più corto possibile, rettilineo e privo di fori passanti e di parti di alimentazione, in modo da prevenire il crosstalk tra clock e alimentazione. Quando più clock con frequenze diverse sono utilizzati sullo stesso PCB, due linee di clock con frequenze differenti non devono essere mantenute parallele. Tuttavia, per più componenti che utilizzano segnali di clock con la stessa frequenza, la rete può essere distribuita a ragnatela, ad albero o a diramazione.

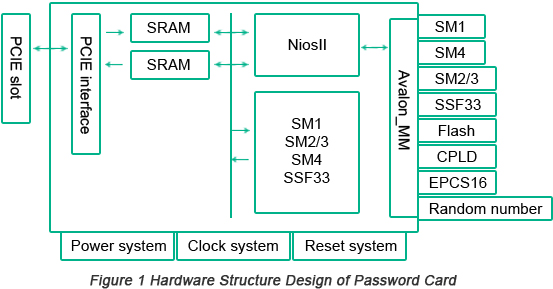

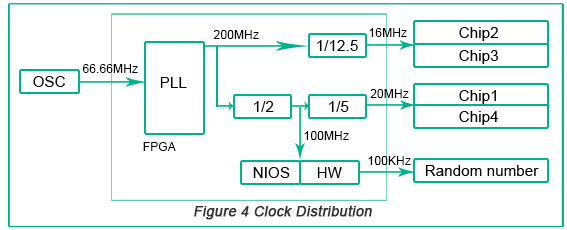

Nella scheda crittografica ad alta velocità, l’FPGA ottiene un clock a 66,66 MHz tramite il cristallo oscillatore sul PCB. Dopo il loop con i blocchi di lock interni all’FPGA, viene generato un clock di base a 200 MHz come interfaccia per il funzionamento a clock del chip 2 e del chip 3. Successivamente, un clock a 100 MHz viene fornito dal circuito interno di divisione di frequenza come softcore NiosII e come clock di lavoro del circuito hardware interno all’FPGA. La frequenza divisa a 16 MHz è il clock di lavoro per il chip 2 e il chip 3, mentre la frequenza divisa a 20 MHz è il clock di lavoro per il chip 1 e il chip 4. La distribuzione del clock è mostrata nella Figura 4 qui sotto.

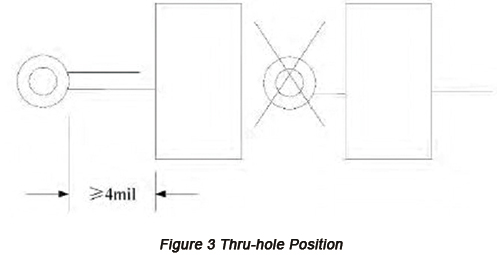

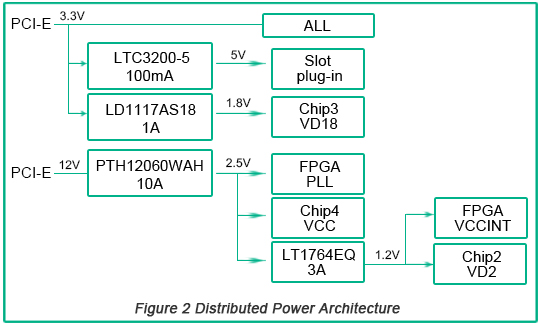

La trasmissione ad alta velocità del segnale tra lo slot PCIE e il PC è realizzata dalla scheda crittografica ad alta velocità tramite instradamento a coppie differenziali per evitare problemi relativi all’integrità del segnale. In generale, non vengono posizionati conduttori di massa tra i segnali della coppia differenziale, altrimenti verrebbe compromesso l’effetto di accoppiamento tra i segnali della coppia differenziale. Dopo l’instradamento dei segnali a coppie differenziali, viene posizionato rame attorno ai segnali ad alta velocità del PCB e lo spazio libero viene completamente riempito con conduttori di massa per aumentare la capacità EMI del circuito. La chiave diInstradamento PCBè mantenere la simmetria delle coppie differenziali. Se la lunghezza delle coppie differenziali non è compatibile, l’accuratezza della lettura e scrittura dei dati sarà influenzata e la velocità di trasmissione dei dati diminuirà. Per garantire la validità del sistema nella lettura dei dati nello stesso periodo, la differenza di ritardo tra i segnali differenziali deve essere mantenuta entro un intervallo consentito e la lunghezza del routing deve essere rigorosamente identica. Pertanto, il routing a forma di serpentina può essere applicato per risolvere questo problema regolando il ritardo temporale. In questo progetto, la comunicazione è implementata dal PC tramite PCIE e scheda crittografica e la trasmissione e la ricezione di segnali ad alta velocità sono realizzate tramite segnali a coppia differenziale con la lunghezza del routing sul PCB controllata entro 25 mil. Il diagramma di corrispondenza della lunghezza del routing a serpentina è illustrato in Figura 5.