現在、インターネット技術の急速な発展により、電子メール、オンライン決済、個人間通信が大規模に利用されている。このような背景の下、情報セキュリティは世界的に重要な研究テーマとなっている。PKI(Public Key Infrastructure:公開鍵基盤)技術は、公開鍵理論および技術を用いてセキュリティサービスを提供する。PCIE(Peripheral Component Interface Express)技術は、シリアルデータ伝送およびポイント・ツー・ポイント接続技術を適用した第3世代I/Oバス標準として、高速デバイスに広く利用されている。デジタルシステム設計の分野では、比較的高いクロック周波数により、信号完全性、電源完全性およびクロストークの観点からいくつかの問題が生じ、従来のPCB設計ではシステムの安定性要件を満たすことができない。

本稿では、PCIE の高速シリアル伝送の利点に基づき、ハイスピードパスワードカード向けの PCIE ベース PCB 設計方案を提示する。

全体設計方案

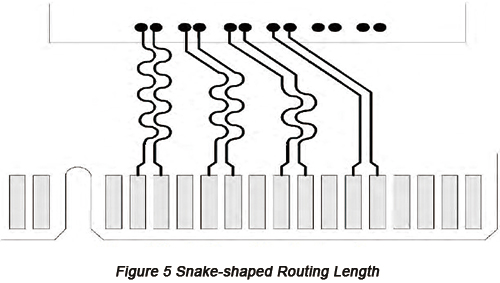

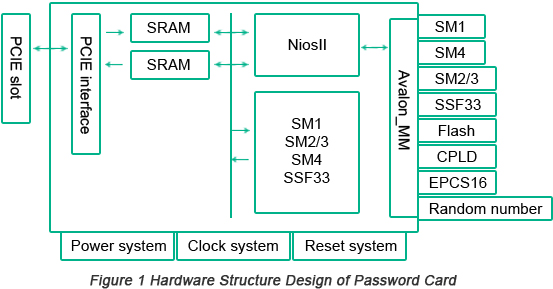

本設計では、Altera が設計した Cyclone IV GX シリーズに属する FPGA チップ EP4CGX50CF23C6N を採用し、PCIE IP ハードコアモジュールを統合して、4 系統の高速データ伝送パスワードカード設計を実現している。チップ1、チップ2、チップ3、チップ4 の 4 種類のチップは、それぞれ SM1、SM2/SM3、SM4、SSF33 のアルゴリズムを実装し、パスワードカードの初期化、秘密鍵管理、バックアップおよびリカバリ、権限管理といった機能を実現することができる。パスワードカードは PC に適用され、PCIE スロットを介して PC のマザーボードに接続され、PC によって制御される。FPGA 内の IP ハードコアは PCIE を実装するために用いられ、PCIE コアと SRAM キャッシュおよび制御モジュールとの通信を実現する。制御センターとして、NiosII はパスワードカードソフトウェアの機能を実装する。一方で、付加されたパスワードチップは、各インターフェースモジュールとパスワードカードとの通信を実現する。パスワードカードのハードウェア構造設計を図1に示す。

高速PCB設計

・スタックアップおよびレイアウト

スタックアップ設計は、考慮すべき最も重要な問題であり、合理的なスタックアップ設計によってEMI(電磁干渉)放射を抑制し、電源プレーンやグラウンド層上の過渡電圧を可能な限り小さくし、信号および電源の電磁界をシールドすることができる。一般的に、高速デジタル回路設計では多層基板および複数の電源が用いられる。PCBスタッキング設計回路クロック周波数を含む包括的な要素に基づいて実装されており、PCB製造コスト、ピン密度、製造期間および信頼性である。さらに、多層基板の層構成は対称に保ち、層数は偶数にする必要がある。これは、非対称な積層設計が基板の反りを引き起こすためである。本稿で設計したパスワードカードは、PCIEスロットを介してPCと接続され、回路基板のサイズと形状は高さ約67mm、長さ約174mmで固定され、下部にPCIE X4インターフェースピンを配置している。高い部品実装密度と厚い配線の結果、PCBの層数は6層とし、信号層、電源層、信号層、電源層、グラウンド層、信号層という構成とした。この設計は、3つの信号層、1つのグラウンド層および2つの電源層を含み、信号完全性に必要な環境を提供する。

PCBスタッキングが決定した後、コンポーネントグループとレイアウトを実装する必要がある。まず、コンポーネントの配置位置は、配線接続、機能分割、およびコンポーネント間の整然さと美観を考慮しつつ、PCBの寸法とパターンに従って設定しなければならない。その後、電圧グレードの異なるコンポーネントに応じて合理的に分配し、電源ラインをできるだけ短くすることで、電源ノイズの干渉を低減し、電源の安定性を高めることができる。チップの配置においては、その補助回路とチップ本体との関係、およびクロックピン背面への水晶発振子の配置に注意する必要がある。高ノイズコンポーネントは水晶発振子の周囲への配置を避け、駆動コンポーネントの近くに配置すべきである。さらに、各チップの電源ピンおよび信号ピンの配置については、接続ラインに基づいてその位置と方向を調整する必要がある。パスワードカードの長さと幅の比率が2:1を超え、PCIEスロット、取付穴およびインジケータLEDの位置が固定されているため、コンポーネントレイアウトでは、まず固定コンポーネントのレイアウトを優先的に検討しなければならない。加えて、コンポーネントとFPGA間の接続ラインが多数存在する結果、コンポーネントレイアウトは、他のコンポーネントの位置決めに先立ち、FPGAを中心として行うことで、PCBの表裏のスペースを有効に活用し、コンポーネント同士およびコンポーネントと位置決め穴との間に十分な空間を確保できるようにすべきである。

・電源設計

中で高速回路基板設計電源システムの設計は、システム全体の成否に直接関係している。製品の信頼性を確保するためには、電源およびグラウンドによって発生するノイズを最小限に抑えなければならない。層構成方式における電源分配方式の適用とは、電源を層全体の金属を通して分配することを指し、これにより電源インピーダンスとノイズを低減し、信頼性を向上させることができる。PCB では複数の電源が関係するため、多電源層設計を適用し、ノイズループとしての共通インピーダンス結合干渉を除去できるようにする必要がある。デカップリング容量の適用は、電源インテグリティの問題を解決することができる。コンデンサは PCB のボトム層またはトップ層にしか配置できないため、これに基づき、デカップリングコンデンサに接続する配線は短く太くする必要がある。チップの仕様に応じて、電源ラインを流れる電流を計算し、リード線の幅を決定することができる。リード線は幅が広いほど多くの電流を流すことができる。実験式は次のように示される。W(線幅:mm)≥L(mm/A) x私(現在:A)

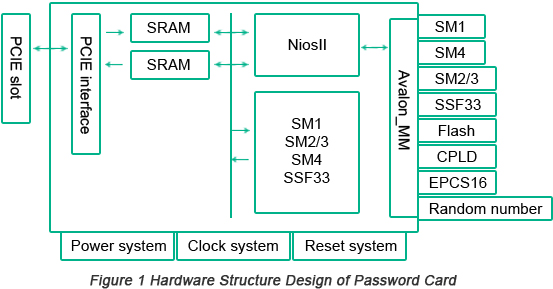

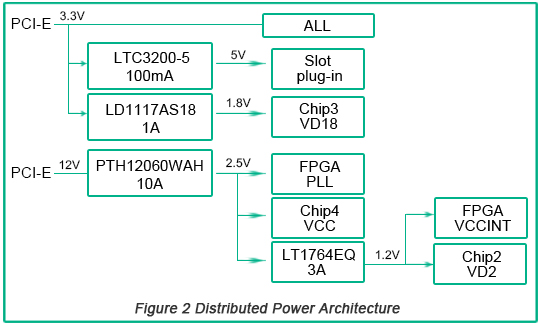

PCB 上の複数の電源は、バックボードを介して電源ボードから 1 種類または 2 種類の電源を取得し、その電源をコンポーネントが必要とする他の電源に変換する。電源の変換は、集中電源アーキテクチャと分散電源アーキテクチャの 2 つの構成に分けられる。前者は、独立した電源から電力を供給し、その後あらゆる種類の必要な電源に変換する方式を指し、後者は多段階の電源変換を指す。集中電源アーキテクチャはコストが高く、PCB 面積も大きいという欠点があるため、本設計では分散電源アーキテクチャを採用している。暗号カードは 12V、3.3V、5V、2.5V、1.2V、1.8V の 6 種類の電源を扱う。本設計では、まず PCIE スロットにおける 3.3V と 12V 電源から始まり、その後 3.3V 電源が電圧変換チップを通じて 5V 電源と 1.8V 電源を生成し、プラグインおよびチップ 3 に電力を供給する。次に、12V 電源を 2.5V 電源に変換し、FPGA およびチップ 4 に電力を供給する。最後に、2.5V 電源を 1.2V 電源に変換し、FPGA およびチップ 2 に電力を供給する。暗号カードの分散電源アーキテクチャを図 2 に示す。

・スルーホール設計

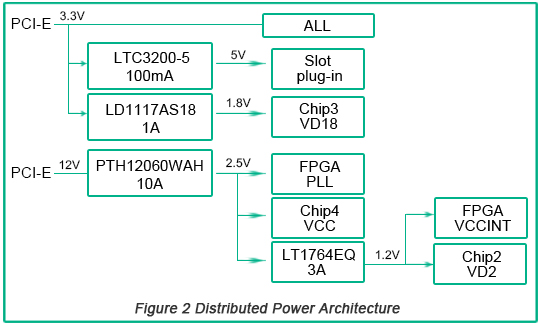

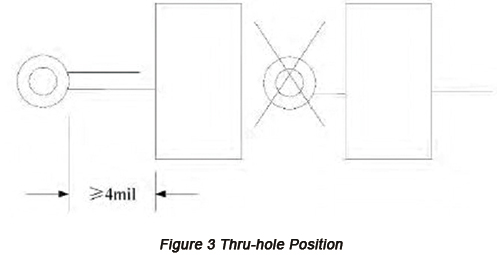

デザインレイアウトの作成過程において多層プリント基板高密度の場合、層間で信号を伝達し電気的な接続を行うためにスルーホールを適用する必要があります。スルーホールの位置設計は細心の注意を払って行わなければなりません。スルーホールはパッド上に配置してはならず、1 本のプリント配線で接続できるようにしなければなりません。そうしないと、ツームストーンやはんだ不足といった問題を引き起こします。ソルダーレジストはスルーホールパッド上に塗布し、そのクリアランスは 4 mil に設定する必要があり、はんだ付け面のチップ部品のパッド中心にスルーホールを配置してはなりません。スルーホールの位置例を以下の図 3 に示します。

さらに、スルーホールの位置は、面取りを施す必要がある挿入側のゴールドフィンガーに近すぎてはなりません。回路基板をPCIEスロットに挿入できるようにするため、挿入用基板の両側縁には (1~1.5)×45° の面取りを設計することができます。

・高速信号配線

配線の過程では、結線を最小限にしてクロストークを低減できるよう、分配を合理的に調整する必要があります。高速デジタル信号の配線過程においては、信号層が複数の電源層に近接して配線される場合、信号電流によるリターンパスの発生を避けるために、電源リファレンス面から十分に離すべきです。

高速回路のクロック信号周波数は比較的高いため、ジッタやドリフト、波形の歪みがシステムに大きな影響を与えます。そのため、高速PCB設計では信号波形への干渉をできるだけ小さく抑える必要があります。したがって、まずクロックの配分と配線の問題を優先的に検討しなければなりません。高速クロック信号には適切な配線を行い、主クロック信号ラインの配線はできる限り短く、直線的にし、スルーホールや電源部を避けて、クロックと電源間のクロストークを防ぐ必要があります。異なる周波数の複数のクロックが同一のPCB上で使用される場合、異なる周波数を持つ2本のクロックラインを平行に走らせてはなりません。一方、同一周波数のクロック信号を使用する複数のコンポーネントに対しては、クロックネットワークをスパイダー型、ツリー型、ブランチ型などで分配することができます。

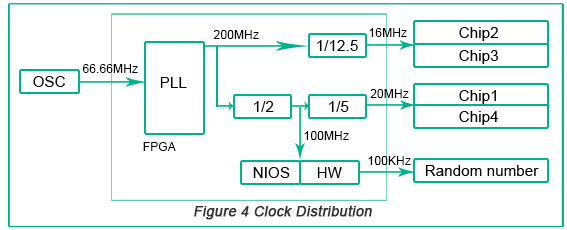

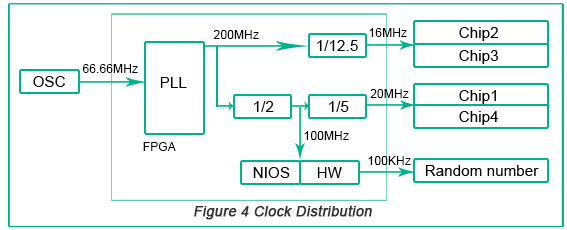

高速暗号カードでは、FPGA は PCB 上の水晶発振器から 66.66MHz のクロックを取得する。FPGA 内部の内蔵ロック回路でループ処理を行った後、チップ 2 およびチップ 3 の動作クロック用インターフェースとして 200MHz の基本クロックが生成される。さらに、内蔵の分周回路によって 100MHz のクロックが生成され、NiosII ソフトコアおよび FPGA 内部のハードウェア回路の動作クロックとして供給される。分周された 16MHz はチップ 2 およびチップ 3 の動作クロックであり、分周された 20MHz はチップ 1 およびチップ 4 の動作クロックである。クロックの分配は下の図 4 に示す。

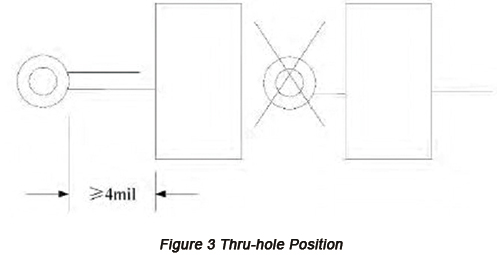

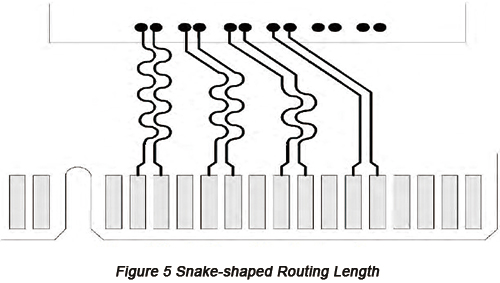

PCIEスロットとPC間の高速信号伝送は、高速暗号カードによって差動ペアルーティングの方式で実装され、信号完全性に関する問題を回避している。一般的に言えば、差動ペア信号の間にはグラウンド線は配置されない。そうしないと、差動ペア信号間の結合効果が損なわれてしまうからである。差動ペア信号の配線後、PCBの高速信号の周囲には銅箔が配置され、余剰スペースはグラウンドで完全に充填されて回路のEMI耐性を高めている。その要点はPCB配線は、差動ペアの対称性を維持することにある。差動ペアの長さが一致していない場合、データの読み書き精度に影響を及ぼし、データ伝送速度が低下する。同一周期内でのデータ読み取りの有効性を確保するためには、差動信号間の遅延差を許容範囲内に抑え、配線長を厳密に同一にする必要がある。したがって、この問題を解決するために、時間遅延を調整する手段としてスネーク配線を適用することができる。本設計では、PC と暗号カード間の通信は PCIE を介して実現され、高速信号の送受信は差動ペア信号によって行われる。PCB 配線長は 25mil 以内に制御されている。スネーク配線長のマッチング図を図5に示す。