現代のエレクトロニクス分野におけるこの急速かつダイナミックな状況においては、これまで以上に次のことが求められている。PCA/PCBAIC 設計が信頼性と機能性を備えたものとなるようにすることです。IoT、AI、5G によって新たに生じる複雑なニーズに効率的に対応することに焦点を当てつつ、技術やデバイスが急速に発展している中で、DFT(Design for Testability:テスト容易化設計)のような成果重視の手法は不可欠な役割を果たします。本記事を通じて、DFT を高度なツールや手法を用いてどのように実現できるかを探っていきます。

DFT の関連性の高まり

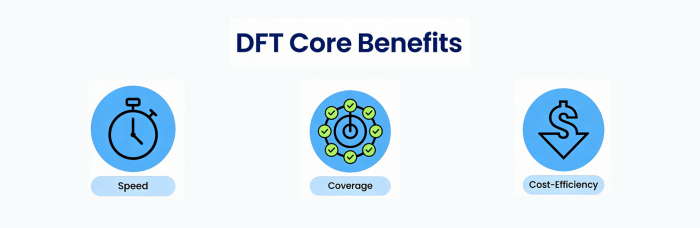

テスト容易化設計(DFT:Design for Testability)は、PCBA 設計および IC 設計にテスト機能を組み込むことに焦点を当てた分野です。DFT テストにより、テスト時間を大幅に短縮し、低コストでより高い故障検出率を実現できます。3nm プロセス技術の進歩や数十億トランジスタ規模の設計によって IC 設計がますます複雑になる中で、DFT は不可欠な分野となっています。

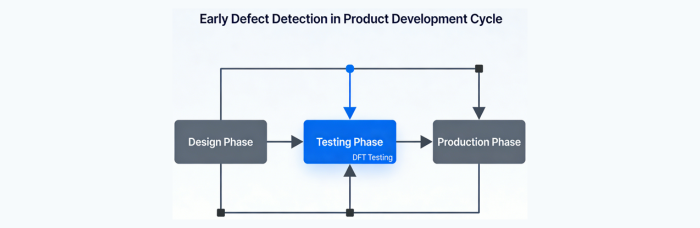

早期かつ効率的な故障検出

DFT に関連する、より本質的な利点を特定することは困難であり、それは生産上の欠陥を特定する際の適用性と比較した場合においてである製品開発の初期段階これらの欠陥を初期段階で特定することにより、製造者は再設計を行うことなくこれらの問題を容易に是正でき、その結果として高い顧客満足につながります。

複雑で高密度な設計の効果的なテスト

現代の電子製品には通常、高速で動作する高密度実装のコンポーネントが含まれています。これらは従来のテスト手順に対して新たな課題をもたらします。DFT 技術は、重要なテストポイントへのアクセスを容易にし、診断機能を向上させます。これにより、複雑な設計に対してテストを実施することが可能になります。

テスト漏れの削減

どのようなテスト手法であっても、故障を100%検出できるとは限りませんが、DFT によってテストエスケープの可能性は大幅に低減されます。テストエスケープとは、不良品がテスト工程で見逃されてしまうことを指します。これらの発生を減らすことで、高額な修理費用を防ぎ、製品の高い信頼性を確保することができます。

2025年の先端DFT手法と今後の展望

階層的DFT

階層型DFTは、非常に大規模なIC設計を扱うのに役立ちます。階層型DFTは、大規模なIC設計を、より扱いやすいチャンクに分解します。これにより、さまざまなチャンクを並列にテストできるため、必要なデータ量とテスト時間を大幅に削減できます。これは、数十億個のトランジスタを持つ大規模ICのテストに非常に有用であることが証明されています。

電力認識型DFT

省電力対応手法は、最適な電力制約の違反を回避するのに役立つため、テストにおいて極めて重要な役割を果たします。さらに、それらは IoT やモバイルプロセッサを含むバッテリ駆動設計に対して、特に重要な意味を持ちます。

アットスピードテスト

5G のような高速技術で一般的なアットスピードテストは、内蔵自己テスト(BIST)部が実際の動作速度と同じフルスピードで動作することを意味します。アットスピードテストは、低速でのテストでは見逃される可能性のあるタイミング関連の欠陥を検出するのに役立ちます。これにより、そのコンポーネントが最適な使用環境において本来のとおりに動作することが保証されます。

最新のDFT技術の適用

2025年までに、最新のDFTソリューションの役割は不可欠なものとなり、自動化、人工知能、クラウド機能をテストに取り入れるようになります。

自動DFT挿入スキャンチェーンとテストポイントの相互接続作業は自動化されており、これにより誤りの可能性が完全に排除されます。これによってプロジェクトの期間が短縮されます。

AI搭載型故障解析AI ツールは設計を活用して、故障が発生する可能性のある領域を予測し、それによって故障検出率を大幅に向上させます。

クラウドテストシミュレーション:クラウドを利用することで、多数のテストを伴うシミュレーションを高価な機器を必要とせずに実行でき、複数の処理を同時に行うことでシミュレーション時間を短縮できる。

テストパターン生成の自動化

ATPG ツールは、高集積設計で一般的な高い故障カバレッジ要件を実現するために不可欠です。これらのツールは、さまざまな故障タイプをテストするためのベクタを自動生成します。その結果、これらのツールは、複雑な設計に対しても包括的なテスト機能を提供します。

テストフロー スクリプト統合

合成から配置配線に至るまでの全体的な設計フローに組み込まれた、DFT を含むプロセスを自動化するためのスクリプトは、反復的な設計を削減し、製品をより迅速に市場へ投入するのに役立ちます。

リアルタイムテスト監視

自動監視システムは、テスト中に施設の担当者へリアルタイムのフィードバックを提供し、その場で適応して変更を加えられるようにします。これにより、大規模なデバッグや故障解析に費やされる無駄な時間が排除されます。

DFT 実装のベストプラクティス

効果的なDFTを実装するためには、今日の先進的な電子設計がもたらす課題に対処できるように策定された、一連のベストプラクティスが必要となる。

早期に統合するDFT 計画を初期設計プロセスと統合することで、再設計に伴うコストを削減し、DFT 計画が設計要件を満たすことを確実にします。

テスト時間とコストの最適化テストコストと時間を最適化するために、テストデータ圧縮および並列テスト手法が採用されています。

業界標準を使用することIEEE 1149.1(JTAG)のような規格を使用して、バウンダリスキャンテストを行いましょう。業界標準を用いることで、テストやデバッグが容易になります。

チームワークを促進するDFT の最適化を容易にするために、設計チームとテストチームの協調を促進します。全体的な観点から問題に対処し、課題の解決時間を最大 30% まで短縮します。

DFTの課題を克服する

DFT には利点がありますが、現代の設計に実装する際には、以下に示すような課題も伴います。

テストデータ量の扱い設計が増えるにつれて、テストデータのサイズも大きくなります。データ圧縮アルゴリズムやクラウドサービスを利用して、大量のデータを効果的に処理しましょう。

テストカバレッジと消費電力のバランス調整テストカバレッジが高いと、消費電力が増加します。許容可能な電力消費の範囲内で安全性を維持できる、省電力を意識したテスト手法を使用してください。

異種設計の検証最新の半導体チップは、旧来の設計と比べて、1つのチップ内にデジタル、アナログ、RFコンポーネントを含む可能性がますます高くなっています。これらの設計を効果的に検証するために、業界の専門家はミックスドシグナルDFTソリューションのツールと手法に依存しています。

急速な技術進歩がいっそう顕著になる時代へと進む中、DFT の高度な手法を効果的に活用することを学ぶことは、競争の激しいエレクトロニクス業界の最前線に立とうとする企業にとって不可欠になっています。初期計画手法を活用し、協調的かつ先進的な技術やツールを利用することで、専門家は最大限の利益を引き出し、より効率的な移行期間と高い費用対効果を実現することが可能になります。

PCBCart では、世界水準の製造および実装サービスを提供することに尽力しており、品質に関して最も厳格な基準を順守しています。私たちは豊富な知識と専門性を有しており、お客様の PCBA および IC 設計が市場基準に見合うだけでなく、それを上回ることを保証します。その結果、お客様は真に卓越し、成功する製品を生み出すことができます。IoT、AI、5G 技術に至るまで、次世代設計を具現化する際、当社の比類なき精度と品質によって、どのような課題も大きすぎることはありません。革新的な電子ソリューションのために、ぜひ本日ご相談いただき、競争力のあるお見積りをご提供させてください。