新世代の電子技術により、部品のエッジ速度はますます高速化しています。回路の動作速度の向上に伴い、PCB設計に対する要求もますます高くなっています。PCB設計の品質は、部品および回路全体の動作性能をも左右します。特に、コストやPCB面積、複合回路の機能性を総合的に考慮すると、EMI(電磁干渉)の発生源はますます多様化し、そのメカニズムも複雑になってきています。

PCB がショッピングカートに正常に追加されました

新世代の電子技術により、部品のエッジ速度はますます高速化しています。回路の動作速度の向上に伴い、PCB設計に対する要求もますます高くなっています。PCB設計の品質は、部品および回路全体の動作性能をも左右します。特に、コストやPCB面積、複合回路の機能性を総合的に考慮すると、EMI(電磁干渉)の発生源はますます多様化し、そのメカニズムも複雑になってきています。

EMI の主な要素には、電磁干渉源、伝搬経路、および干渉を受ける対象が含まれる。EMI の発生につながる要素が特定されたら、PCB 設計の過程で容易に解決できる要素と、部分的にしか解決できない要素を判別する必要がある。これにより、レイアウト、配線、およびグラウンディングの過程でそれらを考慮に入れることができる。

・レイアウト

〜の観点から言えばPCBレイアウトエリアは異なる機能に応じて区分する必要があります。さまざまな機能はそれぞれ異なるエリアに配置されますが、機能エリア内のセンシティブなユニットには特別な注意を払わなければなりません。

一般的に、PCB レイアウトでは次の原則に従う必要があります。

a.高速回路では、部品のピン配置パラメータを考慮する必要があり、特に高速クロック信号に対しては、部品ピンの分布容量が非常に重要となる。同時に、信号の発振を引き起こし、回路機能の不具合の原因となり得るため、分布インダクタンスも考慮に入れなければならない。したがって、レイアウトの過程では、将来の配線とEMIの影響低減を考慮しつつ、リード長を短くして高密度に配置を行う必要がある。

b.アナログ部品と電子部品の両方が回路内に存在する場合、レイアウト工程においてそれぞれを独立して配置しなければなりません。デジタル部品の信号は、複数の高調波を含む複雑な成分を持つため、アナログ信号に大きな影響を与えます。そのため、それらは十分な注意を払って検討する必要があります。

c.クロックユニットは、高速回路において不可欠な存在です。クロックユニットの動作機構は、実際にはノイズ源と同等であり、つまり、特定の条件が満たされるとこのユニットは発振することを意味します。伝導性妨害および放射性妨害の重要な発生源として、クロックユニットをPCBの端部に配置してはなりません。そうしないと、EMIが非常に深刻になります。回路内のEMIを大幅に低減するためには、クロックユニットをPCBの中央に配置する必要があります。

・ルーティング

の過程でPCB配線低コストの状況下では、EMI の影響を低減するために、グラウンドプレーンは可能な限り拡大することができる。しかし、コストを厳密に管理しなければならない状況では、PCB の層数およびスタック構成を慎重に検討する必要がある。さらに、信号の種類を考慮し、高速信号と低速信号はそれぞれ独立して配線しなければならない。加えて、ノイズ源およびノイズ抑制の強化方法、インピーダンスマッチングの問題(適切なマッチングが行われていない高速信号は、必ず信号反射を引き起こし、回路の信頼性を低下させる)、およびネットリストなど、他の要素も考慮する必要がある。

a. ルーティングの基本原則

ルーティングで遵守される一般的な原則には、次のようなものがあります。

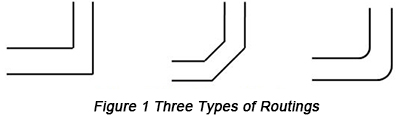

1).配線ではブレークポイントを避けるべきであり、つまり図1に示すように直角を避ける必要があります。

直角は反射を引き起こす可能性があるため、この現象を避けるために屈折点は滑らかに設計する必要があります。同時に、重要な信号は分割されたエリアを越えてはならず、さもないとEMIが即座に増大します。最も一般的な信号のバイパスは、異なる電源分割エリアを横切ることです。

2). レイアウトの過程では、アナログ部品とデジタル部品を互いに分離することが求められます。これは、それぞれの配線も分離すべきであることを意味します。同時に、グランド線および電源線の幅を広くする必要があり、一般的なルールとして、グランド線の幅は電源線より広く、電源線の幅は信号線より広くするべきです。さらに、信号線の配線においては 3W ルールを十分に考慮し、多層基板では内部層に対して 20H ルールを考慮する必要があります。以上の作業を完了することで、EMI の 70% を回避することが可能です。アナログの高感度配線に関しては、グランド処理などの対策を実施することができます。

3).USB2.0 やその他の高速差動ラインの配線においては、差動ペア配線を適用し、差動ペア間のリファレンス面の一貫性を確保する必要があります。差動ペアは一般的に高速信号であるため、PCB の端部には配線を配置しないでください。

b. ループ

PCB設計においてループを完全に避けることはできません。ループは、信号が出ていき戻ってくることで形成され、それぞれのループは機能上アンテナとしての役割を果たします。PCBにおけるEMIを低減するためには、ループの数とループのアンテナ能力の両方を減らす必要があります。これは、PCB設計において各信号の流れる方向を意識し、高速信号についてはループ面積を小さくしなければならないことを意味します。

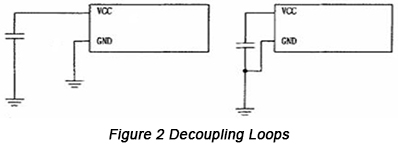

回路において、最も一般的に使用されるループは、図2に示すように、デカップリングコンデンサによって囲まれた電源ループ内に存在するループです。

図2の左側の図のようにデカップリングコンデンサを配置すると、比較的大きな電流ループが生成され、顕著なEMI現象が発生する。これに対して、図2の右側の図のようにデカップリングコンデンサをチップのすぐ近くに配置すると、非常に小さなデカップリングループが形成され、その主な機能はEMIを低減することである。ループを減らすために従うべき原則は次のとおりである。

1).各信号線上の任意の2点間には、1本の経路のみが保証されている。

2). 信号ループが妨げられないように確保したうえで、グラウンドプレーンを適用すること。

c. PCBのグランド線

1).PCBのグラウンディングシステムにおいては、デジタルグランド、アナロググランド、およびシステムシールドグランドの違いを明確にする必要があります。デジタルグランドとアナロググランドを分離するためにビーズコアとコンデンサを用い、デジタルグランドとフィールドグランドは直接接続する必要があります。

2).可能であれば、PCB上のグランド配線は幅を広くするべきです。

3). 閉回路を形成することによって接地線これにより、耐干渉能力が強化され、システム間の電位差が低減されます。

・フィルタ設計

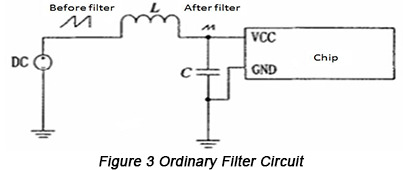

高速PCBでは、電源線および信号線にフィルタ処理を実装することができます。一般的な対策には、磁気フィルタ部品、EMIフィルタ、およびデカップリングコンデンサの追加が含まれます。

a. デカップリングコンデンサの選定

1).回路において、デカップリングコンデンサは電源を安定させ、耐ノイズ性能を強化するのに役立ちます。一般的に、デカップリングコンデンサには、高い安定性と高精度、小型であること、そして低ESR(等価直列抵抗)といった特性から、セラミックコンデンサが選ばれます。回路設計では、容量値は1μFから100μFの範囲で選定され、耐電圧性能については回路に応じて考慮する必要があります。

2).デカップリングコンデンサは、部品のすぐ近くに配置する必要があります。

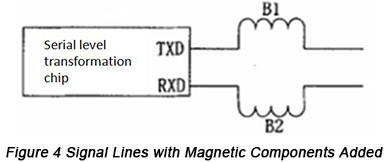

b. 磁気部品の選定

磁性部品はインダクタとフェライトビーズに分類できます。一般的に、インダクタは電源端子の末端に配置され、フェライトビーズは信号ラインの間に配置されます。処理の過程でコンポーネント選択飽和パラメータを考慮する必要があります。磁気部品が一度飽和に達すると、焼損してしまいます。さらに、磁気部品の品質とDCRパラメータの両方を考慮しなければなりません。

信号ライン間で一般的に用いられる対策として、EMI耐性を強化するためにシリアルラインへ磁気ビーズを適用する方法があります。

c. EMIフィルタの選定

深刻なコモンモード干渉が発生する領域は、電源が入力され信号線が出力される箇所に位置する。一般的なコモンモード干渉対策としては、コモンモードインダクタ、バリスタ、LC 回路、および専用の EMI フィルタの追加が挙げられる。高速回路においては、USB や HDMI などのデジタルインターフェース上での高速伝送に対して EMI 問題を考慮しなければならない。

・信号反射

信号伝送においては、送信端のエネルギーが常に負荷端へ伝送されることが期待されます。これは、ZL が ZO と等しくあるべきことを意味します。もし両者が等しくない場合、エネルギーの一部が反射されます。

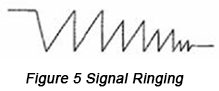

回線の伝送遅延が比較的長い場合、より強い信号が送信端に反射される。その結果、下の図5に示すように、リンギングが発生した際には補償のために比較的大きな量を変更する必要がある。

リンギングが信号に発生すると、EMI は最も深刻なレベルに達します。PCB 設計でこのような現象を回避するために、表1の原則に従ってください。

| 信号エッジ時間 (ns) | 信号線の長さ(インチ) |

| 5 | 8.6 |

| 4 | 6.9 |

| 3 | 5.1 |

| 2 | 3.4 |

| 1 | 1.7 |

製品設計の後、多くの対策を講じてEMIを回避しようとしても、問題は試験を実施するまで発見されないことがあります。その後、問題を解決するためにいくつかの修正を行うことができます。

EMIテストには、試験方法、装置および試験位置が含まれます。試験方法は、すべての項目を参照して実施する必要があります。装置が規格に達しない場合は、分光器を用いて定性的な試験を行うことができます。装置の具体的なEMI値が必要な場合は、専門の装置を使用しなければなりません。試験位置については、暗室で試験を行うのが最適です。

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

[email protected] [email protected]

[email protected] [email protected]

ご支援ありがとうございます!お寄せいただいたご意見は、サービス最適化のために詳細に検討させていただきます。お客様のご提案が最も価値のあるものとして採用された場合、100ドル分のクーポンを添えて、すぐにメールでご連絡いたします。