高速電子工学において、多層プリント基板複雑なアプリケーション向けに、より高い実装密度、優れた信号完全性、そしてより強力な性能を実現します。しかし、そのコンパクトな配線、密に積層されたレイヤー、および高周波信号また、深刻な電磁干渉(EMI)のリスクも引き起こします。制御されていないEMIは信号品質を劣化させ、クロストークを発生させ、システムの不安定性を誘発し、FCC、CE、CISPR などのEMC適合試験における不合格につながります。EMIの低減はオプションの付加要素ではなく、信頼性が高く、認証取得が可能で、市場投入可能な設計にとって中核となる要件です。

本記事では、多層PCBレイアウトにおけるEMIを最小化するための、実務で検証された実践的な手法を紹介します。レイヤースタック構成、グラウンディング、配線、フィルタリング、シールド、そして検証までを網羅します。これらのガイドラインに従うことで、放射を制御し、ノイズを抑え、実際の電磁環境下でも安定した性能を維持できるレイアウトを構築できます。

多層PCBにおけるEMIの基本を理解する

電磁干渉(EMI)とは、回路の動作を妨害する不要な電磁エネルギーを指します。電磁両立性(EMC)とは、機器がその環境内で正常に機能し、他の機器に許容できない干渉を生じさせないことを意味します。多層基板では、EMI はしばしば次のような要因から発生します。

高速エッジレートにより強い高周波高調波を生成する高速信号

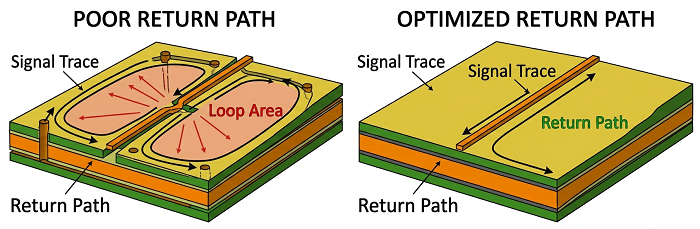

不適切な信号リターンパスによって形成される大きな電流ループ

近接して並行に配線されたトレース間のクロストーク

電源分配の不安定性および電源レール上のノイズ

放射ループを生じさせる不適切な接地

アンテナとして機能する浮遊導体、未使用ピン、または長いケーブル

EMIは主に2つの経路で伝搬します。放射(空中結合)と伝導(ワイヤやケーブルに沿った伝搬)です。効果的なEMI低減には、レイアウト段階でこれら両方の経路を対象とすることが重要です。

低EMIのためのレイヤースタックアップ最適化

レイヤースタックアップ多層PCBにおけるEMI制御の基盤となる。適切に設計されたスタックアップは、リターンパスを短縮し、電界と磁界を閉じ込め、層間のノイズ結合を低減する。

連続参照平面を使用する

すべての信号層には、低インダクタンスのリターンパスを提供するために、隣接するグラウンドまたは電源プレーンを設ける必要があります。この構造により電磁界が閉じ込められ、放射が大幅に低減されます。

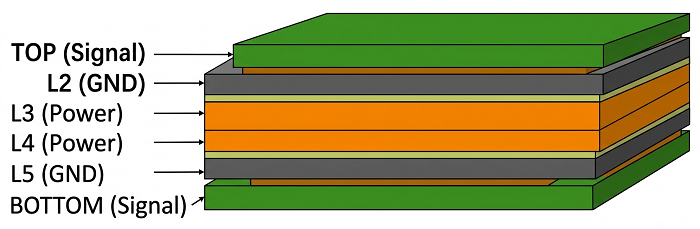

4層基板推奨スタックアップ:信号 → GND → 電源 → 信号

6層基板推奨スタックアップ:信号 → GND → 電源 → 電源 → GND → 信号

分割されたり断片化されたプレーンよりも、連続した一体のプレーンの方がはるかに優れています。グラウンド層や電源層には、ギャップ、スロット、過度な空隙を設けないようにしてください。これらはリターン電流に迂回を強制し、ループ面積を増大させてしまいます。

電源プレーンとグラウンドプレーンを密接に配置する

電源プレーンは、できるだけ薄い誘電体層(理想的には 0.254 mm(10 mil)未満)を介してグラウンドプレーンに直接隣接させて配置します。これにより、高周波で自然に動作するデカップリングコンデンサが形成され、電圧を安定させ、インピーダンスを低減し、広い周波数帯域にわたってノイズを抑制できます。

孤立したシグナル層を避ける

グラウンドプレーンを挟まずに、ある信号層を他の2つの信号層の間に配置してはならない。そのような「孤立した」信号層は深刻なクロストークと不十分な電界閉じ込めを引き起こし、EMI を大幅に増加させる。

グラウンディング戦略を極める

グラウンディングは、EMI を制御するうえで最も効果的な手段です。不適切なグラウンディングは、ループ、共通インピーダンスノイズ、および放射構造を生じさせます。

高周波にはマルチポイント接地を使用する

1 MHz を超える回路では、連続したグラウンドプレーンへの多点接地の方が優れています。これは高周波数でのインピーダンスを低減し、大きなグラウンドループを防ぎます。低周波回路では、循環電流を避けるために一点接地を用いる場合があります。

グラウンドスティッチングビアを追加

層を切り替える信号ビアの近くには、複数のグランドビアを配置してください。これらの「スティッチングビア」は、連続したリターンパスを維持し、層遷移時の電界漏れを防ぎ、インピーダンスを安定させます。高速設計では、グランドビアの間隔を12.7 mm(0.5インチ)未満に保ってください。

グラウンドループの除去

リターンパスは短く、直接的で、信号経路と重なるように設計してください。大きなグラウンドループは強く放射するループアンテナとして機能します。高速配線とそのリターンパスは、密接に結合された状態に保ってください。

クロストークと放射を最小限に抑えるための配線制御

トレース配線はEMIに直接影響します。慎重な配線により、結合が減少し、アンテナが短くなり、信号の完全性が維持されます。

3Wルールに従う

配線幅の少なくとも3倍以上の配線間隔を維持してください。これにより、隣接する配線間の容量性および誘導性のクロストークが低減されます。ノイズに敏感な信号や高速信号の場合は、より広い間隔を使用してください。

重要な信号は内層に配線する

クロック、高速データレーン、およびノイズの多い信号は、グラウンドプレーンに挟まれた内層に配線します。このストリップライン構造は優れたシールド効果を提供し、電磁界を閉じ込めます。

基板の端部付近での配線を避ける

基板の端に近い配線は、より強く放射し、外部からの干渉にも弱くなります。高速配線は、基板端から少なくとも誘電体厚さ1枚分以上離して配置してください。

差動ペアを使用する

重要な高速インターフェースでは、密接に結合され、長さが揃えられた差動ペアを使用してください。これにより、コモンモードノイズが打ち消され、放射が低減され、耐ノイズ性が向上します。

トレース長を短縮する

トレースを短くすると、アンテナ効果が小さくなり、放射も低減されます。クロックライン、オシレータ配線、および立ち上がりの速い信号の長さを最小限に抑えてください。

デカップリングとフィルタリングを効果的に活用する

デカップリングコンデンサとEMIフィルタは、ノイズが基板全体に広がったり外部へ放射されたりする前に、その発生源で抑制します。

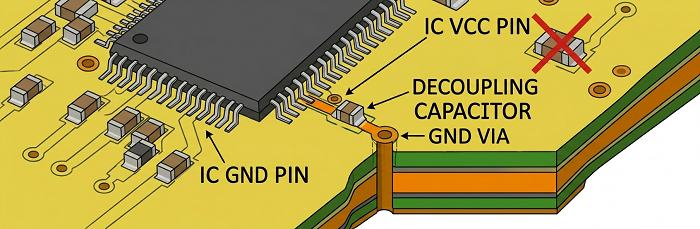

ICの近くにデカップリングコンデンサを配置する

高周波用コンデンサ(0.1 μF など)は、IC の電源ピンから 2.54 mm(100 mil)以内に実装してください。寄生インダクタンスを最小化するために、短く幅広い配線またはビアによる直接接続を使用します。高周波用の小容量コンデンサと、低周波安定化用の大容量バルクコンデンサを組み合わせて使用します。

フェライトビーズとフィルタを適用する

DC を通過させつつ高周波ノイズを減衰させるために、電源入力部にフェライトビーズを配置します。I/O ポートおよび電源ラインには、伝導性 EMI を遮断し、ケーブルが放射アンテナになるのを防ぐために、π フィルタまたは LC フィルタを追加します。

シールドおよび部品配置

戦略的なシールドと部品配置により、ノイズ源を感度の高い回路から分離します。

ノイズの多い回路と高感度回路を分離する

スイッチングレギュレータ、クロック、および RF 回路は、アナログ回路、センサー、低レベル受信回路から離して配置してください。アイソレーションバリアを形成するために、グラウンドプレーンまたはガードトレースを使用してください。

コンポーネントレベルのシールドを使用する

発振器、RFモジュール、およびスイッチング回路を金属シールド缶で覆います。シールドが複数のビアを介して確実にグラウンドプレーンに接続され、連続したファラデーケージを形成するようにしてください。

ガードリングとグランドフィル

高感度またはノイズの多い配線の周囲には、グラウンドのガードリングを配置してください。外層にはグラウンドの銅ポアを使用し、内部のグラウンドプレーンとビアで接続して閉じ込め効果を高めます。浮遊した銅ポアは避けてください。EMI を悪化させる可能性があります。

PCB材料の選定

材料特性は、高周波性能とEMIに影響を与えます。

インピーダンス制御を維持するために、誘電率(Dk)が安定したラミネートを選択してください。

電源層とグラウンド層の間により薄い誘電体を使用して、容量を増加させ、ノイズを低減します。

非常に高速な設計では、信号の減衰と放射を低減するために、低損失材料の採用を検討してください。

EMI性能の検証

最高のレイアウトであっても、検証が必要です。

試作段階でホットスポットを検出するために、近磁界プローブを用いてプレコンプライアンステストを実施します。

認定試験所において、放射エミッション、伝導エミッション、およびイミュニティに関する正式なEMC試験を実施する。

テスト結果に基づいてレイアウトを反復的に見直し、共振、放射、または結合の問題を修正する。

避けるべき一般的な間違い

信号のリターンパスを無視し、大きなループを許容すること

不要なグラウンドプレーンの分割

ICから離れすぎた位置にデカップリングコンデンサを配置すること

長距離にわたって高速信号を並行に配線する

未使用のピン、テストポイント、または配線をフローティングのままにする

最終設計段階までEMI試験を遅らせること

結論

多層PCBレイアウトにおけるEMI低減には、スタックアップ、グラウンディング、配線、フィルタリング、およびシールドにわたる体系的な計画が必要です。これらの手法を設計サイクルの初期段階で実装することで、EMCが大幅に向上し、手戻りが減少し、認証取得までの時間が短縮されます。

EMI 最適化設計および製造基準に基づいて構築された、プロフェッショナルで高信頼性の多層 PCB を求めるなら、電磁両立性と高性能製造に豊富な経験を持つパートナーを選択してください。

PCBCart高度な多層PCB製造を専門としており、低EMIレイアウト手法、高品質な材料、そして厳格なプロセス管理を全面的にサポートします。民生用電子機器、産業機器、あるいは高速デジタルシステムのいずれを開発している場合でも、PCBCartは性能、信頼性、そして各種規格への適合性を兼ね備えた基板を提供します。PCBCartを利用すれば、EMI最適化されたレイアウトを、実環境でも一貫した性能を発揮する量産対応のPCBへと具現化できます。

役立つリソース

・PCB EMC設計における初回成功の確保

・高速レイアウトのコツ

•PCB上の2本の並列マイクロストリップライン間のクロストーク設計戦略

・高速PCB設計における信号品質の課題とその解決策