Pada masa kini, perkembangan pesat teknologi Internet menyaksikan penggunaan meluas e-mel, pembayaran dalam talian dan komunikasi peribadi. Dalam latar belakang ini, keselamatan maklumat telah menjadi tema penyelidikan yang kritikal di seluruh dunia. Teknologi PKI (Public Key Infrastructure) menyediakan perkhidmatan keselamatan dengan menggunakan teori dan teknologi kunci awam. Teknologi PCIE (Peripheral Component Interface Express) telah menerima aplikasi yang meluas dalam peranti berkelajuan tinggi sebagai piawaian bas I/O generasi ketiga yang menggunakan penghantaran data bersiri dan teknologi saling sambung titik ke titik. Dalam bidang reka bentuk sistem digital, frekuensi jam yang agak tinggi membawa kepada beberapa masalah dari perspektif integriti isyarat, integriti kuasa dan gangguan silang, dan reka bentuk PCB tradisional gagal memenuhi keperluan kestabilan sistem.

Artikel ini menawarkan satu skim reka bentuk PCB bagi kad kata laluan berkelajuan tinggi berasaskan PCIE berdasarkan kelebihan penghantaran bersiri berkelajuan tinggi PCIE.

Skim Reka Bentuk Keseluruhan

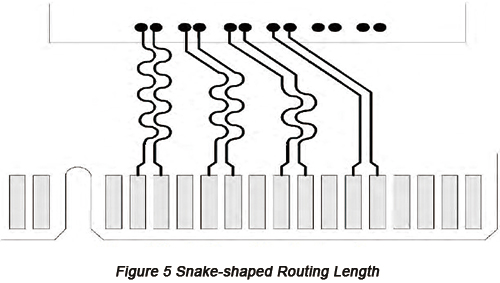

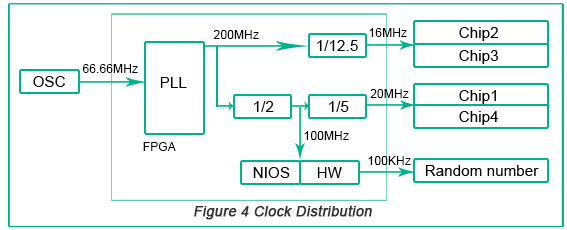

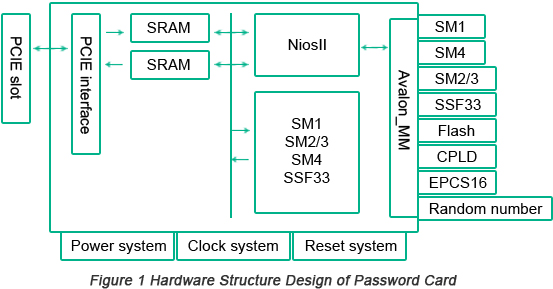

Cip FPGA EP4CGX50CF23C6N yang tergolong dalam Cyclone IV GX yang direka oleh Altera digunakan dalam reka bentuk ini, mengintegrasikan modul IP teras keras PCIE dan melaksanakan reka bentuk kad kata laluan penghantaran data berkelajuan tinggi 4 saluran. Empat jenis cip, cip 1, cip 2, cip 3 dan cip 4, masing-masing berupaya melaksanakan algoritma SM1, SM2/SM3, SM4 dan SSF33 serta melaksanakan fungsi inisialisasi kad kata laluan, pengurusan kunci rahsia, sandaran dan pemulihan serta pengurusan keizinan. Kad kata laluan digunakan dalam PC, disambungkan dengan papan induk dalam PC melalui slot PCIE dan dikawal oleh PC. Teras keras IP dalam FPGA digunakan untuk melaksanakan PCIE, yang membawa kepada komunikasi antara teras PCIE dan cache SRAM serta modul kawalan. Sebagai pusat kawalan, NiosII melaksanakan fungsi perisian kad kata laluan. Pada masa yang sama, cip kata laluan tambahan melaksanakan komunikasi antara setiap modul antara muka dan kad kata laluan. Reka bentuk struktur perkakasan kad kata laluan digambarkan dalam Rajah 1 di bawah.

Reka Bentuk PCB Berkelajuan Tinggi

• Susunan lapisan dan susun atur

Reka bentuk susunan lapisan ialah masalah paling penting yang perlu diambil kira dan reka bentuk susunan lapisan yang munasabah boleh menghalang radiasi EMI (Gangguan Elektromagnet), menjadikan voltan surges pada satah kuasa atau lapisan tanah serendah mungkin serta melindungi medan elektromagnet bagi isyarat dan kuasa. Secara amnya, papan berbilang lapisan dan berbilang bekalan kuasa digunakan dalam reka bentuk litar digital berkelajuan tinggi.Reka bentuk susunan PCBdilaksanakan berdasarkan unsur menyeluruh termasuk frekuensi jam litar,Kos pembuatan PCB, ketumpatan pin, tempoh pembuatan dan kebolehpercayaan. Selain itu, lapisan papan berbilang lapis hendaklah dikekalkan simetri dan bilangan lapisan hendaklah genap kerana reka bentuk susunan tidak simetri akan menyebabkan herotan papan. Kad kata laluan yang direka dalam artikel ini disambungkan dengan PC melalui slot PCIE dan saiz serta bentuk papan litar adalah tetap dengan ketinggian kira-kira 67mm dan panjang kira-kira 174mm, mengkonfigurasi pin antara muka PCIE X4 di bahagian bawah. Disebabkan ketumpatan komponen yang tinggi dan penghalaan yang tebal, bilangan lapisan PCB dipilih sebanyak 6 lapisan dengan pengagihan lapisan isyarat, lapisan kuasa, lapisan isyarat, lapisan kuasa, lapisan tanah, lapisan isyarat. Reka bentuk ini mengandungi 3 lapisan isyarat, 1 lapisan tanah dan 2 lapisan kuasa, menyediakan persekitaran yang diperlukan oleh integriti isyarat.

Selepas penentuan susunan lapisan PCB, pengelompokan komponen dan susun atur perlu dilaksanakan. Pertama, kedudukan komponen perlu diprogramkan mengikut dimensi dan corak PCB, dengan mengambil kira sambungan talian, pembahagian fungsi serta kekemasan dan keindahan antara komponen. Seterusnya, komponen perlu diagihkan secara munasabah mengikut gred voltan komponen yang berbeza untuk memendekkan wayar voltan sebanyak mungkin, yang dapat mengurangkan gangguan hingar kuasa dan meningkatkan kestabilan bekalan kuasa. Penempatan cip perlu memberi perhatian kepada hubungan antara litar bantu dan cipnya serta kepada penempatan pengayun kristal di belakang pin jam. Komponen berhingar tinggi perlu dielakkan daripada diletakkan di sekeliling pengayun kristal dan hendaklah diletakkan berhampiran komponen pemacunya. Selain itu, penempatan setiap pin kuasa dan isyarat cip perlu dipertimbangkan dengan kedudukan dan arahnya dilaraskan berdasarkan talian yang disambungkan.

Oleh sebab nisbah panjang dan lebar kad kata laluan melebihi 2:1 dengan kedudukan slot PCIE, lubang pemasangan dan LED penunjuk yang telah ditetapkan, susun atur komponen bagi komponen tetap perlu dipertimbangkan terlebih dahulu dalam susun atur komponen. Di samping itu, disebabkan oleh bilangan talian sambungan yang banyak antara komponen dan FPGA, susun atur komponen perlu dilaksanakan dengan FPGA sebagai pusat terlebih dahulu sebelum menentukan kedudukan komponen lain supaya ruang bahagian atas dan bawah PCB dapat digunakan dengan berkesan bagi meninggalkan ruang yang mencukupi antara komponen dengan komponen dan antara komponen dengan lubang penentududukan.

• Reka bentuk kuasa

Dalamreka bentuk papan litar berkelajuan tinggi, reka bentuk sistem kuasa berkait rapat secara langsung dengan kejayaan keseluruhan sistem. Bunyi yang dijana oleh kuasa dan tanah hendaklah dikurangkan ke tahap minimum bagi memastikan kebolehpercayaan produk. Penggunaan skim pengagihan kuasa dalam kaedah berlapis merujuk kepada hakikat bahawa kuasa diagihkan melalui logam pada keseluruhan lapisan, mengurangkan impedans kuasa dan bunyi serta meningkatkan kebolehpercayaan. Oleh sebab berbilang kuasa terlibat dalam PCB, reka bentuk lapisan berbilang kuasa hendaklah digunakan, yang mampu menghapuskan gangguan gandingan impedans awam sebagai satu gelung bunyi. Penggunaan kapasitan nyahganding mampu menyelesaikan masalah keutuhan kuasa kerana kapasitor hanya boleh diletakkan pada lapisan bawah atau lapisan atas PCB, berdasarkan mana wayar yang menyambungkan kapasitor nyahganding hendaklah pendek dan lebar. Menurut bahan cip, arus yang melalui talian kuasa boleh dikira dan lebar jejak boleh ditentukan. Semakin lebar jejak, semakin banyak arus yang boleh dibawanya. Formula eksperimen adalah seperti berikut:W(lebar garisan: mm) ≥L(mm/A) xSaya(semasa ini: A)

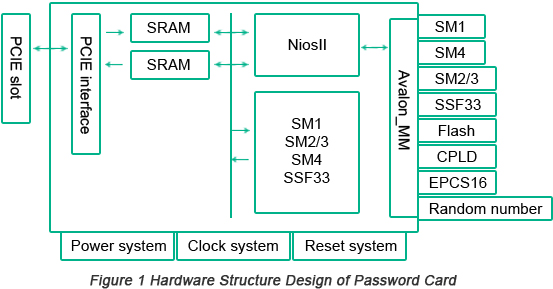

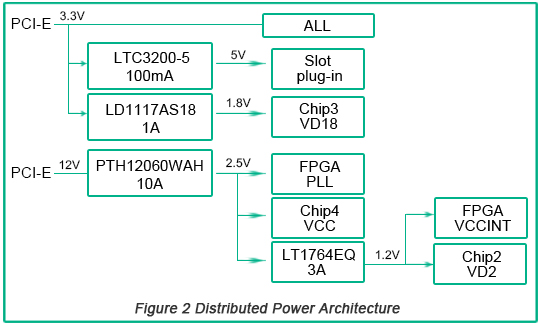

Beberapa bekalan kuasa pada PCB memperoleh satu atau dua jenis kuasa daripada papan kuasa melalui papan belakang dan kuasa tersebut kemudian ditukar kepada bekalan kuasa lain yang diperlukan oleh komponen. Penukaran kuasa dibahagikan kepada dua seni bina: seni bina kuasa berpusat dan seni bina kuasa teragih. Yang pertama merujuk kepada kuasa yang dibekalkan oleh satu bekalan kuasa bebas dan kemudian ditukar kepada semua jenis kuasa yang diperlukan manakala yang kedua merujuk kepada penukaran kuasa berbilang peringkat. Oleh kerana seni bina kuasa berpusat mempunyai kelemahan kos yang tinggi dan kawasan PCB yang besar, seni bina kuasa teragih digunakan dalam reka bentuk ini. Kad kriptografi melibatkan 6 jenis kuasa, termasuk 12V, 3.3V, 5V, 2.5V, 1.2V dan 1.8V. Reka bentuk ini bermula dengan penyertaan bekalan kuasa 3.3V dan 12V dalam slot PCIE dan kemudian bekalan kuasa 3.3V mampu menjana bekalan kuasa 5V dan 1.8V melalui cip penukaran voltan, membekalkan kuasa untuk plug-in dan cip 3. Seterusnya, bekalan kuasa 12V ditukar kepada bekalan kuasa 2.5V untuk membekalkan kuasa kepada FPGA dan cip 4. Akhir sekali, bekalan kuasa 2.5V ditukar kepada bekalan kuasa 1.2V untuk membekalkan kuasa kepada FPGA dan cip 2. Seni bina kuasa teragih bagi kad kriptografi ditunjukkan dalam Rajah 2 di bawah.

• Reka bentuk lubang tembus

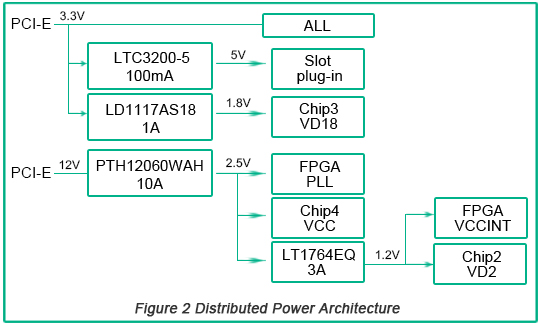

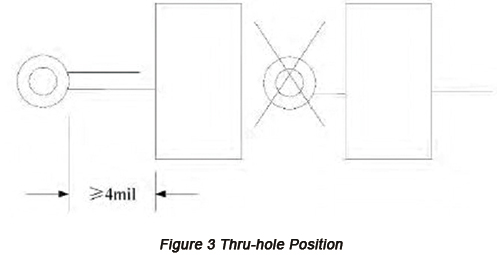

Dalam proses susun atur reka bentuk untukPCB berbilang lapisandengan ketumpatan yang tinggi, lubang tembus hendaklah digunakan, memindahkan isyarat dari satu lapisan ke lapisan yang lain untuk menyediakan komunikasi elektrik antara lapisan. Reka bentuk kedudukan lubang tembus perlu dilaksanakan dengan sangat berhati-hati. Lubang tembus tidak boleh diletakkan pada pad dan satu garisan tercetak boleh digunakan untuk sambungan, jika tidak akan menyebabkan masalah seperti kesan batu nisan dan pateri tidak mencukupi. Topeng pateri hendaklah disalut pada pad lubang tembus dengan jarak ditetapkan kepada 4 mil dan lubang tembus tidak boleh diletakkan di tengah pad bagi komponen cip pada bahagian pematerian. Kedudukan lubang tembus digambarkan dalam Rajah 3 di bawah.

Selain itu, kedudukan lubang tembus tidak boleh terlalu dekat dengan goldfinger yang bahagian palamnya perlu mempunyai serong. Untuk membolehkan papan litar dipalam ke dalam slot PCIE, serong (1~1.5)x45° boleh direka pada kedua-dua tepi sisi papan palam.

• Penghalaan isyarat berkelajuan tinggi

Dalam proses penghalaan, pengagihan perlu dilaraskan secara munasabah untuk meminimumkan talian sambungan supaya gangguan silang dapat dikurangkan. Dalam proses penghalaan isyarat digital berkelajuan tinggi, lapisan isyarat berhampiran lapisan berbilang kuasa hendaklah dijauhkan daripada permukaan rujukan kuasa bagi mengelakkan penjanaan laluan balik oleh arus isyarat.

Oleh kerana frekuensi isyarat jam litar berkelajuan tinggi adalah agak tinggi, jidar, hanyutan dan herotan sangat mempengaruhi sistem sehingga reka bentuk PCB berkelajuan tinggi memerlukan gangguan gelombang isyarat yang kecil. Oleh itu, masalah pengagihan dan peroutingan jam perlu dipertimbangkan terlebih dahulu. Peroutingan mesti dilaksanakan pada isyarat jam berkelajuan tinggi dan peroutingan talian isyarat jam utama mestilah sependek mungkin, lurus serta bebas daripada lubang tembus dan bahagian kuasa bagi mengelakkan gangguan silang antara jam dan kuasa. Apabila berbilang jam dengan frekuensi berbeza digunakan pada PCB yang sama, dua talian jam dengan frekuensi berbeza tidak boleh dikekalkan selari. Walau bagaimanapun, bagi berbilang komponen yang menggunakan isyarat jam dengan frekuensi yang sama, rangkaian boleh diagihkan mengikut jenis labah-labah, jenis pokok dan jenis cabang.

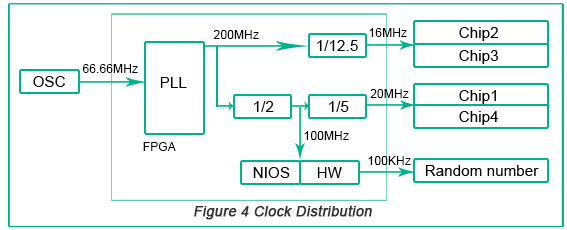

Dalam kad kriptografi berkelajuan tinggi, FPGA memperoleh jam 66.66MHz melalui pengayun kristal pada PCB. Selepas gelung dengan kunci intrinsik di dalam FPGA, jam asas 200MHz dijana sebagai antara muka untuk cip 2 dan cip 3 mengendalikan jam. Kemudian jam 100MHz disediakan selepas litar pembahagi frekuensi intrinsik sebagai teras lembut NiosII dan jam kerja litar perkakasan di dalam FPGA. Frekuensi terbahagi 16MHz ialah jam kerja untuk cip 2 dan cip 3 manakala frekuensi terbahagi 20MHz ialah jam kerja untuk cip 1 dan cip 4. Pengagihan jam dipaparkan dalam Rajah 4 di bawah.

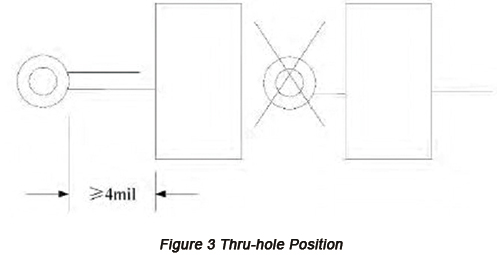

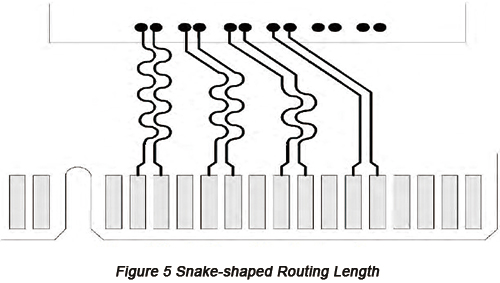

Penghantaran isyarat berkelajuan tinggi antara slot PCIE dan PC dilaksanakan oleh kad kriptografi berkelajuan tinggi melalui penghalaan pasangan pembezaan untuk mengelakkan masalah berkaitan keutuhan isyarat. Secara umumnya, wayar pembumian tidak diletakkan di antara isyarat pasangan pembezaan, jika tidak kesan gandingan antara isyarat pasangan pembezaan akan rosak. Selepas penghalaan isyarat pasangan pembezaan, tembaga diletakkan di sekeliling isyarat berkelajuan tinggi PCB dengan ruang lebihan dipenuhi sepenuhnya dengan wayar pembumian untuk meningkatkan keupayaan EMI litar. Kunci bagiPendawaian PCBadalah untuk mengekalkan kesimetrian pasangan pembezaan. Jika panjang pasangan pembezaan tidak sepadan, ketepatan pembacaan dan penulisan data akan terjejas dengan kadar penghantaran data menurun. Untuk memastikan kesahihan sistem dalam pembacaan data dalam tempoh yang sama, perbezaan lengah antara isyarat pembezaan mesti dikekalkan dalam julat yang dibenarkan dan panjang perutean mestilah benar-benar sama. Oleh itu, perutean berbentuk ular boleh digunakan untuk menyelesaikan masalah ini dengan melaraskan lengah masa. Dalam reka bentuk ini, komunikasi dilaksanakan oleh PC melalui PCIE dan kad kriptografi dan penghantaran serta penerimaan isyarat berkelajuan tinggi dilaksanakan oleh isyarat pasangan pembezaan dengan panjang perutean PCB dikawal dalam 25 mil. Rajah padanan panjang perutean berbentuk ular ditunjukkan dalam Rajah 5.