ปัจจุบัน การพัฒนาอย่างรวดเร็วของเทคโนโลยีอินเทอร์เน็ตทำให้มีการใช้งานอีเมล การชำระเงินออนไลน์ และการสื่อสารส่วนบุคคลอย่างแพร่หลาย ภายใต้บริบทนี้ ความปลอดภัยของข้อมูลจึงกลายเป็นประเด็นวิจัยที่สำคัญทั่วโลก เทคโนโลยี PKI (Public Key Infrastructure) ให้บริการด้านความปลอดภัยโดยใช้ทฤษฎีและเทคโนโลยีกุญแจสาธารณะ เทคโนโลยี PCIE (Peripheral Component Interface Express) ได้รับการประยุกต์ใช้อย่างกว้างขวางในอุปกรณ์ความเร็วสูง ในฐานะมาตรฐานบัส I/O รุ่นที่สามที่ใช้การส่งข้อมูลแบบอนุกรมและเทคโนโลยีการเชื่อมต่อแบบจุดต่อจุด ในด้านการออกแบบระบบดิจิทัล ความถี่สัญญาณนาฬิกาที่ค่อนข้างสูงก่อให้เกิดปัญหาในมุมมองของความสมบูรณ์ของสัญญาณ ความสมบูรณ์ของพลังงาน และการรบกวนข้ามสัญญาณ และการออกแบบ PCB แบบดั้งเดิมไม่สามารถตอบสนองความต้องการด้านเสถียรภาพของระบบได้

บทความนี้นำเสนอแผนผังการออกแบบ PCB สำหรับบัตรรหัสผ่านความเร็วสูงที่ใช้ PCIE โดยอ้างอิงจากข้อดีของการส่งสัญญาณอนุกรมความเร็วสูงของ PCIE

แผนผังการออกแบบโดยรวม

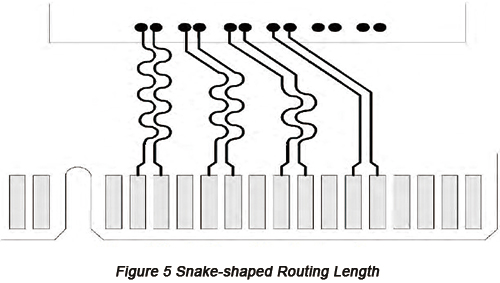

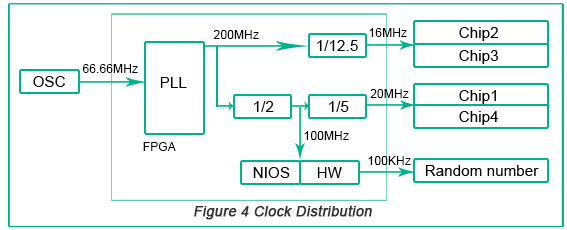

ชิป FPGA รุ่น EP4CGX50CF23C6N ในตระกูล Cyclone IV GX ที่ออกแบบโดย Altera ถูกนำมาใช้ในงานออกแบบนี้ โดยบูรณาการโมดูล IP ฮาร์ดคอร์ PCIE และทำให้สามารถออกแบบการ์ดรหัสผ่านสำหรับการส่งข้อมูลความเร็วสูง 4 ช่องได้ ชิปทั้งสี่ชนิด ได้แก่ ชิป 1 ชิป 2 ชิป 3 และชิป 4 สามารถใช้งานอัลกอริทึม SM1, SM2/SM3, SM4 และ SSF33 ตามลำดับ และสามารถใช้งานฟังก์ชันการเริ่มต้นการ์ดรหัสผ่าน การจัดการกุญแจลับ การสำรองและกู้คืน รวมถึงการจัดการสิทธิ์ การ์ดรหัสผ่านถูกใช้งานในเครื่องพีซี เชื่อมต่อกับเมนบอร์ดของพีซีผ่านช่องเสียบ PCIE และถูกควบคุมโดยพีซี IP ฮาร์ดคอร์ใน FPGA ถูกใช้เพื่อทำให้ PCIE ทำงาน ส่งผลให้เกิดการสื่อสารระหว่างแกน PCIE กับแคช SRAM และโมดูลควบคุม NiosII ทำหน้าที่เป็นศูนย์ควบคุม โดยทำหน้าที่เป็นซอฟต์แวร์ของการ์ดรหัสผ่าน ในขณะเดียวกัน ชิปรหัสผ่านเพิ่มเติมจะทำหน้าที่สื่อสารระหว่างแต่ละโมดูลอินเทอร์เฟซกับการ์ดรหัสผ่าน โครงสร้างฮาร์ดแวร์ของการ์ดรหัสผ่านแสดงไว้ในรูปที่ 1 ด้านล่าง

การออกแบบแผงวงจรพิมพ์ความเร็วสูง

• การซ้อนชั้นและเลย์เอาต์

การออกแบบสแต็กอัปเป็นปัญหาที่สำคัญที่สุดซึ่งควรนำมาพิจารณา และการออกแบบสแต็กอัปที่เหมาะสมสามารถยับยั้งการแผ่รังสี EMI (Electromagnetic Interference) ทำให้แรงดันไฟฟ้าชั่วขณะบนเพลนจ่ายไฟหรือชั้นกราวด์มีค่าต่ำที่สุดเท่าที่จะเป็นไปได้ และช่วยป้องกันสนามแม่เหล็กไฟฟ้าของสัญญาณและกำลังไฟฟ้า โดยทั่วไปแล้ว แผงวงจรหลายชั้นและแหล่งจ่ายไฟหลายชุดจะถูกนำมาใช้ในการออกแบบวงจรดิจิทัลความเร็วสูงการออกแบบการซ้อนชั้น PCBถูกนำไปใช้โดยอิงตามองค์ประกอบที่ครอบคลุมต่าง ๆ รวมถึงความถี่สัญญาณนาฬิกาของวงจรต้นทุนการผลิตแผงวงจรพิมพ์ความหนาแน่นของขา ระยะเวลาการผลิต และความเชื่อถือได้ นอกจากนี้ ชั้นของบอร์ดหลายชั้นควรคงความสมมาตรและจำนวนชั้นควรเป็นจำนวนคู่ เนื่องจากการออกแบบการซ้อนชั้นที่ไม่สมมาตรจะทำให้บอร์ดโก่งงอได้ การ์ดรหัสผ่านที่ออกแบบในบทความนี้เชื่อมต่อกับพีซีผ่านช่องเสียบ PCIE และขนาดรวมถึงรูปทรงของแผงวงจรได้รับการกำหนดตายตัว โดยมีความสูงประมาณ 67 มม. และความยาวประมาณ 174 มม. พร้อมกำหนดขาอินเทอร์เฟซ PCIE X4 ไว้ที่ด้านล่าง เนื่องจากมีความหนาแน่นของชิ้นส่วนสูงและลายวงจรหนา จำนวนชั้นของ PCB จึงถูกเลือกเป็น 6 ชั้น โดยมีการจัดเรียงเป็น ชั้นสัญญาณ ชั้นจ่ายไฟ ชั้นสัญญาณ ชั้นจ่ายไฟ ชั้นกราวด์ ชั้นสัญญาณ การออกแบบนี้ประกอบด้วยชั้นสัญญาณ 3 ชั้น ชั้นกราวด์ 1 ชั้น และชั้นจ่ายไฟ 2 ชั้น ซึ่งให้สภาพแวดล้อมที่จำเป็นต่อความสมบูรณ์ของสัญญาณ

หลังจากกำหนดโครงสร้างการซ้อนชั้นของแผ่น PCB แล้ว จึงค่อยดำเนินการจัดกลุ่มและวางตำแหน่งอุปกรณ์ ขั้นแรกต้องกำหนดตำแหน่งของอุปกรณ์ให้สอดคล้องกับขนาดและลวดลายของ PCB โดยคำนึงถึงการเดินสาย การแบ่งส่วนการทำงาน และความเป็นระเบียบสวยงามระหว่างอุปกรณ์ จากนั้นต้องจัดวางอุปกรณ์ให้เหมาะสมตามระดับแรงดันของอุปกรณ์แต่ละชนิด เพื่อลดความยาวของสายไฟแรงดันให้สั้นที่สุด ซึ่งช่วยลดสัญญาณรบกวนจากแหล่งจ่ายไฟและเพิ่มเสถียรภาพของระบบจ่ายไฟ

การวางชิปต้องให้ความสำคัญกับความสัมพันธ์ระหว่างวงจรเสริมกับตัวชิปเอง และการวางตำแหน่งคริสตัลออสซิลเลเตอร์ให้อยู่ด้านหลังขาของสัญญาณนาฬิกา ควรหลีกเลี่ยงการวางอุปกรณ์ที่มีสัญญาณรบกวนสูงไว้รอบคริสตัลออสซิลเลเตอร์ และควรวางให้อยู่ใกล้กับอุปกรณ์ขับของมัน นอกจากนี้ การวางตำแหน่งขาไฟเลี้ยงและขาสัญญาณของชิปแต่ละตัวต้องพิจารณาร่วมกับตำแหน่งและทิศทางของมัน โดยปรับให้เหมาะสมตามเส้นสัญญาณที่เชื่อมต่อ

เนื่องจากอัตราส่วนความยาวต่อความกว้างของการ์ดรหัสผ่านมีค่ามากกว่า 2:1 และตำแหน่งของช่องเสียบ PCIE รูยึด และไฟ LED แสดงสถานะถูกกำหนดตายตัวแล้ว การจัดวางอุปกรณ์จึงต้องพิจารณาอุปกรณ์ที่มีตำแหน่งตายตัวเหล่านี้ก่อน นอกจากนี้ เนื่องจากมีจำนวนเส้นเชื่อมต่อระหว่างอุปกรณ์กับ FPGA เป็นจำนวนมาก การจัดวางอุปกรณ์จึงควรยึด FPGA เป็นศูนย์กลางก่อนการกำหนดตำแหน่งของอุปกรณ์อื่น ๆ เพื่อให้สามารถใช้พื้นที่ด้านบนและด้านล่างของ PCB ได้อย่างมีประสิทธิภาพ และเว้นระยะห่างที่เพียงพอระหว่างอุปกรณ์แต่ละตัว รวมถึงระหว่างอุปกรณ์กับรูยึดตำแหน่งด้วย

• การออกแบบพลังงาน

ในการออกแบบแผงวงจรความเร็วสูงการออกแบบระบบจ่ายไฟมีความเกี่ยวข้องโดยตรงกับความสำเร็จของระบบทั้งหมด ต้องลดสัญญาณรบกวนที่เกิดจากไฟและกราวด์ให้น้อยที่สุดเพื่อให้มั่นใจในความเชื่อถือได้ของผลิตภัณฑ์ การประยุกต์ใช้โครงร่างการกระจายไฟในวิธีการแบ่งชั้นหมายถึงการที่ไฟถูกกระจายผ่านโลหะบนทั้งชั้น ซึ่งช่วยลดอิมพีแดนซ์ของไฟและสัญญาณรบกวน และเพิ่มความเชื่อถือได้ เนื่องจาก PCB เกี่ยวข้องกับแหล่งจ่ายไฟหลายชุด จึงควรใช้การออกแบบชั้นไฟหลายชั้น ซึ่งสามารถขจัดการรบกวนจากการคัปปลิงอิมพีแดนซ์ร่วมที่เป็นวงจรสัญญาณรบกวนได้ การใช้ตัวเก็บประจุแบบดีคัปปลิงสามารถแก้ปัญหาความสมบูรณ์ของแหล่งจ่ายไฟได้ เนื่องจากตัวเก็บประจุสามารถวางได้เฉพาะบนชั้นล่างหรือชั้นบนของ PCB โดยที่สายที่เชื่อมต่อตัวเก็บประจุแบบดีคัปปลิงควรมีความสั้นและกว้าง จากวัสดุของชิปสามารถคำนวณกระแสที่ไหลผ่านสายไฟได้และสามารถกำหนดความกว้างของลายวงจรได้ ยิ่งลายวงจรกว้างเท่าใด ก็ยิ่งสามารถรับกระแสได้มากขึ้นเท่านั้น สูตรเชิงทดลองแสดงดังนี้:ดับเบิลยู(ความกว้างของเส้น: มม.) ≥แ(mm/A) xฉัน(ปัจจุบัน: A)

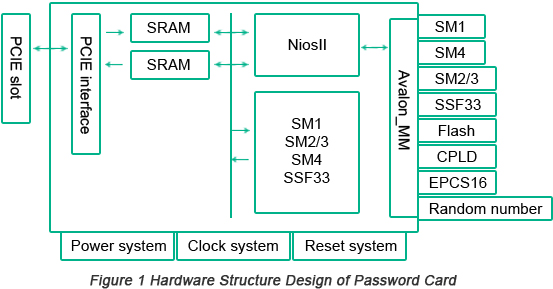

แหล่งจ่ายไฟหลายชุดบนแผงวงจรพิมพ์ (PCB) จะรับพลังงานหนึ่งหรือสองชนิดจากบอร์ดจ่ายไฟผ่านแบ็กเพลน จากนั้นจึงแปลงเป็นแหล่งจ่ายไฟชนิดอื่นที่ชิ้นส่วนต้องการ การแปลงพลังงานแบ่งออกเป็นสองสถาปัตยกรรม ได้แก่ สถาปัตยกรรมจ่ายไฟแบบรวมศูนย์ และสถาปัตยกรรมจ่ายไฟแบบกระจาย สถาปัตยกรรมแบบแรกหมายถึงการที่พลังงานถูกจ่ายโดยแหล่งจ่ายไฟอิสระหนึ่งชุดแล้วจึงแปลงเป็นแหล่งจ่ายไฟทุกชนิดที่ต้องการ ส่วนสถาปัตยกรรมแบบหลังหมายถึงการแปลงพลังงานแบบหลายระดับ เนื่องจากสถาปัตยกรรมจ่ายไฟแบบรวมศูนย์มีข้อเสียคือมีต้นทุนสูงและใช้พื้นที่บน PCB มาก จึงใช้สถาปัตยกรรมจ่ายไฟแบบกระจายในงานออกแบบนี้

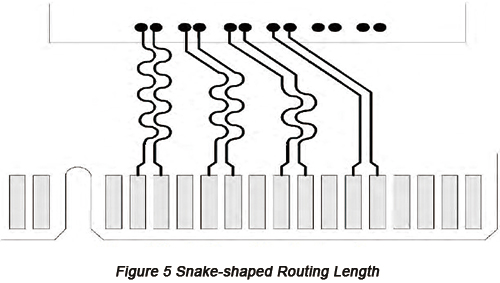

การ์ดเข้ารหัสเกี่ยวข้องกับแหล่งจ่ายไฟ 6 ชนิด ได้แก่ 12V, 3.3V, 5V, 2.5V, 1.2V และ 1.8V การออกแบบนี้เริ่มจากการใช้แหล่งจ่ายไฟ 3.3V และ 12V จากช่องเสียบ PCIE จากนั้นแหล่งจ่ายไฟ 3.3V จะสามารถสร้างแหล่งจ่ายไฟ 5V และ 1.8V ผ่านชิปแปลงแรงดันไฟ เพื่อจ่ายไฟให้กับโมดูลเสียบต่อและชิป 3 ต่อมา แหล่งจ่ายไฟ 12V จะถูกแปลงเป็น 2.5V เพื่อจ่ายไฟให้กับ FPGA และชิป 4 สุดท้าย แหล่งจ่ายไฟ 2.5V จะถูกแปลงเป็น 1.2V เพื่อจ่ายไฟให้กับ FPGA และชิป 2 สถาปัตยกรรมจ่ายไฟแบบกระจายของการ์ดเข้ารหัสแสดงไว้ในรูปที่ 2 ด้านล่าง

• การออกแบบแบบรูทะลุ

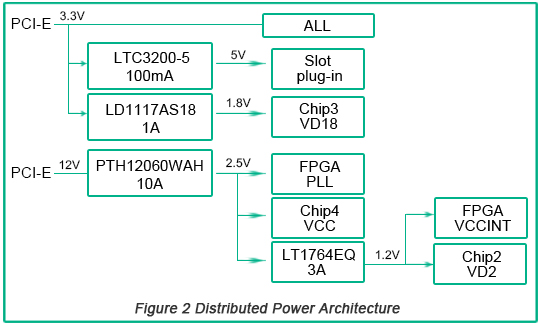

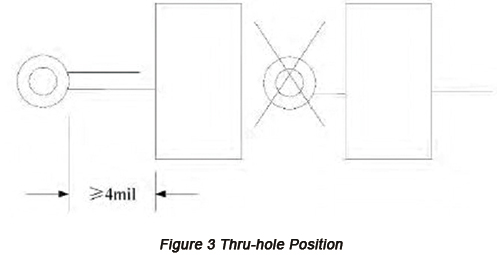

ระหว่างกระบวนการออกแบบเลย์เอาต์สำหรับแผงวงจรพิมพ์หลายชั้นเมื่อมีความหนาแน่นสูง ควรใช้รูทะลุเพื่อส่งสัญญาณจากชั้นหนึ่งไปยังอีกชั้นหนึ่ง เพื่อให้เกิดการเชื่อมต่อทางไฟฟ้าระหว่างชั้น การออกแบบตำแหน่งของรูทะลุต้องทำอย่างระมัดระวัง ห้ามวางรูทะลุบนแผ่นแพด และควรใช้เส้นลายวงจรเพียงเส้นเดียวสำหรับการเชื่อมต่อ มิฉะนั้นจะทำให้เกิดปัญหาเช่น การลอยตัวของชิ้นส่วน (tombstone) และปริมาณประสานไม่เพียงพอ ต้องเคลือบโซลเดอร์มาสก์บนแพดของรูทะลุ โดยกำหนดระยะห่างเป็น 4 mil และห้ามวางรูทะลุไว้ที่กึ่งกลางของแพดสำหรับชิ้นส่วนแบบชิปด้านบัดกรี ตำแหน่งของรูทะลุแสดงไว้ในรูปที่ 3 ด้านล่าง

นอกจากนี้ ตำแหน่งของรูทะลุจะต้องไม่อยู่ใกล้กับขอบทอง (goldfinger) มากเกินไป โดยด้านเสียบปลั๊กของขอบทองควรมีมุมลบคม (chamfer) เพื่อให้แผงวงจรสามารถเสียบเข้าช่อง PCIE ได้ สามารถออกแบบมุมลบคมขนาด (1~1.5)x45° บนขอบด้านข้างทั้งสองด้านของแผงวงจรที่ใช้เสียบปลั๊ก

• การกำหนดเส้นทางสัญญาณความเร็วสูง

ในกระบวนการเดินสาย ต้องปรับการกระจายให้เหมาะสมเพื่อลดจำนวนสายเชื่อมต่อให้เหลือน้อยที่สุดเพื่อที่จะลดการเกิดครอสทอล์ก ในกระบวนการเดินสายสัญญาณดิจิทัลความเร็วสูง การเดินสายบนเลเยอร์สัญญาณที่อยู่ใกล้กับเลเยอร์จ่ายไฟหลายชุดควรอยู่ห่างจากพื้นผิวอ้างอิงของเพาเวอร์ เพื่อหลีกเลี่ยงการเกิดเส้นทางย้อนกลับของกระแสสัญญาณ

เนื่องจากความถี่สัญญาณนาฬิกาในวงจรความเร็วสูงมีค่าสูงมาก การสั่น (jitter) การลอย (drifting) และการบิดเบือนของสัญญาณจึงส่งผลกระทบต่อระบบอย่างมาก ทำให้การออกแบบ PCB ความเร็วสูงต้องการการรบกวนของสัญญาณคลื่นให้มีค่าน้อยที่สุด ดังนั้นจึงควรพิจารณาปัญหาการกระจายสัญญาณนาฬิกาและการวางลายวงจรก่อนเป็นอันดับแรก

การวางลายวงจรจำเป็นต้องดำเนินการกับสัญญาณนาฬิกาความเร็วสูง และการวางลายของเส้นสัญญาณนาฬิกาหลักควรให้สั้นที่สุด เป็นเส้นตรง และหลีกเลี่ยงการใช้รูทะลุ (via) และส่วนของวงจรจ่ายไฟ เพื่อป้องกันการเกิดครอสทอล์กระหว่างสัญญาณนาฬิกากับไฟเลี้ยง

เมื่อมีการใช้สัญญาณนาฬิกาหลายชุดที่มีความถี่ต่างกันบน PCB แผ่นเดียวกัน ห้ามวางเส้นสัญญาณนาฬิกาสองเส้นที่มีความถี่ต่างกันให้ขนานกัน อย่างไรก็ตาม สำหรับอุปกรณ์หลายตัวที่ใช้สัญญาณนาฬิกาที่มีความถี่เท่ากัน สามารถกระจายเครือข่ายสัญญาณได้ในรูปแบบใยแมงมุม แบบต้นไม้ หรือแบบกิ่งก้านได้

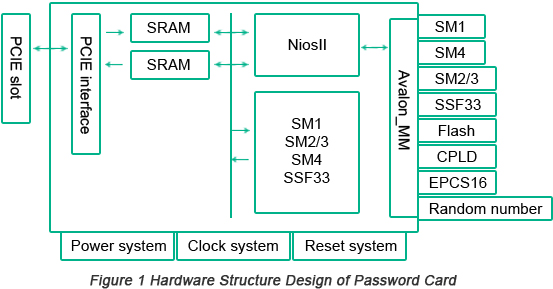

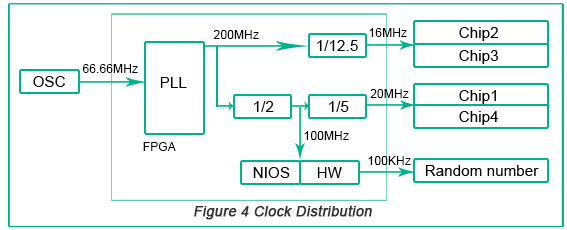

ในการ์ดการเข้ารหัสความเร็วสูง FPGA จะได้รับสัญญาณนาฬิกา 66.66MHz ผ่านคริสตัลออสซิลเลเตอร์บน PCB หลังจากวนลูปด้วยวงจรล็อกภายในตัว FPGA แล้ว จะสร้างสัญญาณนาฬิกาพื้นฐาน 200MHz ขึ้นมาเป็นอินเทอร์เฟซสำหรับชิป 2 และชิป 3 เพื่อใช้งานสัญญาณนาฬิกา จากนั้นจะมีการสร้างสัญญาณนาฬิกา 100MHz ผ่านวงจรแบ่งความถี่ภายใน เพื่อใช้เป็นคอร์แบบซอฟต์ NiosII และเป็นสัญญาณนาฬิกาการทำงานของวงจรฮาร์ดแวร์ภายใน FPGA ความถี่ที่ถูกแบ่งลงมาเป็น 16MHz จะใช้เป็นสัญญาณนาฬิกาการทำงานสำหรับชิป 2 และชิป 3 ในขณะที่ความถี่ที่ถูกแบ่งลงมาเป็น 20MHz จะใช้เป็นสัญญาณนาฬิกาการทำงานสำหรับชิป 1 และชิป 4 การกระจายสัญญาณนาฬิกาจะแสดงดังภาพที่ 4 ด้านล่าง

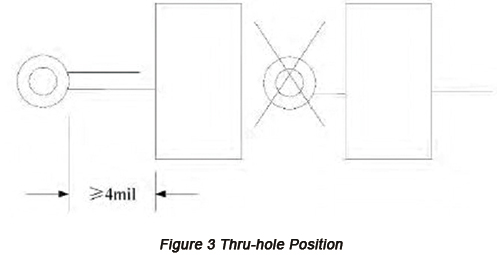

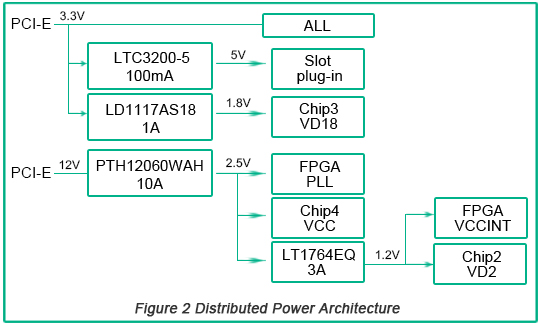

การส่งสัญญาณความเร็วสูงระหว่างสล็อต PCIE และพีซีถูกทำให้เป็นจริงโดยใช้การ์ดเข้ารหัสความเร็วสูงผ่านการเดินลายสัญญาณแบบคู่ดิฟเฟอเรนเชียลเพื่อหลีกเลี่ยงปัญหาที่เกี่ยวข้องกับความสมบูรณ์ของสัญญาณ โดยทั่วไปแล้วจะไม่วางสายกราวด์คั่นระหว่างสัญญาณคู่ดิฟเฟอเรนเชียล มิฉะนั้นจะทำให้เอฟเฟกต์การคัปปลิงระหว่างสัญญาณคู่ดิฟเฟอเรนเชียลเสียไป หลังจากการเดินลายสัญญาณคู่ดิฟเฟอเรนเชียลแล้ว จะมีการวางทองแดงล้อมรอบสัญญาณความเร็วสูงบนแผ่น PCB โดยเติมพื้นที่ว่างให้เต็มด้วยสายกราวด์เพื่อเพิ่มความสามารถ EMI ของวงจร กุญแจของการเดินลายวงจร PCBคือการรักษาความสมมาตรของคู่สายดิฟเฟอเรนเชียล หากความยาวของคู่สายดิฟเฟอเรนเชียลไม่สอดคล้องกัน ความแม่นยำของการอ่านและเขียนข้อมูลจะได้รับผลกระทบพร้อมกับอัตราการส่งผ่านข้อมูลที่ลดลง เพื่อให้มั่นใจถึงความถูกต้องของการอ่านข้อมูลของระบบภายในช่วงเวลาเดียวกัน ความแตกต่างของความหน่วงระหว่างสัญญาณดิฟเฟอเรนเชียลต้องถูกควบคุมให้อยู่ภายในช่วงที่อนุญาต และความยาวของลายวงจรต้องเท่ากันอย่างเคร่งครัด ดังนั้นจึงสามารถใช้การเดินลายแบบงูเพื่อตอบโจทย์ปัญหานี้ด้วยการปรับเวลาแฝง ในการออกแบบนี้ การสื่อสารถูกดำเนินการโดยพีซีผ่าน PCIE และการส่งและรับสัญญาณความเร็วสูงถูกดำเนินการด้วยสัญญาณคู่สายดิฟเฟอเรนเชียล โดยควบคุมความยาวของลายวงจรบน PCB ให้อยู่ภายใน 25 mil แผนภาพการจับคู่ความยาวของลายวงจรแบบงูแสดงไว้ในรูปที่ 5