ในสถานการณ์ที่รวดเร็วและเปลี่ยนแปลงตลอดเวลาในโลกอิเล็กทรอนิกส์ในปัจจุบัน ทำให้มีความจำเป็นมากกว่าที่เคยว่าPCA/PCBAและการออกแบบ IC มีความน่าเชื่อถือและสามารถทำงานได้อย่างมีประสิทธิภาพ เมื่อเทคโนโลยีและอุปกรณ์ต่าง ๆ พัฒนาอย่างรวดเร็วโดยมุ่งเน้นการตอบสนองความต้องการที่ซับซ้อนอย่างมีประสิทธิภาพซึ่งเกิดขึ้นพร้อมกับ IoT, AI และ 5G แนวปฏิบัติที่มุ่งเน้นผลลัพธ์อย่างการออกแบบเพื่อความสามารถในการทดสอบหรือ DFT จึงมีบทบาทสำคัญ บทความนี้จะกล่าวถึงวิธีการทำ DFT ด้วยเครื่องมือและเทคนิคขั้นสูง

ความเกี่ยวข้องที่เพิ่มขึ้นของ DFT

การออกแบบเพื่อความสามารถในการทดสอบ (Design for Testability หรือ DFT) เป็นสาขาที่มุ่งเน้นการผนวกรวมฟังก์ชันการทดสอบเข้าไปในงานออกแบบแผงวงจรประกอบ (PCBA) และงานออกแบบวงจรรวม (IC) การทดสอบด้วย DFT ช่วยให้ระยะเวลาการทดสอบสั้นลงอย่างมากและมีความครอบคลุมของการตรวจหาความผิดพลาดที่ดียิ่งขึ้นในต้นทุนที่ลดลง เมื่อการออกแบบ IC มีความซับซ้อนมากขึ้นจากความก้าวหน้าของเทคโนโลยีกระบวนการระดับ 3 นาโนเมตรและการออกแบบที่มีทรานซิสเตอร์นับพันล้านตัว DFT จึงกลายเป็นสาขาที่มีความจำเป็นอย่างยิ่ง

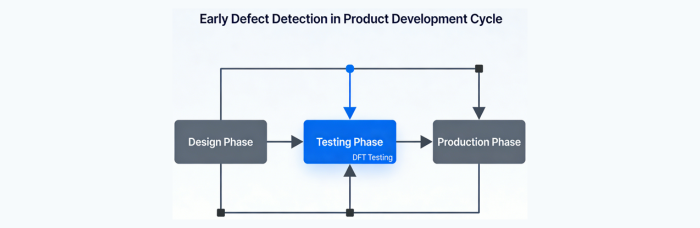

การตรวจจับความผิดปกติได้อย่างรวดเร็วและมีประสิทธิภาพ

เมื่อเทียบกับความสามารถในการระบุข้อบกพร่องในการผลิตแล้ว คงเป็นเรื่องยากที่จะระบุประโยชน์ที่สำคัญยิ่งกว่าที่เกี่ยวข้องกับ DFTระยะเริ่มต้นของการพัฒนาผลิตภัณฑ์โดยการตรวจพบข้อบกพร่องเหล่านี้ตั้งแต่ระยะเริ่มต้น ผู้ผลิตจะสามารถแก้ไขปัญหาเหล่านี้ได้อย่างง่ายดายโดยไม่ต้องทำการออกแบบใหม่ และส่งผลให้ลูกค้ามีความพึงพอใจในระดับสูง

การทดสอบอย่างมีประสิทธิภาพสำหรับการออกแบบที่ซับซ้อนและมีความหนาแน่นสูง

ผลิตภัณฑ์อิเล็กทรอนิกส์สมัยใหม่มักประกอบด้วยชิ้นส่วนที่จัดวางอย่างหนาแน่นและทำงานด้วยความเร็วสูง สิ่งเหล่านี้ก่อให้เกิดความท้าทายเพิ่มเติมต่อกระบวนการทดสอบแบบดั้งเดิม เทคนิค DFT ช่วยให้เข้าถึงจุดทดสอบที่สำคัญได้ง่ายขึ้นและช่วยปรับปรุงฟังก์ชันการวินิจฉัย ทำให้สามารถดำเนินการทดสอบกับการออกแบบที่ซับซ้อนได้

ลดการหลุดรอดของข้อบกพร่องจากการทดสอบ

แม้ว่าวิธีการทดสอบใด ๆ จะไม่สามารถรับประกันการครอบคลุมข้อบกพร่องได้ 100% แต่ DFT ช่วยลดความเป็นไปได้ของการหลุดรอดจากการทดสอบได้อย่างมาก การหลุดรอดจากการทดสอบเกิดขึ้นเมื่อผลิตภัณฑ์ที่มีข้อบกพร่องไม่ถูกตรวจพบในขั้นตอนการทดสอบ การลดเหตุการณ์เหล่านี้ช่วยป้องกันค่าใช้จ่ายในการซ่อมแซมที่สูงและรับรองความเชื่อถือได้ของผลิตภัณฑ์ในระดับที่เหนือกว่า

วิธีการ DFT ขั้นเชี่ยวชาญสำหรับปี 2025 และมองไปข้างหน้า

DFT แบบลำดับชั้น

DFT แบบลำดับชั้นช่วยจัดการกับการออกแบบ IC ขนาดใหญ่มากได้ DFT แบบลำดับชั้นจะแยกการออกแบบ IC ขนาดใหญ่ออกเป็นส่วนย่อยที่จัดการได้ง่ายขึ้น ช่วยให้สามารถทดสอบแต่ละส่วนได้แบบขนาน จึงช่วยลดปริมาณข้อมูลที่ต้องใช้และเวลาทดสอบลงได้อย่างมาก วิธีนี้มีประโยชน์อย่างยิ่งสำหรับการทดสอบ IC ขนาดใหญ่ที่มีทรานซิสเตอร์นับพันล้านตัว

DFT ที่ตระหนักถึงการใช้พลังงาน

วิธีการที่คำนึงถึงพลังงานมีบทบาทสำคัญในการทดสอบ เนื่องจากช่วยหลีกเลี่ยงการละเมิดข้อจำกัดด้านพลังงานที่เหมาะสมที่สุด นอกจากนี้ ยังมีความสำคัญเป็นพิเศษต่อการออกแบบที่ใช้พลังงานจากแบตเตอรี่ รวมถึงอุปกรณ์ IoT และโปรเซสเซอร์บนอุปกรณ์พกพา

การทดสอบที่ความเร็วจริง

การทดสอบที่ความเร็วจริง ซึ่งพบได้บ่อยในเทคโนโลยีความเร็วสูงอย่างเช่น 5G หมายถึงส่วนของการทดสอบด้วยตนเองแบบฝังในตัว (Built-In Self-Test: BIST) ที่ทำงานด้วยความเร็วการทำงานเต็มรูปแบบ การทดสอบที่ความเร็วจริงช่วยตรวจจับข้อบกพร่องที่เกี่ยวข้องกับเวลา ซึ่งอาจถูกมองข้ามไปเมื่อทดสอบที่ความเร็วต่ำกว่า ดังนั้นจึงช่วยให้มั่นใจได้ว่าองค์ประกอบจะทำงานได้อย่างถูกต้องในสภาพแวดล้อมการใช้งานที่เหมาะสมที่สุดของมัน

การประยุกต์ใช้เทคโนโลยี DFT ร่วมสมัย

ภายในปี 2025 บทบาทของโซลูชัน DFT สมัยใหม่จะกลายเป็นสิ่งจำเป็น โดยผสานการทำงานอัตโนมัติ ปัญญาประดิษฐ์ และฟังก์ชันการทำงานบนคลาวด์เข้ากับการทดสอบ

การแทรก DFT อัตโนมัติงานเชื่อมต่อระหว่างสแกนเชนและจุดทดสอบถูกทำให้เป็นแบบอัตโนมัติ จึงขจัดความเป็นไปได้ของความผิดพลาดทั้งหมด ช่วยลดระยะเวลาของโครงการ

การวิเคราะห์ความผิดปกติด้วยระบบปัญญาประดิษฐ์เครื่องมือ AI ใช้ประโยชน์จากดีไซน์เพื่อทำนายบริเวณที่อาจมีความบกพร่องได้ และด้วยเหตุนี้จึงช่วยเพิ่มความครอบคลุมของการตรวจหาความบกพร่องได้อย่างมาก

การจำลองการทดสอบระบบคลาวด์ระบบคลาวด์ช่วยให้สามารถจำลองการทดสอบจำนวนมากได้โดยไม่ต้องใช้อุปกรณ์ราคาแพง เนื่องจากสามารถดำเนินการหลายอย่างพร้อมกันได้ จึงช่วยย่นระยะเวลาในการจำลอง

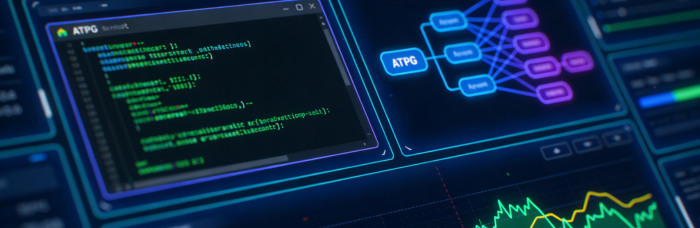

การทำให้การสร้างรูปแบบการทดสอบเป็นแบบอัตโนมัติ

เครื่องมือ ATPG มีความจำเป็นอย่างยิ่งต่อการบรรลุข้อกำหนดด้านความครอบคลุมของความบกพร่องในระดับสูง ซึ่งพบได้บ่อยในดีไซน์ที่มีความหนาแน่นสูง เครื่องมือเหล่านี้จะสร้างเวกเตอร์สำหรับทดสอบความบกพร่องประเภทต่าง ๆ โดยอัตโนมัติ ส่งผลให้เครื่องมือเหล่านี้สามารถรองรับการทดสอบได้อย่างครอบคลุม แม้สำหรับดีไซน์ที่ซับซ้อนมาก

การผสานรวมการเขียนสคริปต์โฟลว์ทดสอบ

สคริปต์สำหรับทำให้กระบวนการที่เกี่ยวข้องกับ DFT เป็นอัตโนมัติ ซึ่งถูกรวมอยู่ภายในโฟลว์การออกแบบโดยรวม ตั้งแต่การสังเคราะห์ไปจนถึงการจัดวางและเดินสาย ช่วยลดการออกแบบแบบวนซ้ำและช่วยให้ผลิตภัณฑ์ออกสู่ตลาดได้เร็วขึ้น

การติดตามการทดสอบแบบเรียลไทม์

ระบบตรวจสอบอัตโนมัติช่วยให้สมาชิกในสถานที่ได้รับข้อมูลป้อนกลับแบบเรียลไทม์ระหว่างการทดสอบ เพื่อให้สามารถปรับตัวและทำการเปลี่ยนแปลงได้ทันที ซึ่งจะช่วยขจัดการเสียเวลาไปกับการดีบักและการวิเคราะห์ความล้มเหลวในระดับขนาดใหญ่

แนวทางปฏิบัติที่ดีที่สุดสำหรับการใช้งาน DFT

การนำ DFT ไปใช้ให้มีประสิทธิภาพจำเป็นต้องอาศัยชุดแนวทางปฏิบัติที่ดีที่สุด ซึ่งสามารถกำหนดขึ้นมาเพื่อรับมือกับความท้าทายที่เกิดจากการออกแบบอิเล็กทรอนิกส์ขั้นสูงในปัจจุบัน

ผสานรวมให้เร็วที่สุดการผสานการวางแผน DFT เข้ากับกระบวนการออกแบบเริ่มต้นช่วยลดต้นทุนที่เกี่ยวข้องกับการออกแบบใหม่และทำให้มั่นใจว่าการวางแผน DFT เป็นไปตามเกณฑ์การออกแบบ

เพิ่มประสิทธิภาพเวลาและต้นทุนการทดสอบมีการใช้วิธีการบีบอัดข้อมูลทดสอบและการทดสอบแบบขนานเพื่อเพิ่มประสิทธิภาพด้านต้นทุนและเวลาในการทดสอบ

ใช้มาตรฐานอุตสาหกรรม:ใช้มาตรฐานอย่าง IEEE 1149.1 (JTAG) สำหรับการทดสอบบาวดารีสแกน มาตรฐานอุตสาหกรรมช่วยให้การทดสอบและการดีบักทำได้ง่ายขึ้น

อำนวยความสะดวกในการทำงานเป็นทีมมันช่วยสร้างแรงบันดาลใจให้เกิดความร่วมมือระหว่างทีมออกแบบและทีมทดสอบ เพื่อให้การปรับแต่ง DFT ทำได้ง่ายขึ้น โดยมองปัญหาในมุมมองภาพรวม และช่วยย่นระยะเวลาในการแก้ไขปัญหาได้มากถึง 30%

การเอาชนะความท้าทายของ DFT

แม้ว่า DFT จะมีประโยชน์ แต่ก็ยังมีความท้าทายที่เกี่ยวข้องกับการนำไปใช้ในงานออกแบบสมัยใหม่ดังที่สรุปไว้ด้านล่างนี้:

การจัดการปริมาณข้อมูลทดสอบ:เมื่อการออกแบบเพิ่มมากขึ้น ขนาดของข้อมูลทดสอบก็เพิ่มขึ้นตามไปด้วย ใช้อัลกอริทึมการบีบอัดข้อมูลและบริการคลาวด์เพื่อจัดการกับปริมาณข้อมูลขนาดใหญ่ได้อย่างมีประสิทธิภาพ

การสร้างสมดุลระหว่างความครอบคลุมของการทดสอบและการใช้พลังงานการมีการครอบคลุมการทดสอบในระดับสูงทำให้เกิดการใช้พลังงานสูง ใช้วิธีการทดสอบที่คำนึงถึงการใช้พลังงานซึ่งช่วยให้คุณสามารถรักษาความปลอดภัยไว้ได้ภายในระดับการใช้พลังงานที่ยอมรับได้

การตรวจสอบการออกแบบที่ไม่เป็นเนื้อเดียวกันชิปเซมิคอนดักเตอร์สมัยใหม่มีแนวโน้มที่จะรวมองค์ประกอบดิจิทัล อนาล็อก และ RF ไว้ภายในชิปเดียว มากกว่าการออกแบบรุ่นเก่า เพื่อให้สามารถตรวจสอบการออกแบบเหล่านี้ได้อย่างมีประสิทธิภาพ ผู้เชี่ยวชาญในอุตสาหกรรมจึงพึ่งพาเครื่องมือและวิธีการโซลูชัน DFT แบบสัญญาณผสม

เมื่อเราก้าวเข้าสู่ยุคที่ความก้าวหน้าทางเทคโนโลยีเกิดขึ้นอย่างรวดเร็วและชัดเจนยิ่งขึ้น การเรียนรู้วิธีประยุกต์ใช้วิธีการขั้นสูงของ DFT อย่างมีประสิทธิภาพจึงกลายเป็นสิ่งจำเป็นสำหรับธุรกิจที่ต้องการอยู่ในแนวหน้าของโลกอิเล็กทรอนิกส์ซึ่งมีการแข่งขันสูง ด้วยการใช้ประโยชน์จากวิธีการวางแผนล่วงหน้าและการใช้เทคโนโลยีและเครื่องมือที่มีความร่วมมือและมีความก้าวหน้าสูง ผู้เชี่ยวชาญจึงสามารถได้รับประโยชน์สูงสุด พร้อมทั้งบรรลุระยะเวลาในการเปลี่ยนผ่านที่มีประสิทธิภาพมากขึ้นและความคุ้มค่าด้านต้นทุนที่สูงกว่าเดิม

ที่ PCBCart เรามุ่งมั่นในการมอบบริการการผลิตและการประกอบระดับเวิลด์คลาสให้กับคุณ และยึดมั่นในมาตรฐานด้านคุณภาพที่เข้มงวดที่สุด เรามีความรู้และความเชี่ยวชาญอย่างกว้างขวางที่จะทำให้มั่นใจได้ว่าแผงวงจรประกอบ (PCBA) และการออกแบบ IC ของคุณไม่เพียงแค่เป็นไปตามมาตรฐานตลาดเท่านั้น แต่ยังเหนือกว่ามาตรฐานเหล่านั้นอีกด้วย ส่งผลให้คุณได้สร้างสรรค์ผลงานที่โดดเด่นและประสบความสำเร็จอย่างแท้จริง ตั้งแต่เทคโนโลยี IoT, AI ไปจนถึง 5G ไม่มีความท้าทายใดที่ใหญ่เกินไป เมื่อคุณนำการออกแบบยุคถัดไปของคุณมาสู่ความเป็นจริงด้วยความแม่นยำและคุณภาพอันไร้เทียมทานของเรา ให้เราช่วยคุณตั้งแต่วันนี้ด้วยการให้คำปรึกษาและข้อเสนอราคาที่แข่งขันได้สำหรับโซลูชันอิเล็กทรอนิกส์เชิงปฏิวัติของคุณ

ขอใบเสนอราคาทันทีสำหรับการประกอบแผงวงจรพิมพ์ (PCB) คุณภาพสูง

แหล่งข้อมูลที่เป็นประโยชน์

•การตรวจสอบด้วยแสงอัตโนมัติ

•การตรวจสอบเอ็กซเรย์อัตโนมัติ

•วิธีการตรวจสอบการประกอบแผงวงจรพิมพ์ (PCB)

•การทดสอบทางไฟฟ้า

•บทความแรก

•ตรวจสอบ DFM ฟรี