ในอุปกรณ์อิเล็กทรอนิกส์ความเร็วสูงแผงวงจรพิมพ์หลายชั้นมอบความหนาแน่นที่สูงขึ้น ความสมบูรณ์ของสัญญาณที่ดียิ่งขึ้น และประสิทธิภาพที่แข็งแกร่งยิ่งขึ้นสำหรับแอปพลิเคชันที่ซับซ้อน อย่างไรก็ตาม การเดินสายที่กะทัดรัด เลเยอร์ที่ซ้อนกันอย่างแน่นหนา และสัญญาณความถี่สูงยังทำให้เกิดความเสี่ยงด้านการรบกวนทางแม่เหล็กไฟฟ้า (EMI) อย่างรุนแรงอีกด้วย การรบกวน EMI ที่ไม่ได้รับการควบคุมจะทำให้คุณภาพสัญญาณลดลง ก่อให้เกิดการรบกวนข้ามช่องสัญญาณ (crosstalk) กระตุ้นให้ระบบไม่เสถียร และนำไปสู่ความล้มเหลวในการทดสอบการปฏิบัติตามมาตรฐาน EMC เช่น FCC, CE หรือ CISPR การลด EMI ไม่ใช่ตัวเลือกเสริม แต่เป็นข้อกำหนดหลักสำหรับการออกแบบที่เชื่อถือได้ รับรองได้ และพร้อมออกสู่ตลาด

บทความนี้นำเสนอวิธีการเชิงปฏิบัติที่ได้รับการพิสูจน์แล้วในทางวิศวกรรมเพื่อช่วยลด EMI ในการออกแบบเลย์เอาต์ PCB แบบหลายชั้น ครอบคลุมการจัดเรียงลำดับชั้นของเลเยอร์ การกราวด์ การเดินลาย การกรอง การป้องกันสัญญาณรบกวน และการตรวจสอบความถูกต้อง โดยการปฏิบัติตามแนวทางเหล่านี้ คุณสามารถออกแบบเลย์เอาต์ที่ควบคุมการแผ่รังสี จำกัดสัญญาณรบกวน และรักษาประสิทธิภาพการทำงานให้คงที่ในสภาพแวดล้อมแม่เหล็กไฟฟ้าจริงได้

ทำความเข้าใจพื้นฐาน EMI ในแผงวงจรพิมพ์หลายชั้น

การรบกวนทางแม่เหล็กไฟฟ้า (EMI) หมายถึงพลังงานแม่เหล็กไฟฟ้าที่ไม่พึงประสงค์ซึ่งรบกวนการทำงานของวงจร ความเข้ากันได้ทางแม่เหล็กไฟฟ้า (EMC) หมายถึงอุปกรณ์สามารถทำงานได้อย่างถูกต้องในสภาพแวดล้อมของตนโดยไม่ก่อให้เกิดการรบกวนที่ไม่อาจยอมรับได้ต่ออุปกรณ์อื่น ในบอร์ดหลายชั้น EMI มักเกิดจาก:

สัญญาณความเร็วสูงที่มีอัตราการเปลี่ยนแปลงขอบสัญญาณรวดเร็วซึ่งก่อให้เกิดฮาร์มอนิกความถี่สูงที่รุนแรง

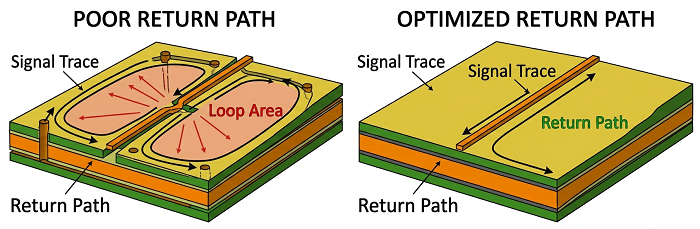

ลูปกระแสไฟฟ้าขนาดใหญ่ที่เกิดจากเส้นทางการคืนสัญญาณที่ไม่ดี

การรบกวนข้ามระหว่างลายวงจรขนานที่วางใกล้กันมาก

การกระจายพลังงานที่ไม่เสถียรและสัญญาณรบกวนบนรางจ่ายไฟ

การต่อลงดินที่ไม่ถูกต้องซึ่งก่อให้เกิดลูปการแผ่รังสี

ตัวนำลอย ขาใช้งานที่ไม่ได้ใช้ หรือสายเคเบิลยาวที่ทำหน้าที่เสมือนเสาอากาศ

EMI แพร่กระจายได้สองวิธีหลัก: ผ่านการแผ่รังสี (การคัปปลิงทางอากาศ) และการนำ (ตามสายไฟหรือสายเคเบิล) การลด EMI อย่างมีประสิทธิภาพจะต้องจัดการทั้งสองเส้นทางตั้งแต่ขั้นตอนการออกแบบเลย์เอาต์

ปรับแต่งการจัดเรียงเลเยอร์ให้เหมาะสมเพื่อให้ EMI ต่ำ

โครงสร้างซ้อนชั้นของเลเยอร์เป็นพื้นฐานของการควบคุม EMI ในแผงวงจรพิมพ์หลายชั้น (multi-layer PCB) การออกแบบโครงสร้างซ้อนชั้นที่ดีจะช่วยย่นระยะเส้นทางกระแสย้อนกลับ กักเก็บสนามไฟฟ้าและสนามแม่เหล็ก และลดการคัปปลิงสัญญาณรบกวนระหว่างชั้นต่าง ๆ

ใช้ระนาบอ้างอิงแบบต่อเนื่อง

ทุกชั้นสัญญาณควรมีระนาบกราวด์หรือระนาบจ่ายไฟที่อยู่ติดกันเพื่อให้เส้นทางกลับที่มีความเหนี่ยวนำต่ำ โครงสร้างนี้จะจำกัดสนามแม่เหล็กไฟฟ้าและลดการแผ่รังสีลงอย่างมาก

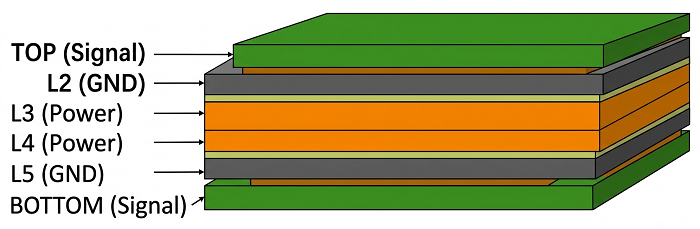

สำหรับบอร์ด 4 ชั้นสแต็กอัปที่แนะนำ: สัญญาณ → กราวด์ → เพาเวอร์ → สัญญาณ

สำหรับบอร์ด 6 ชั้นสแต็กอัปที่แนะนำ: สัญญาณ → กราวด์ → เพาเวอร์ → เพาเวอร์ → กราวด์ → สัญญาณ

ระนาบที่เป็นแผ่นทึบต่อเนื่องโดยไม่มีการแบ่งแยกจะดีกว่าระนาบที่ถูกแยกหรือแตกเป็นส่วน ๆ มาก ควรหลีกเลี่ยงช่องว่าง ร่อง หรือช่องว่างขนาดใหญ่เกินไปในชั้นกราวด์และชั้นจ่ายไฟ เนื่องจากสิ่งเหล่านี้บังคับให้กระแสไหลกลับต้องอ้อมและเพิ่มพื้นที่ของลูป

จับคู่ระนาบไฟเลี้ยงและระนาบกราวด์ให้ใกล้กัน

วางระนาบไฟเลี้ยงให้อยู่ติดกับระนาบกราวด์โดยมีชั้นไดอิเล็กทริกที่บางเป็นตัวคั่น — โดยอุดมคติควรน้อยกว่า 0.254 มม. (10 mil) การจัดวางเช่นนี้จะสร้างตัวเก็บประจุสำหรับการดีคัปปลิงความถี่สูงตามธรรมชาติ ซึ่งช่วยทำให้แรงดันคงที่ ลดอิมพีแดนซ์ และกดทับสัญญาณรบกวนในย่านความถี่กว้าง

หลีกเลี่ยงชั้นสัญญาณที่แยกเดี่ยว

อย่าวางเลเยอร์สัญญาณไว้ระหว่างเลเยอร์สัญญาณอื่นสองเลเยอร์โดยไม่มีเพลนกราวด์คั่นกลาง เลเยอร์สัญญาณที่ “แยกเดี่ยว” เช่นนี้จะมีปัญหาการครอสทอล์กอย่างรุนแรงและการกักเก็บสนามไฟฟ้าที่ไม่ดี ทำให้ EMI เพิ่มสูงขึ้นอย่างมาก

กลยุทธ์การยึดโยงขั้นสูง

การต่อลงกราวด์เป็นวิธีที่มีประสิทธิภาพสูงสุดเพียงวิธีเดียวในการควบคุม EMI การต่อลงกราวด์ที่ไม่ดีจะก่อให้เกิดลูป สัญญาณรบกวนจากอิมพีแดนซ์ร่วม และโครงสร้างที่แผ่รังสี

ใช้การต่อลงกราวด์แบบหลายจุดสำหรับความถี่สูง

สำหรับวงจรที่มีความถี่สูงกว่า 1 MHz การต่อลงกราวด์แบบหลายจุดเข้ากับระนาบกราวด์ต่อเนื่องจะให้ประสิทธิภาพที่ดีกว่า เพราะช่วยลดอิมพีแดนซ์ที่ความถี่สูงและป้องกันการเกิดกราวด์ลูปขนาดใหญ่ ส่วนวงจรความถี่ต่ำอาจใช้การต่อลงกราวด์แบบจุดเดียวเพื่อหลีกเลี่ยงกระแสไหลวน

เพิ่มรูเชื่อมกราวด์ (Ground Stitching Vias)

ใช้วิอากราวด์หลายจุดใกล้วิอาสัญญาณที่มีการสลับเลเยอร์ “วิอาเย็บต่อ” เหล่านี้ช่วยคงเส้นทางกระแสย้อนกลับให้ต่อเนื่อง ป้องกันการรั่วไหลของสนามไฟฟ้าที่จุดเปลี่ยนเลเยอร์ และทำให้อิมพีแดนซ์มีความเสถียร สำหรับการออกแบบความเร็วสูง ควรรักษาระยะห่างระหว่างวิอากราวด์ให้ต่ำกว่า 12.7 มม. (0.5 นิ้ว)

กำจัดกราวด์ลูป

ออกแบบเส้นทางกระแสย้อนกลับให้สั้น ตรง และซ้อนทับกับเส้นทางสัญญาณ วงลูปกราวด์ขนาดใหญ่จะทำหน้าที่เป็นเสาอากาศแบบลูปที่แผ่รังสีได้แรง รักษาระยะการวางลายวงจรความเร็วสูงและเส้นทางกระแสย้อนกลับให้แนบชิดกัน

ควบคุมการจัดเส้นทางเพื่อลดการรบกวนระหว่างสัญญาณและการแผ่รังสี

การวางลายวงจรมีผลโดยตรงต่อ EMI การวางลายวงจรอย่างรอบคอบช่วยลดการคัปปลิง ทำให้เสาอากาศสั้นลง และคงไว้ซึ่งความสมบูรณ์ของสัญญาณ

ปฏิบัติตามกฎ 3W

เว้นระยะห่างระหว่างลายทองแดงอย่างน้อยสามเท่าของความกว้างลายทองแดง วิธีนี้ช่วยลดการรบกวนแบบครอสทอล์กเชิงความจุและเชิงเหนี่ยวนำระหว่างลายทองแดงที่อยู่ติดกัน สำหรับสัญญาณที่ไวต่อสัญญาณรบกวนหรือสัญญาณความเร็วสูง ให้ใช้ระยะห่างที่กว้างขึ้น

กำหนดเส้นทางสัญญาณสำคัญบนชั้นใน

กำหนดเส้นทางสัญญาณนาฬิกา เลนข้อมูลความเร็วสูง และสัญญาณที่มีสัญญาณรบกวนบนเลเยอร์ด้านในที่ถูกประกบอยู่ระหว่างระนาบกราวด์ โครงสร้างสไตรป์ไลน์นี้ให้การป้องกันสัญญาณที่ยอดเยี่ยมและช่วยกักเก็บสนามแม่เหล็กไฟฟ้าไว้ภายใน

หลีกเลี่ยงการวางเส้นทางใกล้ขอบบอร์ด

รอยทางใกล้ขอบบอร์ดจะแผ่รังสีได้แรงกว่าและมีความอ่อนไหวต่อสัญญาณรบกวนภายนอกมากกว่า ควรรักษารอยทางความเร็วสูงให้อยู่ห่างจากขอบอย่างน้อยหนึ่งความหนาของไดอิเล็กทริก

ใช้คู่ดิฟเฟอเรนเชียล

สำหรับอินเทอร์เฟซความเร็วสูงที่มีความสำคัญ ให้ใช้คู่สายดิฟเฟอเรนเชียลที่วางชิดกันและมีความยาวเท่ากัน ซึ่งจะช่วยยกเลิกสัญญาณรบกวนแบบโหมดร่วม ลดการแผ่รังสี และเพิ่มความทนทานต่อสัญญาณรบกวน

ลดความยาวของลายวงจร

รอยต่อที่สั้นลงหมายถึงเสาอากาศที่มีขนาดเล็กลงและการแผ่รังสีน้อยลง ลดความยาวของสายสัญญาณนาฬิกา รอยต่อออสซิลเลเตอร์ และสัญญาณที่มีขอบขาขึ้น‑ลงเร็วให้สั้นที่สุด

ใช้การแยกส่วนและการกรองอย่างมีประสิทธิภาพ

ตัวเก็บประจุแบบแยกและตัวกรอง EMI จะกดทับสัญญาณรบกวนที่แหล่งกำเนิดก่อนที่มันจะแพร่กระจายไปทั่วบอร์ดหรือแผ่รังสีออกไป

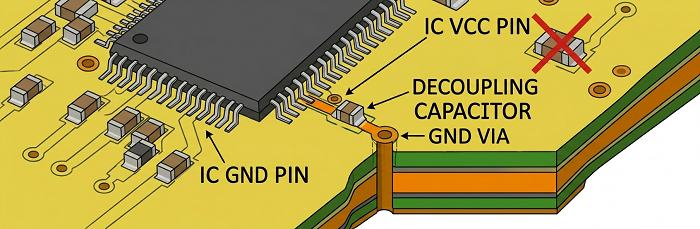

วางตัวเก็บประจุแยกสัญญาณให้ใกล้กับไอซี

ติดตั้งตัวเก็บประจุความถี่สูง (เช่น 0.1 μF) ภายในระยะ 2.54 มม. (100 mil) จากขาพาวเวอร์ของ IC ใช้ลายวงจรที่สั้นและกว้างหรือใช้การต่อผ่านรู (via) โดยตรงเพื่อลดค่าความเหนี่ยวนำพาราซิติก ผสมผสานตัวเก็บประจุขนาดเล็กสำหรับความถี่สูงและตัวเก็บประจุแบบบัลก์ขนาดใหญ่สำหรับการทำให้เสถียรที่ความถี่ต่ำ

ใช้เฟอร์ไรต์บีดและฟิลเตอร์

วางบีดเฟอร์ไรต์ที่ขั้วอินพุตของแหล่งจ่ายไฟเพื่อทำให้สัญญาณรบกวนความถี่สูงอ่อนลงในขณะที่ยังคงให้กระแสตรงผ่านได้ สำหรับพอร์ต I/O และสายไฟ ให้เพิ่มฟิลเตอร์แบบ π หรือฟิลเตอร์แบบ LC เพื่อบล็อก EMI ที่ถูกนำพามาและป้องกันไม่ให้สายเคเบิลกลายเป็นเสาอากาศที่แผ่รังสี

การป้องกันสัญญาณรบกวนและการจัดวางชิ้นส่วน

การป้องกันเชิงกลยุทธ์และการจัดวางชิ้นส่วนช่วยแยกแหล่งกำเนิดสัญญาณรบกวนออกจากวงจรที่มีความไวสูง

แยกวงจรที่มีสัญญาณรบกวนและวงจรที่มีความไวสูงออกจากกัน

วางตัวปรับแรงดันแบบสวิตชิ่ง วงจรนาฬิกา และวงจร RF ให้ห่างจากวงจรแอนะล็อก เซนเซอร์ และตัวรับสัญญาณระดับต่ำ ใช้ระนาบกราวด์หรือร่องกราวด์เพื่อสร้างแนวกั้นการแยกตัว

ใช้การป้องกันในระดับคอมโพเนนต์

ครอบคลุมออสซิลเลเตอร์ โมดูล RF และวงจรสวิตชิ่งด้วยฝาครอบโลหะสำหรับการป้องกันสัญญาณรบกวน ตรวจสอบให้แน่ใจว่าฝาครอบเชื่อมต่อกับระนาบกราวด์อย่างมั่นคงด้วยวิอาหลายจุดเพื่อสร้างกรงฟาราเดย์ที่ต่อเนื่อง

วงแหวนป้องกันและพื้นที่กราวด์

ล้อมรอบร่องรอยสัญญาณที่ไวต่อสัญญาณรบกวนหรือมีสัญญาณรบกวนสูงด้วยวงแหวนการ์ดที่ต่อกราวด์ ใช้พื้นที่ทองแดงกราวด์บนเลเยอร์ด้านนอกและเชื่อมต่อด้วย via ไปยังเพลนกราวด์ภายในเพื่อเพิ่มประสิทธิภาพการกักเก็บสัญญาณรบกวน หลีกเลี่ยงการใช้พื้นที่ทองแดงลอยตัว เพราะอาจทำให้ EMI แย่ลง

การเลือกวัสดุแผ่นวงจรพิมพ์ (PCB)

คุณสมบัติของวัสดุมีผลต่อประสิทธิภาพความถี่สูงและ EMI

เลือกใช้ลามิเนตที่มีค่าคงที่ไดอิเล็กทริก (Dk) ที่เสถียรเพื่อคงการควบคุมอิมพีแดนซ์

ใช้ไดอิเล็กทริกที่บางลงระหว่างเพาเวอร์และกราวด์เพื่อเพิ่มค่าคาปาซิแตนซ์และลดสัญญาณรบกวน

สำหรับการออกแบบความเร็วสูงมาก ควรพิจารณาใช้วัสดุที่มีการสูญเสียต่ำเพื่อลดการลดทอนสัญญาณและการแผ่รังสี

ตรวจสอบประสิทธิภาพ EMI

แม้แต่เลย์เอาต์ที่ดีที่สุดก็ยังต้องมีการตรวจสอบ

ทำการทดสอบก่อนการรับรองด้วยโพรบระยะใกล้เพื่อค้นหาจุดร้อนระหว่างการสร้างต้นแบบ

ดำเนินการทดสอบ EMC อย่างเป็นทางการในห้องปฏิบัติการที่ได้รับการรับรองสำหรับการแผ่รังสีรบกวน การรบกวนแบบนำ และความทนทานต่อสัญญาณรบกวน

ทำซ้ำการออกแบบเลย์เอาต์ตามผลการทดสอบเพื่อแก้ไขปัญหาการเรโซแนนซ์ การแผ่รังสี หรือปัญหาการคัปปลิง

ข้อผิดพลาดที่พบบ่อยที่ควรหลีกเลี่ยง

การเพิกเฉยต่อเส้นทางกลับของสัญญาณและการปล่อยให้เกิดลูปขนาดใหญ่

การแยกพื้นกราวด์ออกจากกันโดยไม่จำเป็น

การวางตัวเก็บประจุแยกให้ห่างจากวงจรรวมมากเกินไป

การจัดเส้นทางสัญญาณความเร็วสูงแบบขนานในระยะทางไกล

ปล่อยให้ขาใช้งานไม่ได้ จุดทดสอบ หรือรอยทางเดินสัญญาณที่ไม่ได้ใช้ลอยอยู่

การเลื่อนการทดสอบ EMI ออกไปจนถึงขั้นตอนการออกแบบขั้นสุดท้าย

บทสรุป

การลด EMI ในเลย์เอาต์ PCB แบบหลายชั้นจำเป็นต้องมีการวางแผนอย่างเป็นระบบในด้านโครงสร้างเลเยอร์ การต่อลงกราวด์ การเดินลาย การกรองสัญญาณ และการป้องกันสัญญาณรบกวน เมื่อดำเนินการตั้งแต่ช่วงต้นของวงจรการออกแบบ วิธีการเหล่านี้จะช่วยปรับปรุง EMC ได้อย่างมีนัยสำคัญ ลดการแก้ไขงาน และเร่งกระบวนการรับรองมาตรฐาน

สำหรับแผงวงจรพิมพ์หลายชั้น (PCB) ระดับมืออาชีพที่มีความน่าเชื่อถือสูง ซึ่งสร้างขึ้นตามมาตรฐานการออกแบบและการผลิตที่ปรับให้เหมาะสมด้าน EMI ให้เลือกพันธมิตรที่มีประสบการณ์ลึกซึ้งด้านความเข้ากันได้ทางแม่เหล็กไฟฟ้าและการผลิตประสิทธิภาพสูง

PCBCartเชี่ยวชาญด้านการผลิตแผ่นวงจรพิมพ์หลายชั้นขั้นสูง (Multi-layer PCB) พร้อมการสนับสนุนอย่างครบถ้วนสำหรับแนวทางการออกแบบเลย์เอาต์แบบ EMI ต่ำ วัสดุคุณภาพสูง และการควบคุมกระบวนการที่เข้มงวด ไม่ว่าคุณจะกำลังพัฒนาอุปกรณ์อิเล็กทรอนิกส์สำหรับผู้บริโภค อุปกรณ์อุตสาหกรรม หรือระบบดิจิทัลความเร็วสูง PCBCart มอบแผ่นวงจรที่ผสานประสิทธิภาพ ความเชื่อถือได้ และการปฏิบัติตามมาตรฐานเข้าไว้ด้วยกัน ด้วย PCBCart คุณสามารถเปลี่ยนเลย์เอาต์ที่ปรับให้เหมาะสมด้าน EMI ของคุณให้กลายเป็นแผ่นวงจรพิมพ์พร้อมผลิตที่ให้ประสิทธิภาพสม่ำเสมอในสภาพแวดล้อมการใช้งานจริง

แหล่งข้อมูลที่เป็นประโยชน์

•การออกแบบ EMC ของแผงวงจรพิมพ์ให้ประสบความสำเร็จตั้งแต่ครั้งแรก

•เคล็ดลับการออกแบบความเร็วสูง

•กลยุทธ์ในการออกแบบการรบกวนระหว่างสายไมโครสตริปแบบขนานสองเส้นบนแผงวงจรพิมพ์ (PCB)

•ความท้าทายด้านความสมบูรณ์ของสัญญาณในการออกแบบแผงวงจรพิมพ์ความเร็วสูงและแนวทางแก้ไข