Moderne elektronische Systeme entwickeln sich mit der Tendenz zu kleinen Gehäusen, großem Integrationsgrad und hoher Geschwindigkeit, da die Packungsdichte der Chips in SLSI (Super-Large-Scale Integration) immer weiter zunimmt. Dies führt zu einigen unvermeidlichen Problemen, etwa der Frage, wie man die Interconnects und Stapelungsprobleme im Hochgeschwindigkeits-Schaltungsdesign analysiert und bewältigt. Derzeit erreichen die Funkfrequenzen elektronischer Produkte Hunderte oder Tausende von MHz, und sowohl die Anstiegs- als auch die Abfallflanken werden so steil, dass die PCB-Layoutregeln und die Dielektrizitätskonstante des Substratmaterials im Prozess der Entwicklung solcher Produkte für die elektrische Leistung des Systems von entscheidender Bedeutung sind.

Als ein bedeutender Prozess und Schritt in der Mehrzahl der aktuellen Forschungsarbeiten zu elektronischen Produkten,Hochgeschwindigkeits‑LeiterplatteBeim Design wurden die Hauptprobleme wie Timing-Probleme, Störrauschen und EMI (elektromagnetische Störungen) festgestellt, deren Lösungen mit dem normalen Betrieb des Systemdesigns zusammenhängen.

Nun führen herkömmliche Entwurfsmethoden zu einer geringen Zuverlässigkeit und Erfolgsquote von Produkten, was der Forschung zum Hochgeschwindigkeits‑PCB‑Design in eingebetteten Anwendungssystemen einen hohen praktischen Wert und breite Markterwartungen verleiht.

Systementwurfschema

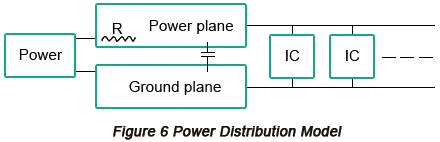

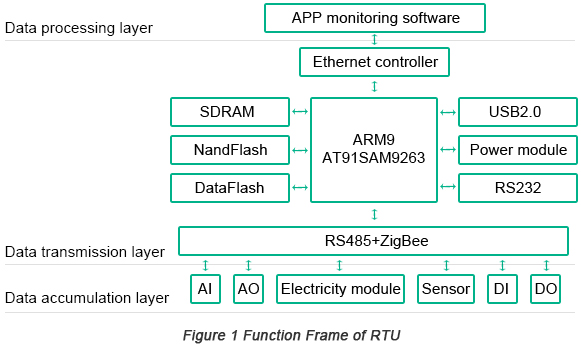

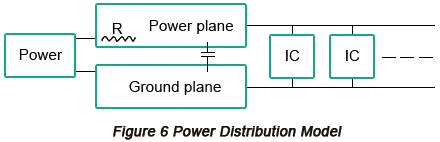

Abbildung 1 zeigt den Funktionsrahmen der eingebetteten RTU (Remote Terminal Unit).

Aus Abbildung 1 ist ersichtlich, dass dieses System eine vertikale Kommunikationsstruktur ist, die aus einer Datensammelschicht besteht, welche die elektrische Energieeinheit, die Sensoreinheit und die analoge Messeinheit umfasst, einer Datenübertragungsschicht, die ein Gateway enthält, das die Daten in der Datensammelschicht anhand von Befehlen aus dem über das Internet angebundenen Ingenieurzentrum anpasst, sowie einer Datenverarbeitungsschicht, die durch eine APP-Überwachungssoftware implementiert wird, Daten in Echtzeit speichert und analysiert und Datenkurven für die Benutzeroberfläche erstellt, sodass die Flexibilität und Verwaltungseffizienz der Datensammlung erhöht werden.

RTU-System-Hardware-Rahmen

Diese eingebettete IoT-RTU-Systemhardware besteht hauptsächlich aus USB 2.0, dem AT91SAM9263-Prozessor, CAN, SDRAM, NAND-Flash, Data-Flash, Ethernet-Controller, Taktchip, RS232/485-Schnittstelle, Stromversorgungsverwaltung und Datenerfassungseinheiten.

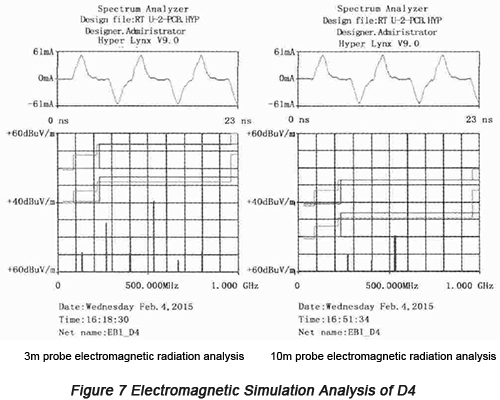

Mit dem Linux-Betriebssystem betrieben, verfügt dieses Design über erweiterte Fähigkeiten in Bezug auf Speicher- und Geräteverwaltung, sodass eine Multi-Missions-Echtzeitplanung implementiert werden kann, die komplexe Algorithmen und Kommunikationsprotokolle umfasst und für Netzwerkverbindung, Datenkommunikation und Konfigurationsspeicherung verantwortlich ist. Abbildung 2 zeigt die in diesem Artikel entworfene RTU-Leiterplatte.

Durch die Unterstützung des Dual-Stacks von IPv6 und IPv4 ist dieses System in der Lage, Promptheit und Echtzeitfähigkeit zu realisieren. Hinsichtlich der Datenspeicherung kann die Anforderung an lokalen Speicher auch bei unterbrochener Kommunikation erfüllt werden. In Bezug auf die Kommunikationsschnittstelle verfügt es über verschiedene Feld-Datenkommunikationsschnittstellen, darunter RS485, RS232 und CAN, unterstützt das Modbus-RTU-Kommunikationsprotokoll und erfüllt die Anforderungen unterschiedlicher Schnittstellen und verschiedener Kommunikationsraten.

PCB-Design des RTU-Systems

• PCB-Stackup-Design des Systems

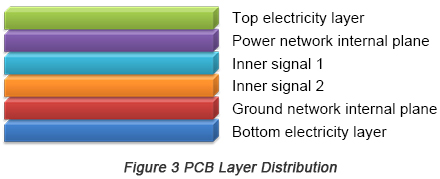

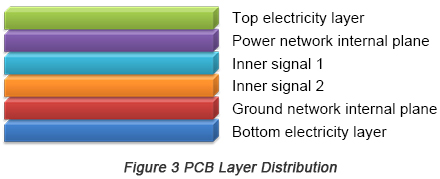

Die Anzahl der Lagen von Leiterplatten liegt je nach Konstruktionsschwierigkeit üblicherweise im Bereich von 2 bis 32. Die 6-lagige Leiterplatte in diesem Design wird auf Grundlage der Bauteilpackungsdichte, des geringen Layout- und Routingraums sowie der hohen Signalfrequenz festgelegt. ThisVerteilung der PCB-Schichtenist in Abbildung 3 unten dargestellt.

In dieser Konfiguration des Systems wird die Strip-Line-Konfiguration für FLASH und SDRAM übernommen, und das Routing wird auf Inner Signal 1 und Inner Signal 2 implementiert.

• Leiterplatten-Einschränkungsregeln in diesem System

Bei der Hochgeschwindigkeits-PCB-Entwicklung werden Impedanzkontinuität und EMI stark von Leiterbahnabstand, -länge und -breite sowie von der benachbarten Ausführung von Schleifen beeinflusst. Die Qualität des Bauteillayouts und der Leiterbahnführung steht in direktem Zusammenhang mit dem Erfolg des endgültigen Designs, daher müssen PCB-Designregeln für Randbedingungen sinnvoll festgelegt werden.

Hyper Lynx verfügt über eine Funktion zur Einbindung in die Diagrammanalyse, und das IBIS-Modell kann angewendet werden, um Verlustübertragung, differenzielle Signale und ein frequenzabhängiges Durchkontaktierungsmodell präzise zu simulieren. Das Hauptnetzwerk wird vor dem Routing mit Line simuliert, um die PCB-Lagenstruktur und die Leitungsimpedanz zu verbessern, und auf Basis der Simulationsergebnisse werden zuvor Hochgeschwindigkeits‑PCB‑Netzwerk‑Routing‑Constraints entworfen, um die Designeffizienz zu erhöhen.

• PCB-Simulation dieses Systems

Im Prozess des Hochgeschwindigkeits-PCB-Designs wird für die Simulation am vorderen Ende ein ideales Übertragungsleitungsmodell verwendet, wobei jeweils nur eine begrenzte Anzahl von Signalleitungen simuliert wird. Die Übertragungsleitungen am hinteren Ende der Leiterplatte sind jedoch in Wirklichkeit Leiterbahnen der PCB, die durch Durchkontaktierungen und Ebenenversätze beeinflusst werden. Unter diesen Umständen ist das erhaltene Simulationsergebnis äußerst zuverlässig.

Im Prozess der Kerndesigns des Systems wird für die Einzelend-Signale eine Abschlusswiderstandsanpassung im Bereich von 40 bis 60 Ω gefordert und der Übersprechschwellenwert zwischen Signalleitungen beträgt 165 mV. Darüber hinaus muss, damit die Netzwerkcontroller DM9000 und DM9161 sich selbst an die Kommunikationsgeschwindigkeit von 100 Mbit/s anpassen können, die differentielle Impedanz im Bereich von 100 ± 5 Ω liegen.PCB-Simulationwird mit der Hyper-Lynx-Simulationssoftware von Mentor Graphics für SDRAM, Ethernet-Differenzleitungen, Power-Integrität und EMV implementiert.

a. SDRAM-Design

Im Prozess des Stripline-Designs sind Übersprechen und Durchkontaktierungen die Hauptursachen für Zeitverzögerungen. Selbst wenn die Leiterplatte gemäß den von Leitungssimulationswerkzeugen festgelegten Routing-Regeln fertiggestellt wird, sind einige Probleme unvermeidlich, wie etwa zu viele Bauteilpins und begrenzte Leiterplattenabmessungen. Daher ist es notwendig, mehrere Netzwerke angemessen mit Boardsimulationswerkzeugen zu simulieren.

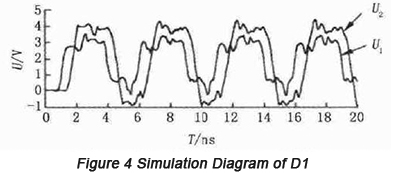

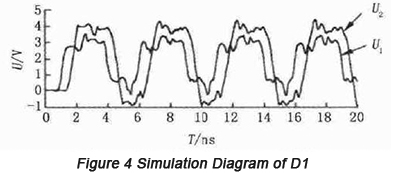

Basierend auf dem Simulationsergebnis liegt die Übersprechintensität des analogen Netzwerks EBI_D0 und EBI_D2 über 165 mV. Die beiden Netzwerke greifen EBI_D1 an und suchen nach Kopplungsstellen, weil der Abstand zwischen den schlangenförmigen Leitungen im gelb markierten Bereich ungeeignet ist. Es lässt sich veranschaulichen, dass eine Vergrößerung des Leiterbahnabstands dazu beitragen wird, ein solches Problem zu beseitigen. Was uns jedoch wirklich interessiert, ist, warum das angegriffene Netzwerk unter so starken Störungen leidet. Der Grund liegt möglicherweise in einer ungeeigneten Widerstandswahl, die zu einer nicht passenden Impedanz führt. Bis jetzt ist der bestimmte Widerstand des Abschlusswiderstands 43,1 Ω. Unter der Anregungsbedingung von 220 MHz ist die Analysesimulationskurve des Netzwerks EBI_D1 in Abbildung 4 unten dargestellt.

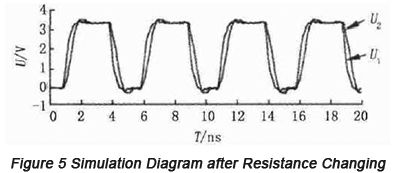

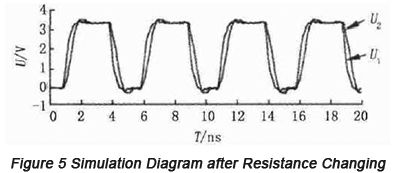

Basierend auf Abbildung 4 tritt eine Impedanzdiskontinuität auf der EMI_D1-Übertragungsleitung auf und es kommt zu einer Verformung der Signalwellen. Obwohl dadurch kein Systemstartfehler verursacht wird, kann die Stabilität des Produktbetriebs kaum gewährleistet werden. Zurück zur Board-Simulation: Durchkontaktierungen und beschädigte Simulation werden angewendet, um den Abschlusswiderstand von EBI_D0 und EBI_D1 auf 46,9 Ω zu ändern. Daher ist das Simulationsdiagramm des Übersprechens nach der Änderung des Widerstands in Abbildung 5 unten dargestellt.

Auf Grundlage dieser Abbildung lässt sich veranschaulichen, dass das Netzwerksignal verbessert wurde und die auf EBI_D1 hervorgerufene Störintensität deutlich verringert wurde.

b. Internet-Differentialbus-Design

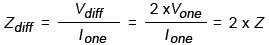

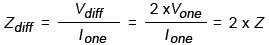

Mit Eigenschaften wie Hochgeschwindigkeits- und 3GIO‑Verbindungen verwendet das von Hyper Lynx entwickelte Boardsimulationsmodul eine ultraschnelle serielle Datenpfad- und Quellensynchronisationstechnologie auf Basis eines differentiellen Signalbusses und bietet damit eine komfortable und hocheffiziente Lösung für das High‑Speed‑PCB‑Design. Sowohl der DM9000 als auch der DM9161 in diesem System verfügen über zwei Paare von Hochgeschwindigkeits‑Differenzsignalbussen: TX+, TX- und RX+, RX- mit einer differentiellen Impedanz von 100 Ω. Aufgrund der Übertragungstheorie kann die differentielle Impedanz anhand der folgenden Formel berechnet werden: .

.

In dieser Formel bezeichnet Z die Übertragungsimpedanz jeder Signalleitung, die einen entscheidenden Einfluss auf die Kommunikationsentfernung und die Störfestigkeit hat. Hier wird der DM9000 verwendet, um differentiell zu den Netzwerkleitungen TP_E_TX+ und TP_E_TX- zu übertragen. Um den Einfluss von Reflexionen zu verringern, wird ein Widerstand von 100 Ω parallel zu den Signalleitungen mit Durchkontaktierungen eingesetzt.

c. Leistungsintegritätsdesign dieses Systems

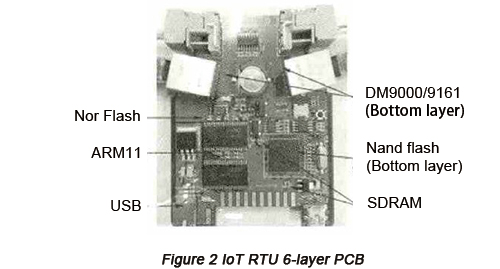

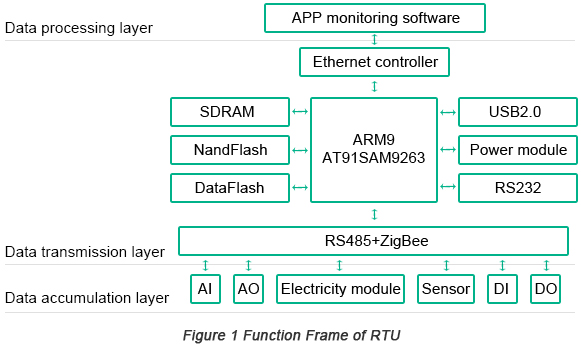

Abbildung 6 zeigt ein grundlegendes Leistungsverteilungsmodell, bei dem der Strom über Leistungsebenen zu jedem Träger und anschließend zur Masseebene übertragen wird.

Im Prozess des Hochgeschwindigkeits-PCB-Designs muss der Energieverbrauch in jeder Einheit im Schaltungssystem berechnet werden, wobei die Breite des Stromversorgungsnetzes korrekt verteilt und angemessen vergrößert wird.

Die Leistungsintegrität von 6 Lagen lässt sich wie folgt zusammenfassen: Der maximale Spannungsabfall beträgt 2,1 mV, was etwa 0,06 % entspricht; die maximale Stromdichte beträgt 16,3 mA/m². Innerhalb eines geeigneten Bereichs führt eine Stromdichte von mehr als 50 mA/m² zu einem Anstieg der PCB-Temperatur, was den Hauptchip und die Signalleitungen während des Betriebs beeinflusst. Eine Vergrößerung der Kupferbreite kann die Stromdichte verringern, und eine Erhöhung der Dicke der Signalleitungen trägt zur Senkung der PCB-Temperatur bei.

d. Systemelektromagnetische Verträglichkeitsanalyse

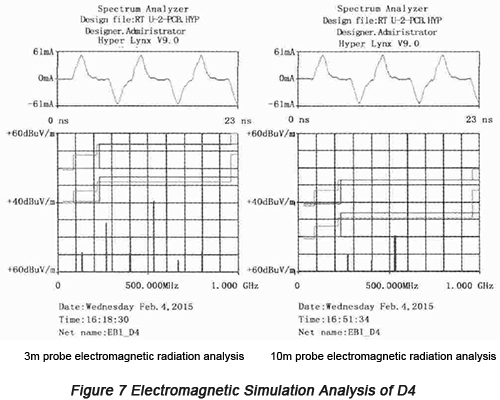

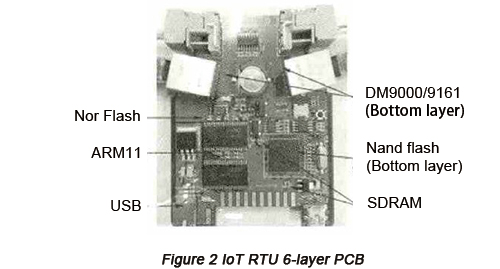

Elektromagnetische Störungen werden in der Regel in Form einer Kopplung als Träger mit Nutzsignalen übertragen. In diesem Design wird die Simulationssoftware Hyper Lynx eingesetzt, um nach dem Vorentwurf die Strahlungsintensität der Leiterplatte (PCB) zu analysieren. Die kritische Signalleitung D4 wird zwischen ARM9 und SDRAM mit Sondenpositionen von 3 m bzw. 10 m erfasst. Bei einer Anregungsquelle von 220 MHz können sowohl FCC- als auch CISPR-Simulationsdaten nach internationalen Standards gewonnen werden, wie in Abbildung 7 unten dargestellt.

Basierend auf den Simulationsergebnissen führt der geringe Abstand zur Leiterplatte zu einer hohen Abstrahlung von der Leiterplatte, und die Abstrahlung ändert sich mit den Signalfrequenzen. Im Prozess des Hochgeschwindigkeits-Schaltungsdesigns kann die Störfestigkeit der Leiterplatte optimiert werden, während die Geräuschabstrahlung reduziert werden muss.

.

.