Mit der großflächigen Integration von 5G‑Kommunikation und KI‑Technologie entwickeln sich elektronische Geräte rasant in Richtung Hochgeschwindigkeitsübertragung, hoher Rechenleistung und hoher Integration. Als zentrales Trägermedium elektronischer Geräte bestimmt die Leiterplatte (PCB) direkt die Betriebseffizienz, Signalstabilität und langfristige Zuverlässigkeit der Endgeräte. Sie ist zur grundlegenden Hardwarebasis für die Unterstützung der Implementierung von Schlüsselanwendungen wie 5G‑Basisstationen, KI‑Servern und intelligenten Endgeräten geworden. Angesichts der doppelten Anforderungen von 5G‑Hochfrequenzsignalübertragung und KI‑Hochdichte-Rechenleistung muss die PCB‑Technologie in den drei grundlegenden Zielen „geringer Verlust, hohe Präzision und starke Unterstützung“ Durchbrüche erzielen und ein umfassendes Innovationssystem aus Materialien, Prozessen und Strukturdesign formen.

I. Übertragung von Hochgeschwindigkeits- und Hochfrequenzsignalen: Überbrückung des „Signalengpasses“ von KI und 5G

Die Millimeterwellen-Frequenzbänder der 5G-Kommunikation (26/28 GHz) und die Anforderungen von KI-Geräten an Hochgeschwindigkeitsverbindungen mit 10 Gbit/s und mehr stellen äußerst hohe Anforderungen an den „geringen Verlust“ und die „hohe Stabilität“ der PCB-Signalübertragung. Herkömmliche Leiterplatten können aufgrund von Materialeigenschaften und prozesstechnischen Einschränkungen die Anforderungen an Signalabschwächung, Reflexion und Übersprechen in Hochfrequenzanwendungen nicht erfüllen und werden damit zu einem entscheidenden Engpass, der die Leistungsfähigkeit von 5G- und KI-Geräten begrenzt.

(I) Hochfrequente „Schwachstellen“ herkömmlicher Leiterplatten

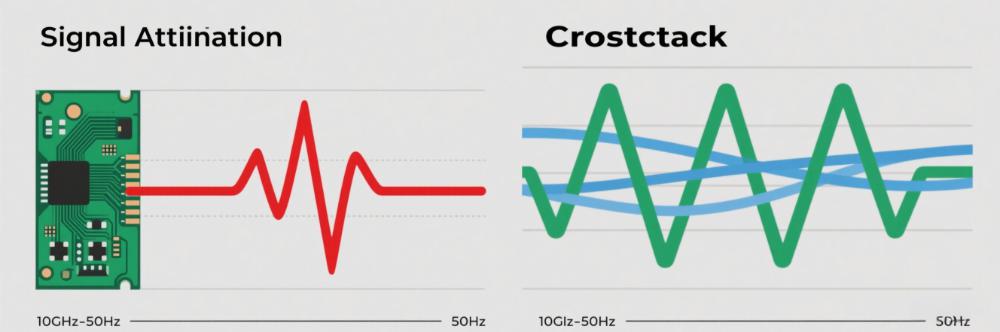

1. Erhöhte Signaldämpfung: Der „Skineffekt“ hochfrequenter Signale konzentriert den Strom an der Oberfläche der Leiter (bei 10 GHz breitet sich der Strom nur innerhalb von 5 μm von der Oberfläche der Kupferschicht aus) und erhöht damit den äquivalenten Widerstand erheblich. Gleichzeitig beträgt der dielektrische Verlustfaktor (tanδ) herkömmlicher FR-4-Substrate bei 10 GHz etwa 0,02 und steigt bei 28 GHz auf 0,03 an, was zu einem Energieverlust von mehr als 60 % für Signale führt, die über mehr als 10 cm übertragen werden, und somit die Anforderungen an die Weitbereichsabdeckung von 5G-Basisstationen nicht erfüllen kann.

2. Schwere Signalstörungen: Die Wellenlänge des Hochfrequenzsignals ist extrem kurz (die Wellenlänge der 28‑GHz-Millimeterwelle liegt in der Größenordnung von 10 mm), und bereits geringe Abweichungen in der Leiterbahnlänge können Phasenverschiebungen verursachen. Elektromagnetische Kopplung (Übersprechen) zwischen benachbarten Leiterbahnen führt zu Signal-„Crosstalk“. Bei einer Datenübertragungsgeschwindigkeit von 10 Gbit/s führt ein Übersprechen von mehr als -20 dB (10 % Signalenergiekopplung) direkt zu Datenübertragungsfehlern. Testergebnisse zeigen, dass das Übersprechen eines herkömmlichen 10‑Gbit/s-Signals bis zu -15 dB betragen kann, während es bei 5G- und KI-orientierten Leiterplatten unter -25 dB gehalten werden muss.

(II) Wege technologischer Durchbrüche: „Doppelte Aufrüstung“ von Verfahren und Materialien

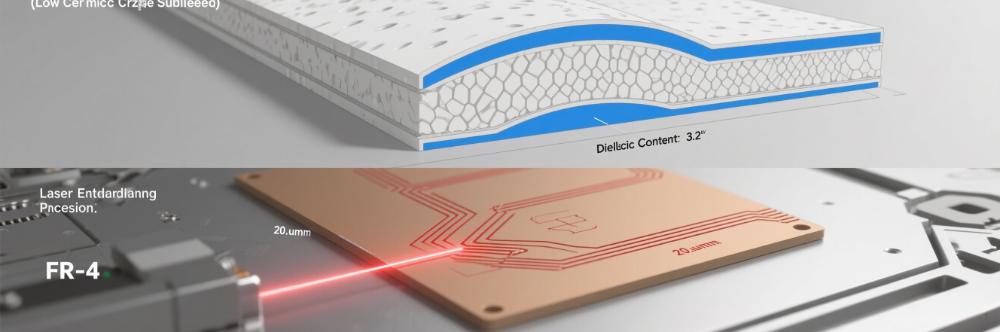

1. Auswahl von verlustarmem Material: Es werden hochfrequente, keramikgefüllte Substrate mit einer Dielektrizitätskonstante Dk = 3,0±0,05 eingesetzt. Für 5G-Millimeterwellen-Mikrobasisstations-PCBs wird der Signalübertragungsverlust im 10-GHz-Frequenzbereich bei 0,25 dB/in gehalten, was einer Verringerung um 45 % im Vergleich zu herkömmlichen FR-4-Substraten entspricht und die Hochfrequenz-Signalübertragungsdistanz nahezu verdoppelt. Gleichzeitig wird „Very Low Profile (VLP)“-Kupferfolie verwendet, um eine Oberflächenrauheit (Ra) von 0,3 μm zu erreichen, wodurch der durch herkömmliche Elektrolytkupferfolie (Ra≈1,5 μm) verursachte „Streuverlust“ des Signals vermieden und der Übertragungsverlust von 28-GHz-Signalen um 15 %–20 % reduziert wird.

2. Optimierung von Hochpräzisionsprozessen: Ein Prozess der „PräzisionImpedanzregelung+ Leitungen mit geringer Rauheit“ ist behoben. Übertragungsleitungen werden mittels Laserätztechnologie mit einer Kantenrauheit von Ra<0,5 μm verarbeitet. Der Reflexionskoeffizient des Signals (S11) im 28‑GHz‑Frequenzband wird auf -30 dB optimiert, was 20 % besser ist als der Branchenstandard, um eine verzerrungsfreie Übertragung von Hochgeschwindigkeitssignalen mit 10 Gbit/s zu ermöglichen. Gleichzeitig wird Laser Direct Imaging (LDI) eingesetzt, um eine Leitungsbreitentoleranz von ±0,005 mm zu erreichen, wobei die Impedanzanpassungsgenauigkeit ±2 % beträgt und damit deutlich besser ist als das ±10 %-Niveau herkömmlicher Leiterplatten. Dadurch wird das Signalreflexionsrisiko prozessseitig reduziert.

(III) Anwendungseffekte: Verbesserung der Leistung von 5G- und KI-Geräten

Testergebnisse eines 5G-Basisstationenherstellers zeigen, dass mit dem hochfrequenzoptimierten HF‑Modul mit größerer Signalabdeckung und verbesserter Ratenstabilität eine um 15 % breitere Signalabdeckung und eine um 30 % höhere Ratenstabilität erreicht wird, wenn mehrere Benutzer gleichzeitig zugreifen. Auf den Hochgeschwindigkeits‑Interconnect‑Verbindungen von AI‑Servern wird die Bitfehlerrate der 10‑Gbps‑Signalübertragung von 1e‑12 (bei herkömmlichen Leiterplatten) auf 1e‑15 reduziert und erfüllt damit die Anforderungen der latenzarmen, KI‑gestützten Echtzeitdatenverarbeitung.

II. Hochdichtes Integrationsdesign: Die „Weltraumrevolution“ zur Ermöglichung von KI-Rechenkapazität

Die kontinuierliche Steigerung der Rechendichte von KI‑Chips (wobei die Rechenleistung eines einzelnen Chips bei mehr als Dutzenden von TOPS liegt) hat Leiterplatten (PCBs) in Richtung „hohe Dichte und kleine Baugröße“ vorangetrieben. Standard‑PCBs sind durch die Leiterbahndichte und die Chipintegration begrenzt und können keinen Parallelbetrieb vieler Hochleistungsrechenchips realisieren. Fortschritte bei Integrationsengpässen erfordern Durchbrüche im strukturellen Design.

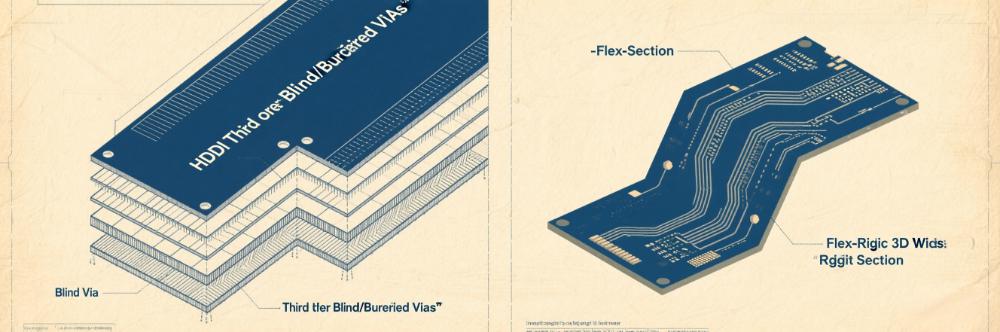

(I) Zentrale technologische Innovationen

1. HDI-Drittordnungs-Blind- und -Buried-Via-Technologie: Durch eine 0,1-mm-Microvia-Prozesstechnologie wird die Leiterbahndichte in einer Leiterplatte auf 200 Leiterbahnen/cm² erhöht, 50 % mehr als bei Standard-Leiterplatten. In einer Leiterplatte für eine KI-Beschleunigerkarte unterstützt diese Technologie problemlos bis zu 8 Hochleistungsrechner-Chips, erhöht die Rechendichte auf 20 TOPS/cm² und bietet hochdichte Rechenleistung für KI-Inferenzaufgaben.

2. Flex-Rigid-Kombination + 3D-Verkabelung: Es wird eine 3D-Verkabelungsstruktur eingesetzt, die starre Hauptplatinen über flexible Komponenten verbindet, wodurch die Anzahl der Steckverbinder um 60 % und der Signalübertragungsweg um 30 % reduziert werden und die Signallaufzeit innerhalb von 50 ns gehalten wird. Für intelligente Terminal-PCBs erfüllt diese Struktur nicht nur die Anforderungen an Gerätedünnheit und -leichtbau, sondern stellt auch die Reaktionsgeschwindigkeit für die Echtzeit-AI-Interaktion sicher.

In Serveranwendungen für Edge Computing weist die Hochdichte-Integrationstechnologie eine Flächennutzung von 40 % der Leiterplatte auf und unterstützt die parallele Datenverarbeitung über 16 Kanäle. Damit erfüllt sie die doppelten Anforderungen an „kleine Baugröße und hohe Rechenleistung“ für KI-Echtzeitinferenz und stellt eine Hardwareplattform für die Bereitstellung von KI in Edge-Szenarien bereit.

III. Optimierung der Rechenleistung: Durchbrechen des „Kühlungs- und Stromversorgungsdilemmas“ von KI-Geräten

Die tiefgreifenden Energieverbrauchseigenschaften von KI‑Geräten (Leistungsaufnahme eines einzelnen Chips von bis zu 300 W) stellen enorme Herausforderungen an die Wärmeableitungsleistung und die Stromversorgungsstabilität von Leiterplatten dar. Bei verzögerter Wärmeabfuhr steigt die Sperrschichttemperatur des Chips an, was zu einem Rückgang der Rechenleistung führt; übermäßige Welligkeit der Stromversorgung kann die unmittelbaren Leistungsanforderungen von Hochleistungsrechenchips nicht erfüllen. Struktur- und Schaltungsdesign müssen gleichzeitig optimiert werden, um diese Einschränkungen zu überwinden.

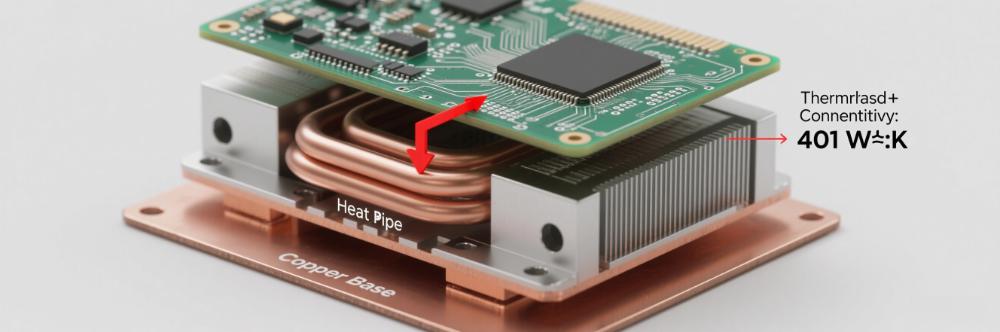

(I) Innovation von Wärmeableitungslösungen

Es wird eine Verbund-Wärmeableitungsstruktur aus „Kupferbasis + eingebetteten Heatpipes“ aufgebaut, wobei die Wärmeleitfähigkeit der Leiterplatte auf 5 W/(m·K) erhöht wird, was einem Anstieg von 60 % im Vergleich zu herkömmlichen Aluminium-Substraten entspricht. In einer AI-Server-Leiterplatte kann diese Struktur die Chipübergangstemperatur bei einer Umgebungstemperatur von 40 ℃ auf unter 85 ℃ regeln und so den durch hohe Temperaturen verursachten Rückgang der Rechenfrequenz unterdrücken.

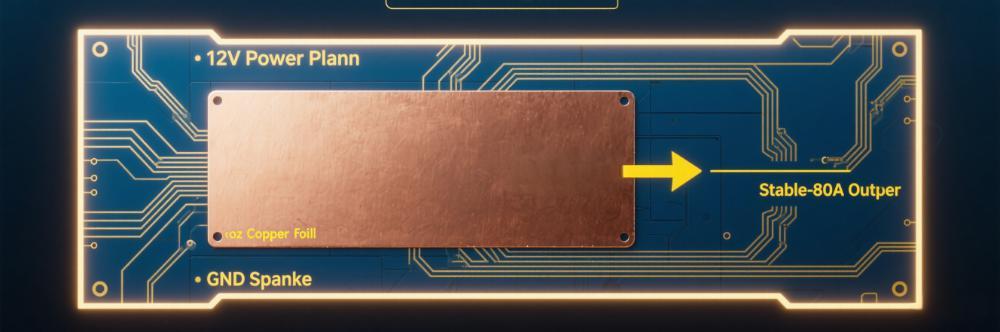

(II) Optimierung von Stromverteilungsnetzen

Es verwendet eine 2oz dicke Kupferfolie und ein mehrgruppiges Power-Plane-Design, um das Stromverteilungsnetzwerk zu maximieren, die Welligkeit der Stromversorgung innerhalb von ±2 % zu halten und einen zuverlässigen Hochstromausgang von 12 V/80 A bereitzustellen. In einer PCB-AI-Training-Karte erfüllt die Lösung die Anforderungen des momentanen Stromverbrauchs von Hochleistungsrechenchips, verbessert den zuverlässigen Betrieb der Training-Karte unter langfristiger hoher Last um 40 % und erhöht die Auslastungsrate der Rechenleistung von 85 % auf 95 %.