El sistema electrónico moderno se está desarrollando con la tendencia de encapsulados pequeños, gran escala y alta velocidad, a medida que la densidad de los chips aumenta cada vez más en la SLSI (integración a súper gran escala), lo que trae consigo problemas inevitables, como cómo analizar y manejar las interconexiones y los problemas de apilamiento en el diseño de circuitos de alta velocidad. En la actualidad, la frecuencia de radio de los productos electrónicos alcanza cientos o miles de MHz y tanto el flanco de subida como el de bajada se vuelven tan pronunciados que las reglas de diseño del trazado de PCB y la constante dieléctrica del material del sustrato son extremadamente cruciales para el rendimiento eléctrico del sistema en el proceso de diseño de dichos productos.

Como un proceso y paso significativo en la mayoría de las investigaciones actuales de productos electrónicos,PCB de alta velocidadEl diseño ha presentado los principales problemas, incluyendo el problema de temporización, la interferencia de ruido y las EMI (interferencias electromagnéticas), cuyas soluciones están relacionadas con el funcionamiento normal del diseño del sistema.

Ahora, los métodos de diseño tradicionales conducen a una baja fiabilidad y tasa de éxito de los productos, lo que otorga un alto valor práctico y amplias expectativas de mercado a la investigación sobre el diseño de PCBs de alta velocidad en sistemas de aplicación embebidos.

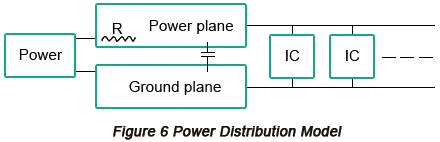

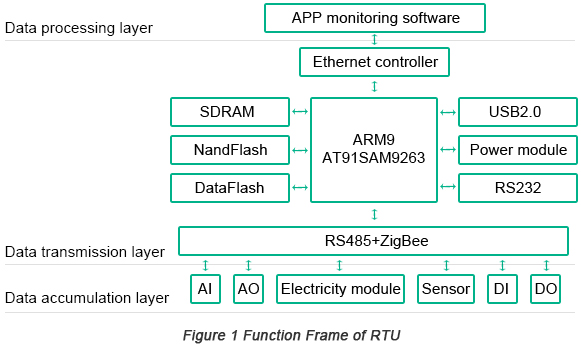

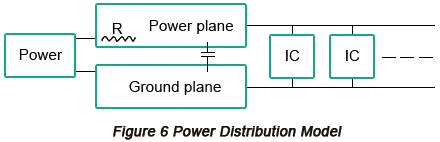

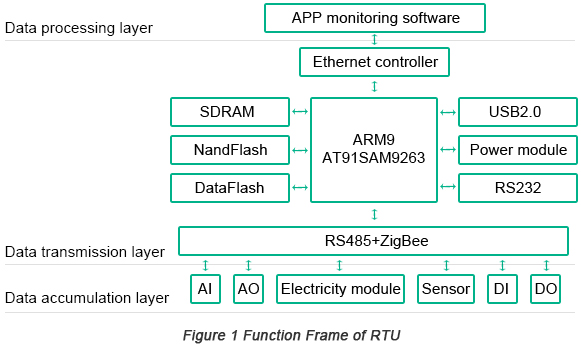

La Figura 1 muestra el marco funcional de la RTU (unidad terminal remota) incrustada.

A partir de la Figura 1, se puede ver que este sistema es una estructura de comunicación vertical compuesta por una capa de acumulación de datos que contiene la unidad de energía eléctrica, la unidad de sensores y la unidad de medición de magnitudes analógicas; una capa de transmisión de datos que contiene la pasarela que ajusta los datos en la capa de acumulación de datos mediante las órdenes procedentes del centro de ingeniería receptor de Internet; y una capa de procesamiento de datos que se implementa mediante el software de supervisión de la aplicación (APP), almacena y analiza los datos en tiempo real y genera curvas de datos orientadas a la interfaz de usuario, de modo que se incrementan la flexibilidad y la eficiencia de gestión de la acumulación de datos.

Este hardware de sistema RTU IoT embebido consiste principalmente en USB2.0, procesador AT91SAM9263, CAN, SDRAM, Nand Flash, Data Flash, controlador Ethernet, chip de reloj, interfaz RS232/485, administración de energía y partes de acumulación de datos.

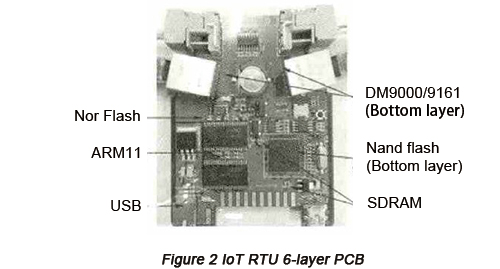

Operado por el sistema operativo Linux, este diseño ofrece mayores capacidades de administración de memoria y dispositivos, de modo que se implementa una planificación en tiempo real para múltiples misiones que incluye algoritmos complejos y protocolos de comunicación, encargados de la conexión de red, la comunicación de datos y la acumulación de configuraciones. La Figura 2 muestra la placa de circuito de la RTU diseñada en este artículo.

Al admitir la doble pila de IPv6 e IPv4, este sistema es capaz de implementar la inmediatez y la capacidad en tiempo real. En cuanto al almacenamiento de datos, el requisito de almacenamiento local puede cumplirse en condiciones de interrupción de la comunicación. En cuanto a la interfaz de comunicación, dispone de diferentes interfaces de comunicación de datos de campo, incluidas RS485, RS232 y CAN, es compatible con el protocolo de comunicación Modbus RTU y satisface los requisitos de diferentes interfaces y diferentes velocidades de comunicación.

• Diseño de apilamiento de PCB del sistema

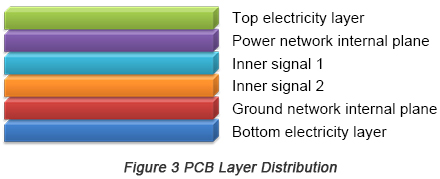

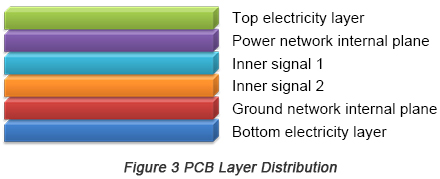

El número de capas de las PCB suele estar en el rango de 2 a 32 según la dificultad del diseño. La PCB de 6 capas en este diseño se determina de acuerdo con la densidad de encapsulado de los componentes, el reducido espacio de enrutamiento del diseño y la alta frecuencia de la señal. EstaDistribución de capas de PCBse ilustra en la Figura 3 a continuación.

En este sistema se adopta la configuración de líneas en tiras para FLASH y SDRAM, y el ruteo se implementa en Inner Signal 1 e Inner Signal 2.

• Reglas de restricciones de PCB en este sistema

Durante el diseño de PCB de alta velocidad, la continuidad de la impedancia y las EMI están fuertemente influenciadas por el espaciado, la longitud y el ancho de las pistas, así como por el tratamiento de los bucles adyacentes. La calidad de la disposición de los componentes y del ruteo está relacionada con el éxito del diseño final, por lo que las reglas de restricción de la PCB deben establecerse de manera razonable.

Hyper Lynx cuenta con una funcionalidad que permite intervenir en el análisis de diagramas, y el modelo IBIS puede aplicarse para simular con precisión la transmisión de pérdidas, las señales diferenciales y el modelo de vías que varía con la frecuencia. La red principal se simula antes del ruteo mediante Line para mejorar la estructura de apilado del PCB y la impedancia de ruteo, y las reglas de restricción de ruteo de redes de PCB de alta velocidad se diseñan antes de la simulación de resultados para aumentar la eficiencia del diseño.

• Simulación de PCB de este sistema

En el proceso de diseño de PCB de alta velocidad, se aplica un modelo de línea de transmisión ideal para la simulación del terminal frontal, con un número limitado de líneas de señal simuladas a la vez. Sin embargo, las líneas de transmisión en el terminal posterior de la PCB son en realidad pistas de enrutamiento de la PCB, con la influencia de los orificios pasantes y el desplazamiento de planos. Bajo estas circunstancias, el resultado de la simulación obtenido es extremadamente fiable.

En el proceso de diseño del circuito central del sistema, se requiere que la resistencia de adaptación de terminal de la señal de un solo terminal esté en el rango de 40 a 60 Ω y que el valor umbral de diafonía entre líneas de señal sea de 165 mV. Además, para que los controladores de red DM9000 y DM9161 se adapten automáticamente a la velocidad de comunicación de 100 Mbps, la impedancia diferencial debe estar dentro de la categoría de 100 ± 5 Ω.Simulación de PCBse implementa mediante el software de simulación Hyper Lynx desarrollado por Mentor Graphic en SDRAM, líneas diferenciales Ethernet, integridad de potencia y EMC.

a. Diseño de SDRAM

En el proceso de diseño de líneas strip, la diafonía y los orificios pasantes son las principales causas que provocan retrasos de tiempo. Aunque la PCB se complete de acuerdo con las reglas de ruteo determinadas por las herramientas de simulación de líneas, algunos problemas son inevitables, como el exceso de pines de componentes y las dimensiones limitadas de la PCB. Por lo tanto, es necesario simular adecuadamente múltiples redes mediante herramientas de simulación de placas.

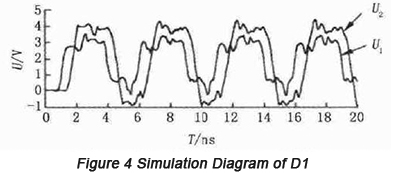

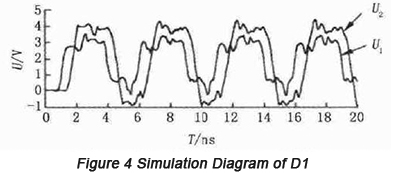

Según el resultado de la simulación, la intensidad de diafonía de la red analógica EBI_D0 y EBI_D2 supera los 165 mV. Las dos redes atacan a EBI_D1 y buscan el lugar de acoplamiento porque el espaciado es inadecuado entre las líneas en forma de serpiente en el área marcada en amarillo. Se puede ilustrar que el aumento del espaciado de ruteo ayudará a eliminar dicho problema. Sin embargo, lo que realmente nos preocupa es por qué la red hack sufre una interferencia tan fuerte. La razón posiblemente radica en la elección inadecuada del resistor que conduce a una impedancia no coincidente. Hasta ahora, la resistencia determinada del resistor de terminación es de 43,1 Ω. Bajo la condición de excitación de 220 MHz, la forma de onda de simulación de análisis de la red EBI_D1 se muestra en la Figura 4 a continuación.

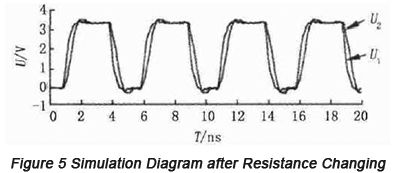

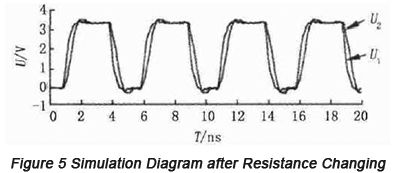

Según la Figura 4, se produce una discontinuidad de impedancia en la línea de transmisión EMI_D1 y se produce una deformación en las ondas de señal. Aunque no puede causar un fallo de arranque del sistema, difícilmente se puede garantizar la estabilidad del funcionamiento del producto. Volviendo a la simulación de la placa, se aplican orificios pasantes y simulación de daños para cambiar la resistencia terminal de EBI_D0 y EBI_D1 a 46,9 Ω. Por lo tanto, el diagrama de simulación de la diafonía después del cambio de resistencia se muestra en la Figura 5 a continuación.

Basado en esta figura, se puede ilustrar que la señal de red ha mejorado y que la intensidad de interferencia generada en EBI_D1 se ha reducido de manera evidente.

b. Diseño de bus diferencial de Internet

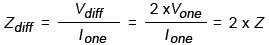

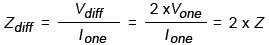

Con atributos de alta velocidad e interconexiones 3GIO, el módulo de simulación de placas desarrollado por Hyper Lynx aplica una ruta de datos serie ultrarrápida y tecnología de sincronización de origen basada en un bus de señal diferencial, proporcionando una solución conveniente y altamente efectiva para el diseño de PCB de alta velocidad. Tanto el DM9000 como el DM9161 en este sistema tienen dos pares de buses diferenciales de señales de alta velocidad: TX+, TX- y RX+, RX- con una impedancia diferencial de 100 Ω. Debido a la teoría de transmisión, la impedancia diferencial puede calcularse según la fórmula: .

.

En esta fórmula, Z se refiere a la impedancia de transmisión de cada línea de señal, que tiene un efecto crucial en la distancia de comunicación y en la capacidad de resistencia al ruido. Aquí se selecciona el DM9000 para transmitir de forma diferencial a la red TP_E_TX+ y TP_E_TX-. Para reducir el efecto de la reflexión, se coloca una resistencia de 100 Ω en paralelo con las líneas de señal, aplicando orificios pasantes.

c. Diseño de integridad de potencia de este sistema

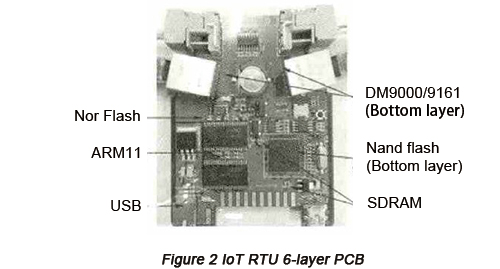

La Figura 6 es un modelo básico de distribución de energía en el que la corriente se transmite a cada portador a través de las capas de alimentación y luego a la capa de tierra.

En el proceso de diseño de PCB de alta velocidad, es necesario calcular el consumo de energía en cada unidad dentro del sistema de circuito, distribuyendo correctamente el ancho de la red de alimentación y ampliándolo de manera adecuada.

La integridad de potencia de las 6 capas puede resumirse de la siguiente manera: la caída de tensión máxima es de 2,1 mV, cercana al 0,06%; la densidad máxima de corriente es de 16,3 mA/m²; dentro de una categoría adecuada, si la densidad de corriente supera los 50 mA/m², la temperatura de la PCB aumentará, lo que influye en el chip principal y en las líneas de señal durante el proceso de funcionamiento. El aumento del ancho del cobre es capaz de disminuir la densidad de corriente y el incremento del grosor de las pistas de señal ayuda a reducir la temperatura de la PCB.

d. Análisis de compatibilidad electromagnética del sistema

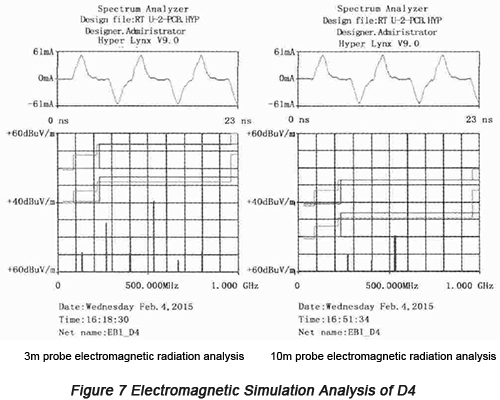

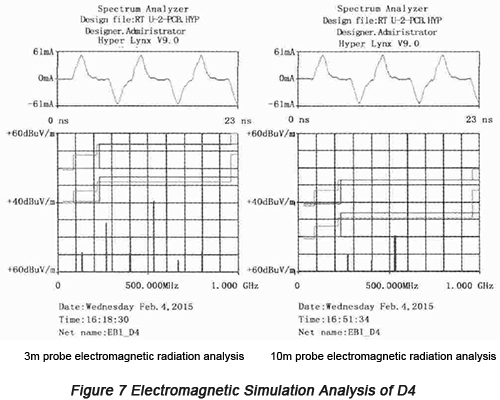

La interferencia electromagnética suele transmitirse como un portador con señales útiles por medio de acoplamiento. En este diseño, se aplica el software de simulación Hyper Lynx para analizar la intensidad de radiación de la PCB después del diseño preliminar. La línea de señal crucial, D4, se toma entre el ARM9 y la SDRAM con posiciones de sonda a 3 m y 10 m respectivamente. Bajo la condición de una fuente de excitación de 220 MHz, se pueden obtener los datos de simulación de las normas internacionales FCC y CISPR, que se muestran en la Figura 7 a continuación.

Según los resultados de la simulación, la corta distancia a la PCB provoca una alta radiación de la placa de circuito y la radiación varía con el cambio de las frecuencias de la señal. En el proceso de diseño de circuitos de alta velocidad, se puede optimizar la inmunidad a interferencias de la PCB, mientras que la radiación de ruido debe reducirse.

.

.