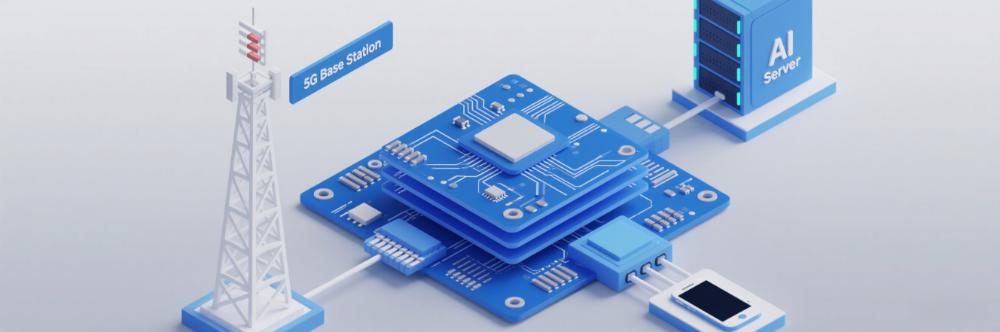

Con la integración a gran escala de la comunicación 5G y la tecnología de IA, los dispositivos electrónicos están evolucionando rápidamente hacia la transmisión de alta velocidad, el soporte de alta capacidad de cómputo y la alta integración. Como portador central de los dispositivos electrónicos, la placa de circuito impreso (PCB) determina directamente la eficiencia de funcionamiento, la estabilidad de la señal y la fiabilidad a largo plazo de los equipos terminales. Se ha convertido en la base de hardware subyacente para apoyar el despliegue de aplicaciones clave como estaciones base 5G, servidores de IA y terminales inteligentes. Ante los requisitos de transmisión de señales de alta frecuencia del 5G y las demandas de alta densidad de potencia de cómputo de la IA, la tecnología de PCB necesita lograr avances en los tres objetivos básicos de “baja pérdida, alta precisión y gran capacidad de soporte” y formar un sistema de innovación integral que abarque materiales, procesos y diseño estructural.

I. Transmisión de señales de alta velocidad y alta frecuencia: superando el “cuello de botella de señal” de la IA y el 5G

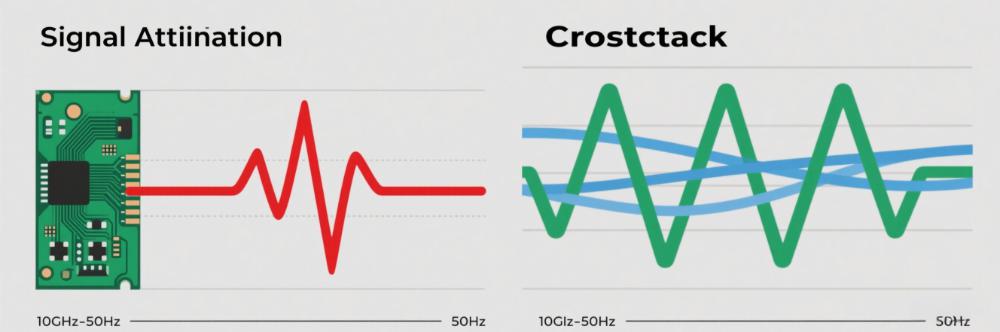

Las bandas de frecuencia de ondas milimétricas de comunicación 5G (26/28 GHz) y las necesidades de interconexión de alta velocidad de más de 10 Gbps de los equipos de IA imponen exigencias muy altas sobre la “baja pérdida” y la “alta estabilidad” de la transmisión de señales en las PCB. Las PCB convencionales, debido a las limitaciones de las propiedades de los materiales y de los procesos, no pueden cumplir con los requisitos de atenuación de señal, reflexión y diafonía en aplicaciones de alta frecuencia, convirtiéndose así en un cuello de botella clave que restringe el rendimiento de los dispositivos 5G e IA.

(I) "Deficiencias" de alta frecuencia de los PCB ordinarios

1. Mayor atenuación de la señal: El “efecto piel” de las señales de alta frecuencia tiende a concentrar la corriente en la superficie de los conductores (a 10 GHz la corriente solo se distribuye dentro de 5 μm de la superficie de la capa de cobre), lo que incrementa significativamente la resistencia equivalente. Al mismo tiempo, la tangente de pérdida dieléctrica (tanδ) de los sustratos FR-4 estándar es de aproximadamente 0,02 a 10 GHz y aumenta a 0,03 a 28 GHz, lo que provoca una pérdida de energía superior al 60 % para señales que viajan más de 10 cm, incapaz de satisfacer las demandas de cobertura de larga distancia de las estaciones base 5G.

2. Grave interferencia de señal: La longitud de onda de la señal de alta frecuencia es extremadamente corta (la longitud de onda de la onda milimétrica de 28 GHz es del orden de 10 mm), y pequeñas variaciones en la longitud de la línea pueden producir desplazamientos de fase. El acoplamiento electromagnético (diafonía) entre líneas adyacentes provoca “diafonía” de la señal. Cuando la velocidad de transmisión de datos es de 10 Gbps, si la diafonía es superior a -20 dB (acoplamiento del 10 % de la energía de la señal), esto conducirá directamente a errores en la transmisión de datos. Los resultados de las pruebas muestran que la diafonía de una señal común de 10 Gbps puede llegar a -15 dB, mientras que en las PCB orientadas a 5G y a IA debe mantenerse por debajo de -25 dB.

(II) Rutas de avances tecnológicos: "doble actualización" de procesos y materiales

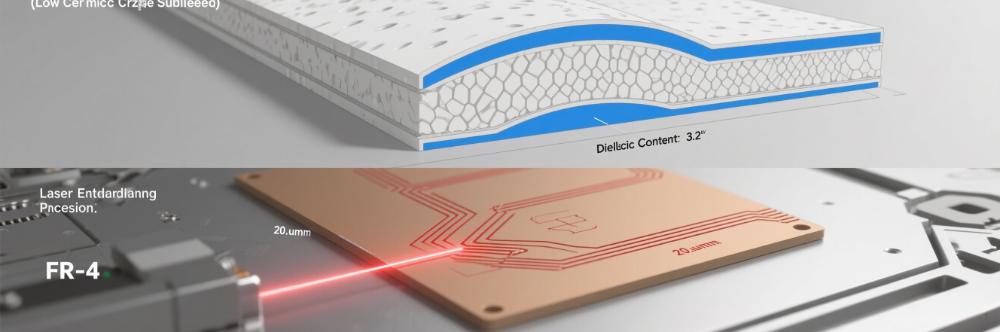

1. Selección de material de baja pérdida: Se emplean sustratos cerámicos de alta frecuencia con constante dieléctrica Dk = 3,0±0,05. Para las PCB de microestaciones base 5G de ondas milimétricas, la pérdida de transmisión de señal en el rango de frecuencia de 10 GHz se mantiene en 0,25 dB/in, lo que supone una disminución del 45% en comparación con los sustratos tradicionales FR-4 y prácticamente duplica la distancia de transmisión de señales de alta frecuencia. Al mismo tiempo, se utiliza “cobre de perfil muy bajo (VLP)” para controlar la rugosidad superficial (Ra) de 0,3 μm, lo que evita la “pérdida por dispersión” de la señal causada por el cobre electrolítico general (Ra≈1,5 μm) y reduce la pérdida de transmisión de señales de 28 GHz en un 15%-20%.

2. Optimización de procesos de alta precisión: Un proceso de "precisióncontrol de impedancia+ Las líneas de baja rugosidad" están corregidas. Las líneas de transmisión se procesan utilizando tecnología de grabado láser con una rugosidad de borde Ra<0,5μm. El coeficiente de reflexión de la señal (S11) en la banda de frecuencia de 28GHz se optimiza a -30dB, lo que es un 20% mejor que el nivel de la industria, para permitir la transmisión no distorsionada de señales de alta velocidad de 10Gbps. Al mismo tiempo, se utiliza la tecnología de imagen directa por láser (LDI) para lograr un control de desviación del ancho de línea de ±0,005mm, con una precisión de coincidencia de impedancia que alcanza ±2%, muy superior al nivel de ±10% de las PCB convencionales, reduciendo el riesgo de reflexión de la señal desde el lado del proceso.

(III) Efectos de la aplicación: Mejora del rendimiento de los dispositivos 5G y de IA

Los resultados de las pruebas de un fabricante de equipos de estaciones base 5G demuestran que se ha logrado un módulo RF optimizado para altas frecuencias, con una cobertura de señal más amplia y una estabilidad de tasa mejorada, obteniendo un 15% más de cobertura de señal y un 30% más de estabilidad de tasa cuando varios usuarios acceden simultáneamente. En los enlaces de interconexión de alta velocidad de los servidores de IA, la tasa de error de bit de la transmisión de señal de 10 Gbps se reduce de 1e-12 (con PCB comunes) a 1e-15, cumpliendo los requisitos de procesamiento de datos en tiempo real de IA con baja latencia.

II. Diseño de Integración de Alta Densidad: La "Revolución Espacial" que Potencia la Capacidad de Cómputo de IA

La mejora continua en la densidad de potencia de cómputo de los chips de IA (con la potencia de cómputo de un solo chip superando varias decenas de TOPS) ha impulsado a las PCB a desarrollarse hacia una “alta densidad y tamaño reducido”. Las PCB estándar están limitadas por la densidad de cableado y la integración de chips y no pueden implementar el funcionamiento en paralelo de muchos chips de alta potencia de cómputo. Los avances en los cuellos de botella de integración requieren avances en el diseño estructural.

(I) Innovaciones Tecnológicas Fundamentales

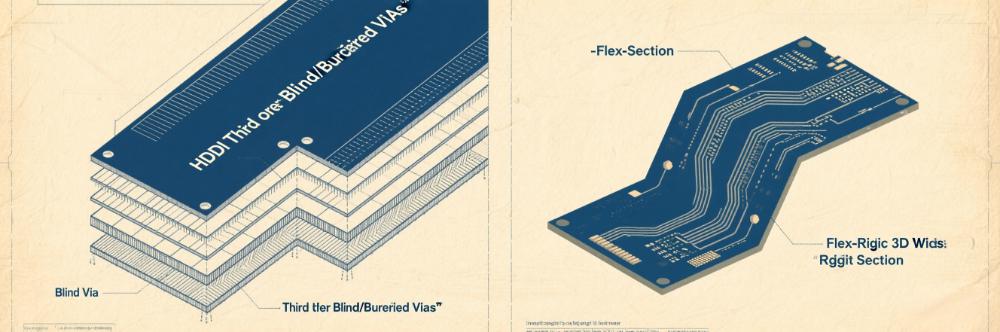

1. Tecnología HDI de vías ciegas y enterradas de tercer orden: Mediante una tecnología de procesado de microvías de 0,1 mm, la densidad de cableado en una PCB se incrementa a 200 líneas/cm², un 50% más que las PCBs estándar. En una PCB para una tarjeta aceleradora de IA, esta tecnología admite sin dificultad hasta 8 chips de alta potencia de cómputo, aumentando la densidad de potencia de cálculo a 20 TOPS/cm² y proporcionando un soporte de potencia de cómputo de alta densidad para tareas de inferencia de IA.

2. Combinación flexible-rígida + cableado 3D: Se emplea una estructura de cableado 3D que conecta placas base rígidas mediante componentes flexibles, reduciendo los conectores en un 60%, la ruta de transmisión de señal en un 30% y controlando el retardo de señal dentro de los 50 ns. Para las PCB de terminales inteligentes, esta estructura no solo satisface la demanda de dispositivos delgados y ligeros, sino que también garantiza la velocidad de respuesta para la interacción de IA en tiempo real.

En aplicaciones de servidor para computación perimetral, la tecnología de integración de alta densidad asigna el 40% del área de la PCB y admite el procesamiento de datos en paralelo de 16 canales, satisfaciendo las demandas duales de «tamaño reducido y gran potencia de cómputo» para la inferencia de IA en tiempo real y proporcionando una plataforma de hardware para el despliegue de IA en escenarios de borde.

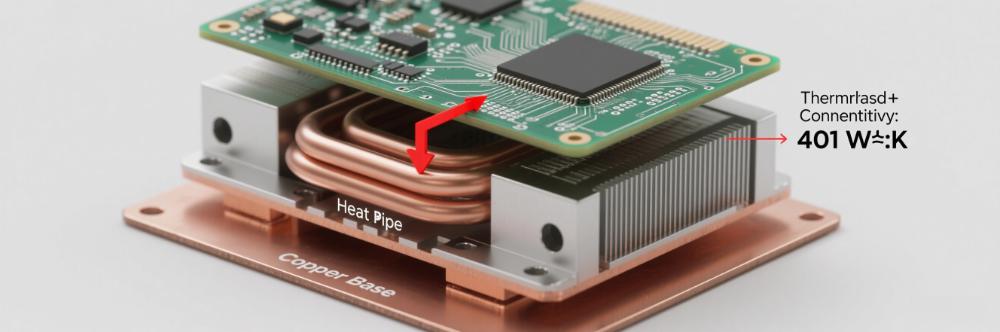

III. Optimización del soporte de potencia de cómputo: Romper el “dilema de disipación de calor y suministro de energía” del equipo de IA

Las profundas características de consumo de energía de los equipos de IA (con un consumo de hasta 300 W por chip) imponen enormes desafíos al rendimiento de disipación de calor y a la estabilidad de la fuente de alimentación de las PCB. Si la disipación de calor se retrasa, la temperatura de unión del chip aumentará, lo que provocará una disminución de la capacidad de cómputo; un rizado excesivo de la fuente de alimentación no puede satisfacer las demandas instantáneas de consumo de energía de los chips de alta potencia de cómputo. Es necesario optimizar simultáneamente el diseño de la estructura y del circuito para superar estas limitaciones.

(I) Innovación de soluciones de disipación de calor

Se ha construido una estructura compuesta de disipación de calor de “base de cobre + tubos de calor incrustados”, con la conductividad térmica de la PCB mejorada a 5 W/(m·K), un aumento del 60% en comparación con los sustratos de aluminio tradicionales. En una PCB de servidor de IA, esta estructura puede regular la temperatura de unión del chip por debajo de 85 ℃ a una temperatura ambiente de 40 ℃, suprimiendo la disminución de la frecuencia de potencia de cómputo causada por las altas temperaturas.

(II) Optimización de las redes de distribución de energía

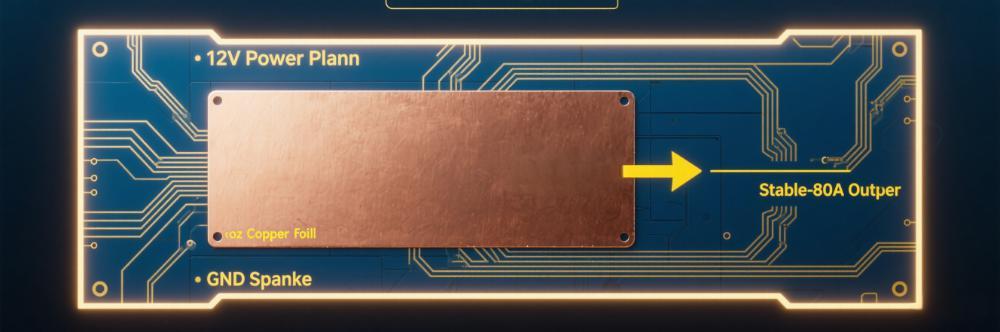

Utiliza una lámina de cobre de 2 oz de espesor y un diseño de plano de alimentación de múltiples grupos para maximizar la red de distribución de energía, controlando el rizado de la fuente de alimentación dentro de ±2% y proporcionando una salida confiable de alta corriente de 12V/80A. En una tarjeta de entrenamiento de IA con PCB, la solución satisface las demandas de consumo de energía instantáneo de los chips de alta capacidad de cómputo, mejorando en un 40% el funcionamiento fiable de la tarjeta de entrenamiento bajo carga alta a largo plazo y aumentando la tasa de utilización de la capacidad de cómputo del 85% al 95%.