Le système électronique moderne évolue vers des boîtiers de petite taille, une grande intégration et une haute vitesse, à mesure que la densité des puces augmente de plus en plus dans les SLSI (intégration à très grande échelle), ce qui entraîne des problèmes inévitables tels que l’analyse et le traitement des interconnexions et des problèmes d’empilement dans la conception de circuits à haute vitesse. À l’heure actuelle, la fréquence radio des produits électroniques atteint des centaines voire des milliers de MHz, et les fronts montant et descendant deviennent si abrupts que les règles de routage des PCB et la constante diélectrique du matériau du substrat sont extrêmement cruciales pour les performances électriques du système lors de la conception de tels produits.

En tant qu’étape et processus important dans la majorité des recherches actuelles sur les produits électroniques,PCB haute vitesseLa conception a mis en évidence les principaux problèmes, notamment les problèmes de synchronisation, les interférences de bruit et les EMI (interférences électromagnétiques), dont les solutions sont liées au fonctionnement normal de la conception du système.

Aujourd’hui, les méthodes de conception traditionnelles entraînent une faible fiabilité et un faible taux de réussite des produits, ce qui confère une grande valeur pratique et de larges perspectives de marché à la recherche sur la conception de PCB haute vitesse dans les systèmes d’application embarqués.

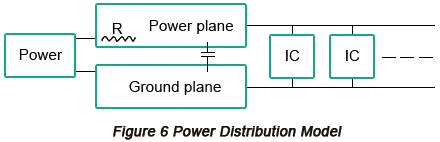

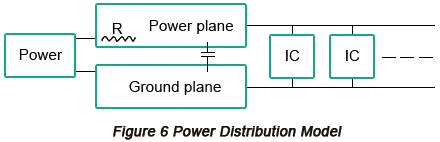

La figure 1 montre le cadre fonctionnel de l’UTR (unité terminale distante) embarquée.

À partir de la Figure 1, on peut voir que ce système est une structure de communication verticale composée d’une couche d’accumulation de données contenant une unité d’énergie électrique, une unité de capteurs et une unité de mesure de grandeurs analogiques, d’une couche de transmission de données contenant une passerelle qui ajuste les données de la couche d’accumulation de données via les commandes provenant du centre d’ingénierie recevant Internet, et d’une couche de traitement de données mise en œuvre par un logiciel de surveillance sous forme d’application, permettant de stocker et d’analyser les données en temps réel et de générer des courbes de données destinées à l’interface utilisateur, de sorte que la flexibilité et l’efficacité de gestion de l’accumulation de données soient accrues.

Le matériel de ce système RTU IoT embarqué se compose principalement d’USB2.0, du processeur AT91SAM9263, de CAN, de SDRAM, de Nand Flash, de Data Flash, du contrôleur Ethernet, d’une puce d’horloge, d’une interface RS232/485, de la gestion de l’alimentation et des modules d’accumulation de données.

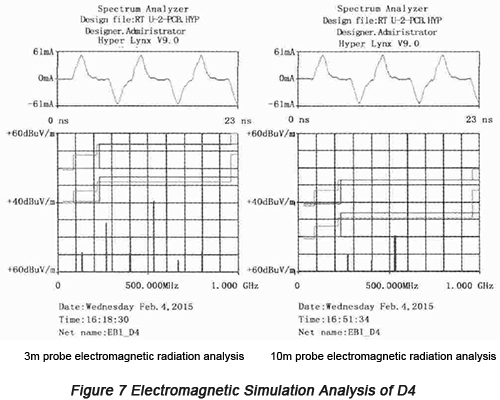

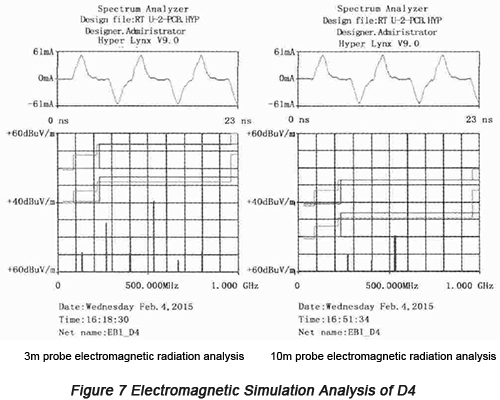

Fonctionnant sous le système d’exploitation Linux, cette conception offre des capacités accrues de gestion de la mémoire et des périphériques, de sorte qu’une planification temps réel multi-missions est mise en œuvre, intégrant des algorithmes complexes et des protocoles de communication chargés de la connexion réseau, de la communication de données et de l’accumulation de configurations. La figure 2 présente la carte de circuit RTU conçue dans cet article.

Prenant en charge la double pile IPv6 et IPv4, ce système est capable d’assurer la rapidité et les capacités temps réel. En termes de stockage de données, l’exigence de stockage local peut être satisfaite en cas de coupure de communication. En ce qui concerne l’interface de communication, il dispose de différentes interfaces de communication de données terrain, notamment RS485, RS232 et CAN, prenant en charge le protocole de communication Modbus RTU et répondant aux exigences de différentes interfaces et de différents débits de communication.

• Conception de l’empilement de PCB du système

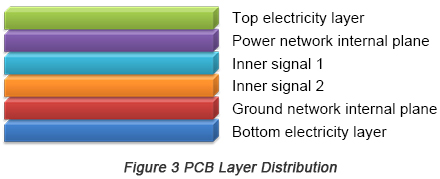

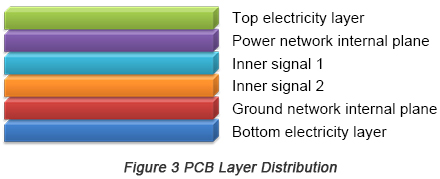

Le nombre de couches des circuits imprimés se situe généralement entre 2 et 32 en fonction de la complexité de la conception. Le circuit imprimé à 6 couches de cette conception est déterminé en fonction de la densité d’encapsulation des composants, du faible espace de routage du schéma d’implantation et de la haute fréquence des signaux. ThisRépartition des couches de PCBest illustré à la figure 3 ci-dessous.

La configuration des lignes de bande est appliquée à la FLASH et à la SDRAM dans ce système, et le routage est réalisé sur Inner Signal 1 et Inner Signal 2.

• Règles de contraintes de PCB dans ce système

Lors de la conception de circuits imprimés à haute vitesse, la continuité d’impédance et les interférences électromagnétiques (EMI) sont fortement influencées par l’espacement, la longueur et la largeur des pistes ainsi que par le traitement des boucles adjacentes. La qualité du placement des composants et du routage est liée au succès de la conception finale, il est donc nécessaire d’établir des règles de contraintes PCB de manière raisonnable.

Hyper Lynx dispose d’une fonctionnalité permettant d’intervenir dans l’analyse des schémas, et le modèle IBIS peut être appliqué pour simuler avec précision la transmission des pertes, les signaux différentiels et le modèle de vias variant avec la fréquence. Le réseau principal est simulé avant le routage par piste afin d’améliorer la structure d’empilage du PCB et l’impédance de routage, et des règles de contraintes de routage de réseaux PCB haute vitesse sont définies avant la simulation des résultats pour accroître l’efficacité de la conception.

• Simulation du PCB de ce système

Dans le processus de conception de PCB à haute vitesse, un modèle de ligne de transmission idéale est appliqué pour la simulation du terminal avant, avec un nombre limité de lignes de signal simulées à la fois. Les lignes de transmission au terminal arrière du PCB, cependant, sont en réalité des pistes de routage du PCB, influencées par les vias et les décalages de plans. Dans ces circonstances, le résultat de simulation obtenu est extrêmement fiable.

Dans le processus de conception du circuit central du système, la résistance d’adaptation en terminaison du signal à une seule extrémité doit être comprise entre 40 et 60 Ω et la valeur seuil de diaphonie entre les lignes de signal est de 165 mV. De plus, afin de permettre aux contrôleurs réseau DM9000 et DM9161 de s’adapter automatiquement à la vitesse de communication de 100 Mbps, l’impédance différentielle doit se situer dans la plage de 100 ± 5 Ω.Simulation de PCBest mis en œuvre par le logiciel de simulation Hyper Lynx développé par Mentor Graphic sur la SDRAM, les lignes différentielles Ethernet, l’intégrité de puissance et la CEM.

a. Conception de SDRAM

Dans le processus de conception de lignes en bande (stripline), la diaphonie et les vias constituent les principales causes de retard de propagation. Même si le PCB est réalisé conformément aux règles de routage déterminées par les outils de simulation de lignes, certains problèmes sont inévitables, tels qu’un trop grand nombre de broches de composants et des dimensions limitées du PCB. Il est donc nécessaire de simuler de manière appropriée plusieurs réseaux à l’aide d’outils de simulation de carte.

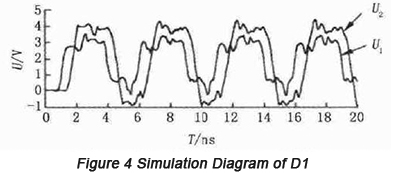

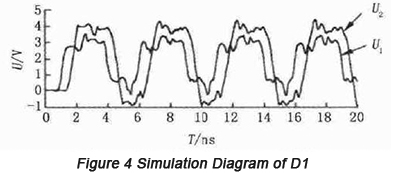

D’après le résultat de la simulation, l’intensité de diaphonie du réseau analogique EBI_D0 et EBI_D2 dépasse 165 mV. Les deux réseaux attaquent EBI_D1 et recherchent un point de couplage parce que l’espacement est inadapté entre les lignes en forme de serpent dans la zone marquée en jaune. Il peut être démontré que l’augmentation de l’espacement de routage aidera à éliminer ce problème. Cependant, ce qui nous importe réellement, c’est pourquoi le réseau hack subit une interférence aussi forte. La raison réside possiblement dans un choix de résistance inadapté entraînant une impédance non adaptée. Jusqu’à présent, la résistance déterminée de la résistance de terminaison est de 43,1 Ω. Sous l’excitation de 220 MHz, l’onde de simulation d’analyse du réseau EBI_D1 est montrée sur la Figure 4 ci-dessous.

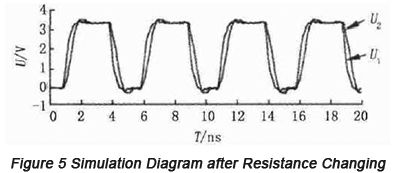

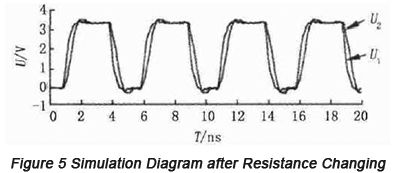

D’après la Figure 4, une discontinuité d’impédance se produit sur la ligne de transmission EMI_D1 et une déformation affecte les ondes de signal. Bien qu’elle ne puisse pas provoquer une défaillance de démarrage du système, la stabilité du fonctionnement du produit ne peut guère être garantie. En revenant à la simulation de la carte, des trous traversants et une simulation de dommages sont appliqués pour modifier la résistance terminale de EBI_D0 et EBI_D1 à 46,9 Ω. Par conséquent, le schéma de simulation de la diaphonie après la modification de la résistance est présenté dans la Figure 5 ci-dessous.

D’après cette figure, il apparaît que le signal réseau a été amélioré et que l’intensité des interférences générées sur EBI_D1 a été nettement réduite.

b. Conception de bus différentiel Internet

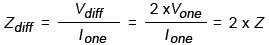

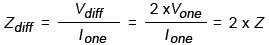

Avec des caractéristiques de haute vitesse et d’interconnexions 3GIO, le module de simulation de carte développé par Hyper Lynx applique une technologie de chemin de données série ultra-rapide et de synchronisation de source basée sur un bus de signaux différentiels, offrant une solution pratique et hautement efficace pour la conception de PCB haute vitesse. Le DM9000 et le DM9161 de ce système possèdent chacun deux paires de bus différentiels de signaux haute vitesse : TX+, TX- et RX+, RX- avec une impédance différentielle de 100 Ω. En raison de la théorie de la transmission, l’impédance différentielle peut être calculée selon la formule : .

.

Dans cette formule, Z désigne l’impédance de transmission de chaque ligne de signal, ayant un effet crucial sur la distance de communication et la capacité de résistance au bruit. Ici, le DM9000 est choisi pour transmettre en différentiel vers le réseau TP_E_TX+ et TP_E_TX-. Afin de réduire l’effet de réflexion, une résistance de 100 Ω est placée en parallèle sur les lignes de signal, avec des trous traversants appliqués.

c. Conception de l’intégrité de puissance de ce système

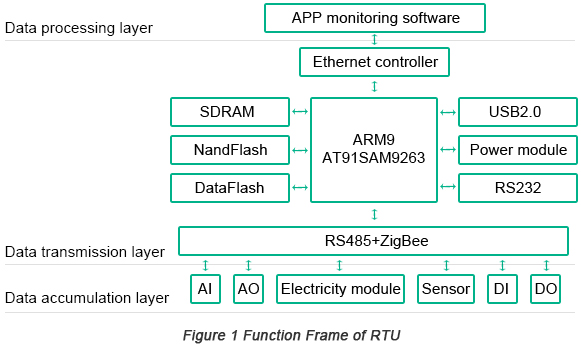

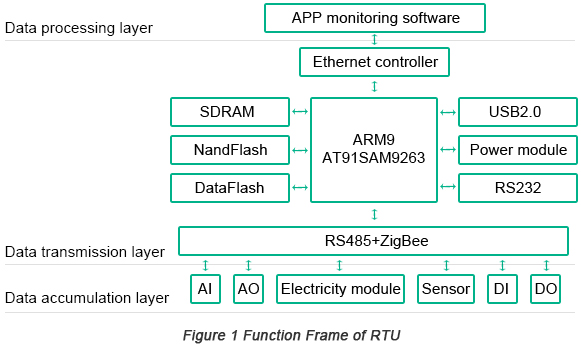

La figure 6 présente un modèle de distribution d’alimentation de base dans lequel le courant est transmis à chaque support par les couches d’alimentation, puis à la couche de masse.

Dans le processus de conception de PCB à haute vitesse, la consommation d’énergie de chaque unité doit être calculée dans le système de circuit, avec une largeur du réseau d’alimentation correctement répartie et convenablement amplifiée.

L’intégrité de puissance des 6 couches peut être résumée comme suit : la chute de tension maximale est de 2,1 mV, soit environ 0,06 % ; la densité de courant maximale est de 16,3 mA/m² ; dans une certaine plage, si la densité de courant dépasse 50 mA/m², la température du PCB augmentera, ce qui influence la puce principale et les lignes de signal pendant le fonctionnement. L’augmentation de la largeur du cuivre permet de réduire la densité de courant et l’augmentation de l’épaisseur des pistes de signal contribue à la diminution de la température du PCB.

d. Analyse de la compatibilité électromagnétique du système

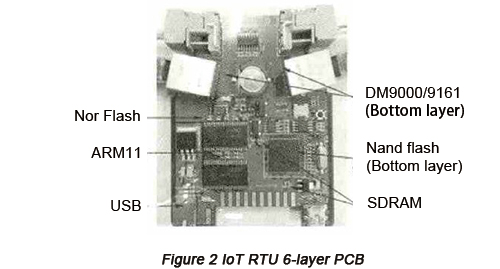

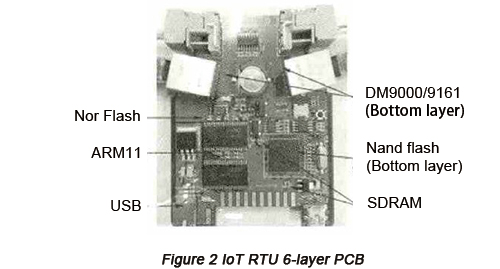

Les interférences électromagnétiques sont généralement transmises sous forme de porteuse avec des signaux utiles par couplage. Dans cette conception, le logiciel de simulation Hyper Lynx est utilisé pour analyser l’intensité de rayonnement du PCB après la conception préliminaire. La ligne de signal cruciale, D4, est sélectionnée entre l’ARM9 et la SDRAM avec des positions de sonde à 3 m et 10 m respectivement. Dans la situation d’une source d’excitation de 220 MHz, les données de simulation selon les normes internationales FCC et CISPR peuvent être obtenues, comme illustré à la Figure 7 ci-dessous.

Sur la base des résultats de simulation, la courte distance au PCB entraîne une forte radiation provenant de la carte de circuit imprimé et cette radiation varie avec la variation des fréquences du signal. Dans le processus de conception de circuits à haute vitesse, l’anti-interférence du PCB peut être optimisée tandis que le rayonnement de bruit doit être réduit.

.

.