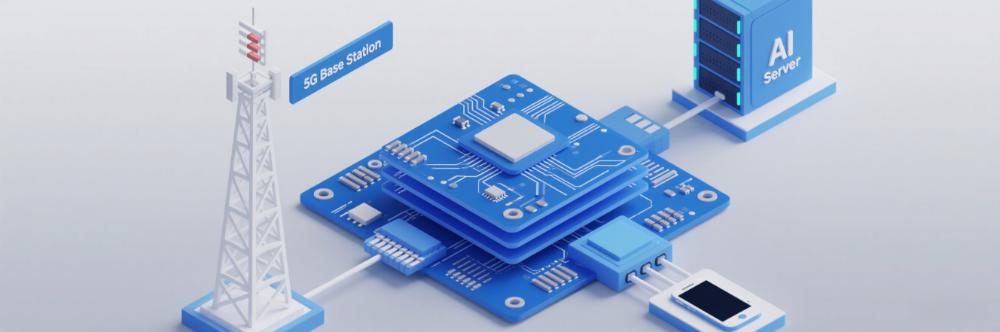

Avec l’intégration à grande échelle des communications 5G et de la technologie d’IA, les dispositifs électroniques évoluent rapidement vers une transmission à haute vitesse, un support de calcul haute performance et une forte intégration. En tant que support central des dispositifs électroniques, le circuit imprimé (PCB) détermine directement l’efficacité de fonctionnement, la stabilité du signal et la fiabilité à long terme des équipements terminaux. Il est devenu la base matérielle sous-jacente pour soutenir le déploiement d’applications clés telles que les stations de base 5G, les serveurs d’IA et les terminaux intelligents. Face aux exigences de transmission de signaux haute fréquence de la 5G et aux besoins de puissance de calcul à haute densité de l’IA, la technologie des PCB doit réaliser des percées autour de trois objectifs fondamentaux — « faibles pertes, haute précision et forte capacité de support » — et former un système d’innovation global couvrant les matériaux, les procédés et la conception structurelle.

I. Transmission de signaux à haute vitesse et haute fréquence : combler le « goulot d’étranglement des signaux » de l’IA et de la 5G

Les bandes de fréquences millimétriques de communication 5G (26/28 GHz) et les besoins d’interconnexion à très haut débit de plus de 10 Gbit/s des équipements d’IA imposent des exigences très élevées en matière de « faible perte » et de « haute stabilité » pour la transmission des signaux sur les PCB. Les PCB ordinaires, en raison des propriétés des matériaux et des contraintes de procédé, ne peuvent pas satisfaire aux exigences de performance en termes d’atténuation, de réflexion et de diaphonie des signaux dans les applications à haute fréquence, devenant ainsi un goulot d’étranglement majeur qui limite les performances des dispositifs 5G et d’IA.

(I) « Insuffisances » à haute fréquence des circuits imprimés ordinaires

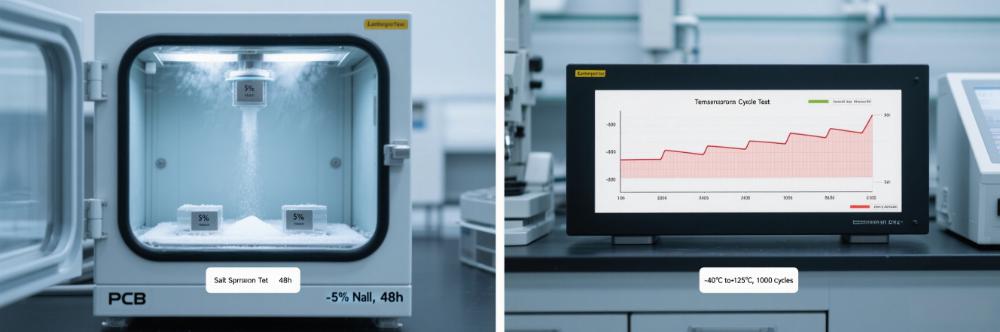

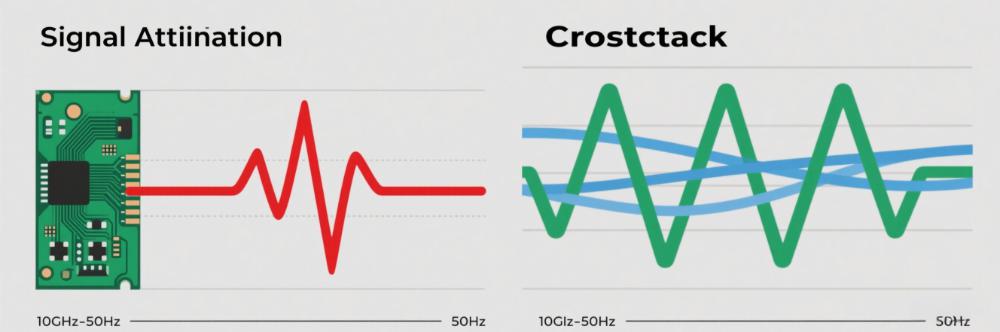

1. Atténuation accrue du signal : l’« effet de peau » des signaux haute fréquence tend à concentrer le courant à la surface des conducteurs (à 10 GHz, le courant ne se répartit que dans une couche de 5 μm à partir de la surface de la couche de cuivre), ce qui augmente considérablement la résistance équivalente. Parallèlement, la tangente de perte diélectrique (tanδ) des substrats FR-4 standard est d’environ 0,02 à 10 GHz et augmente à 0,03 à 28 GHz, entraînant une perte d’énergie de plus de 60 % pour les signaux parcourant plus de 10 cm, ce qui ne permet pas de répondre aux exigences de couverture longue distance des stations de base 5G.

2. Interférences graves du signal : La longueur d’onde du signal haute fréquence est extrêmement courte (la longueur d’onde de l’onde millimétrique à 28 GHz est de l’ordre de 10 mm), et de légères variations de longueur de ligne peuvent produire des déphasages. Le couplage électromagnétique (diaphonie) entre les lignes adjacentes entraîne une « diaphonie » du signal. Lorsque la vitesse de transmission des données est de 10 Gbps, si la diaphonie est supérieure à -20 dB (couplage de 10 % de l’énergie du signal), cela conduit directement à des erreurs de transmission de données. Les résultats des tests montrent que la diaphonie d’un signal 10 Gbps classique peut atteindre -15 dB, tandis que celle des circuits imprimés destinés à la 5G et à l’IA doit être maintenue en dessous de -25 dB.

(II) Voies de percée technologique : « double montée en gamme » des procédés et des matériaux

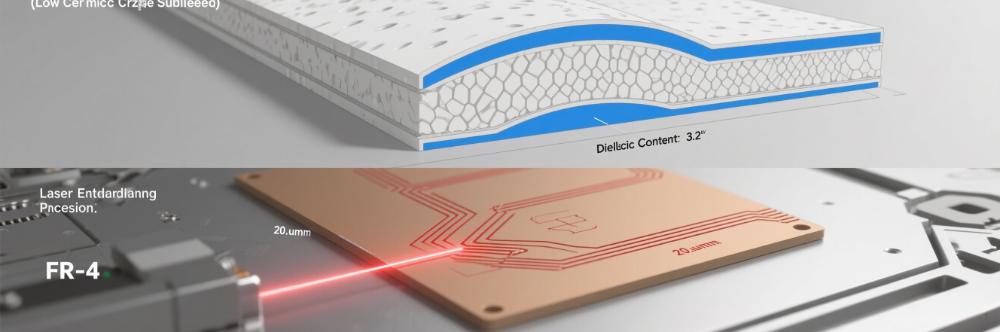

1. Sélection de matériaux à faibles pertes : des substrats céramiques chargés haute fréquence avec une constante diélectrique Dk = 3,0±0,05 sont utilisés. Pour les circuits imprimés de micro-stations de base 5G millimétriques, la perte de transmission du signal dans la plage de fréquence de 10 GHz est maintenue à 0,25 dB/pouce, soit une diminution de 45 % par rapport aux substrats FR-4 traditionnels, ce qui double pratiquement la distance de transmission des signaux haute fréquence. Parallèlement, un « cuivre à très faible rugosité (VLP, Very Low Profile) » est utilisé pour contrôler la rugosité de surface (Ra) à 0,3 μm, ce qui évite la « perte par diffusion » du signal causée par le cuivre électrolytique classique (Ra≈1,5 μm) et réduit la perte de transmission des signaux à 28 GHz de 15 % à 20 %.

2. Optimisation des procédés de haute précision : Un procédé de « précisioncommande d’impédanceLes lignes à faible rugosité sont optimisées. Les lignes de transmission sont traitées par une technologie de gravure laser avec une rugosité de bord Ra < 0,5 μm. Le coefficient de réflexion du signal (S11) dans la bande de fréquence de 28 GHz est optimisé à -30 dB, soit 20 % de mieux que le niveau industriel, permettant une transmission non déformée de signaux haut débit de 10 Gbps. Parallèlement, la technologie d’imagerie directe par laser (LDI) est utilisée pour obtenir un contrôle de la déviation de largeur de ligne de ±0,005 mm, avec une précision d’adaptation d’impédance atteignant ±2 %, bien supérieure au niveau de ±10 % des PCB classiques, ce qui réduit le risque de réflexion du signal du point de vue du procédé.

(III) Effets de l’application : amélioration des performances des appareils 5G et d’IA

Les résultats de tests d’un fabricant d’équipements de stations de base 5G démontrent que le module RF optimisé pour les hautes fréquences, avec une couverture de signal plus large et une stabilité de débit améliorée, permet d’atteindre une couverture de signal 15 % plus étendue et une stabilité de débit 30 % plus élevée lorsque plusieurs utilisateurs sont connectés simultanément. Sur les liaisons d’interconnexion à haute vitesse des serveurs d’IA, le taux d’erreurs binaires de la transmission de signaux à 10 Gbps est réduit de 1e-12 (avec des PCB classiques) à 1e-15, répondant aux exigences de traitement de données en temps réel pour l’IA à faible latence.

II. Conception à haute densité d’intégration : la « révolution spatiale » permettant la capacité de calcul de l’IA

L’amélioration continue de la densité de puissance de calcul des puces d’IA (la puissance de calcul d’une seule puce dépassant plusieurs dizaines de TOPS) a poussé les PCB à évoluer vers une « haute densité et une petite taille ». Les PCB standards sont limités par la densité de routage et l’intégration des puces et ne peuvent pas réaliser un fonctionnement parallèle sur de nombreuses puces à haute puissance de calcul. Les progrès dans le dépassement des goulets d’étranglement liés à l’intégration nécessitent des percées en matière de conception structurelle.

(I) Innovations technologiques fondamentales

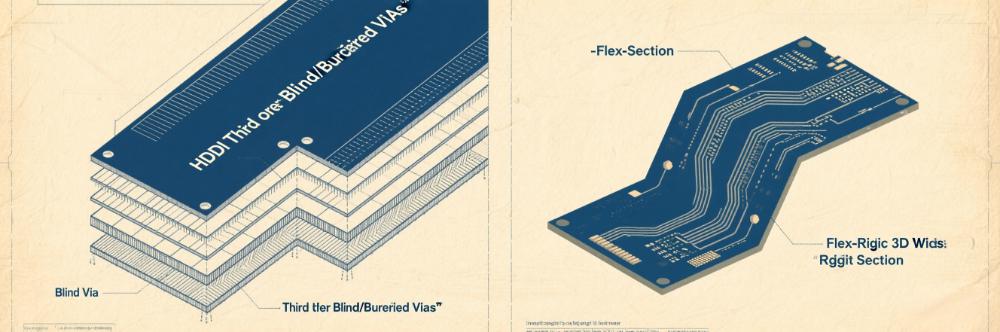

1. Technologie de vias aveugles et enterrés HDI de troisième ordre : grâce à une technologie de traitement de microvias de 0,1 mm, la densité de câblage d’un PCB est portée à 200 lignes/cm², soit 50 % de plus que les PCB standards. Dans un PCB pour une carte accélératrice d’IA, cette technologie permet de prendre en charge jusqu’à 8 puces à haute puissance de calcul sans difficulté, augmentant la densité de puissance de calcul à 20 TOPS/cm² et offrant un support de puissance de calcul haute densité pour les tâches d’inférence IA.

2. Combinaison flexible-rigide + câblage 3D : une structure de câblage 3D reliant les cartes mères rigides par des composants flexibles est utilisée, réduisant les connecteurs de 60 %, le trajet de transmission du signal de 30 % et maintenant le délai de signal en dessous de 50 ns. Pour les PCB de terminaux intelligents, cette structure répond non seulement aux exigences de finesse et de légèreté des appareils, mais garantit également la vitesse de réponse pour l’interaction IA en temps réel.

Dans les applications serveur pour l’edge computing, la technologie d’intégration à haute densité alloue 40 % de la surface du PCB et prend en charge le traitement parallèle de données sur 16 canaux, répondant à la double exigence de « petite taille et grande puissance de calcul » pour l’inférence IA en temps réel et fournissant une plateforme matérielle pour le déploiement de l’IA dans des scénarios en périphérie.

III. Optimisation du support de puissance de calcul : briser le « dilemme de dissipation thermique et d’alimentation électrique » des équipements d’IA

Les caractéristiques de consommation électrique élevée des équipements d’IA (consommation pouvant atteindre 300 W par puce) imposent d’énormes défis aux performances de dissipation thermique et à la stabilité de l’alimentation des circuits imprimés (PCB). En cas de dissipation thermique retardée, la température de jonction de la puce augmente, entraînant une baisse de la puissance de calcul ; une ondulation excessive de l’alimentation ne peut pas répondre aux besoins instantanés en consommation d’énergie des puces à haute puissance de calcul. La conception de la structure et des circuits doit être optimisée simultanément pour surmonter ces contraintes.

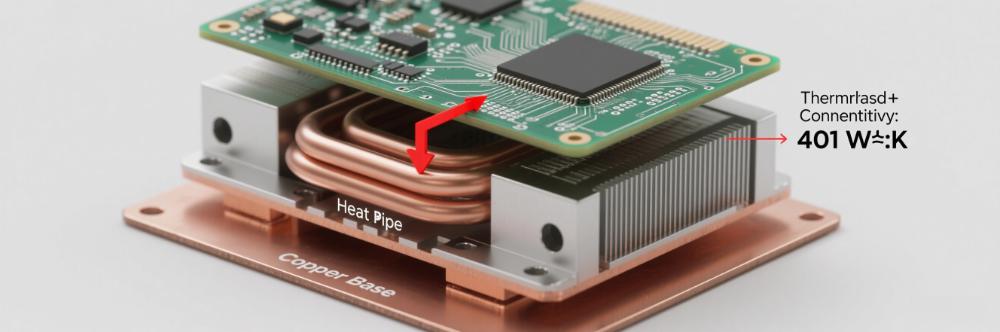

(I) Innovation des solutions de dissipation thermique

Une structure composite de dissipation thermique « base en cuivre + caloducs intégrés » est construite, avec une conductivité thermique du PCB portée à 5 W/(m·K), soit une augmentation de 60 % par rapport aux substrats en aluminium traditionnels. Dans un PCB de serveur IA, cette structure peut réguler la température de jonction de la puce en dessous de 85 ℃ à une température ambiante de 40 ℃, supprimant la baisse de fréquence de puissance de calcul causée par les températures élevées.

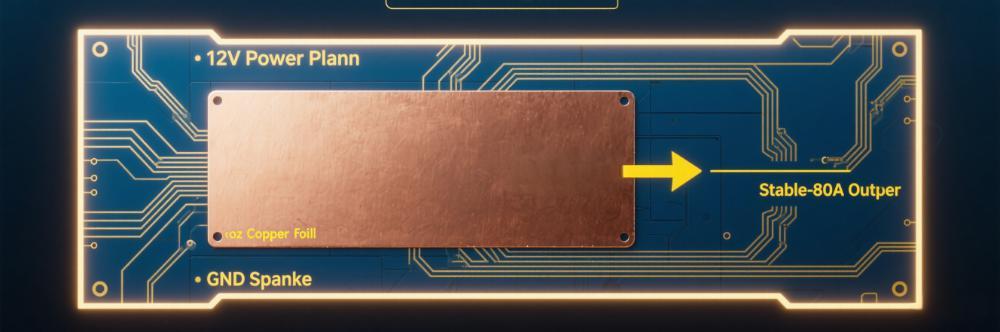

(II) Optimisation des réseaux de distribution d’énergie

Il utilise une feuille de cuivre épaisse de 2 oz et une conception de plans d’alimentation multi-groupes pour maximiser le réseau de distribution de puissance, en contrôlant l’ondulation de l’alimentation dans une plage de ±2 % et en fournissant une sortie fiable de courant élevé de 12 V/80 A. Sur une carte d’entraînement IA en PCB, la solution répond aux exigences de consommation de puissance instantanée des puces à haute puissance de calcul, améliorant de 40 % le fonctionnement fiable de la carte d’entraînement sous une charge élevée à long terme et augmentant le taux d’utilisation de la puissance de calcul de 85 % à 95 %.