Con l’integrazione su larga scala della comunicazione 5G e della tecnologia AI, i dispositivi elettronici si stanno evolvendo rapidamente verso la trasmissione ad alta velocità, il supporto ad elevata potenza di calcolo e l’elevata integrazione. In quanto supporto centrale dei dispositivi elettronici, il circuito stampato (PCB) determina direttamente l’efficienza operativa, la stabilità del segnale e l’affidabilità a lungo termine delle apparecchiature terminali. Esso è diventato la base hardware sottostante per supportare la distribuzione di applicazioni chiave quali stazioni base 5G, server AI e terminali intelligenti. Di fronte ai requisiti, da un lato, della trasmissione di segnali ad alta frequenza del 5G e, dall’altro, delle esigenze di potenza di calcolo ad alta densità dell’AI, la tecnologia PCB deve compiere passi avanti nei tre obiettivi fondamentali di “basse perdite, alta precisione e forte capacità di supporto” e formare un sistema di innovazione a tutto tondo in termini di materiali, processi e progettazione strutturale.

I. Trasmissione di segnali ad alta velocità e alta frequenza: colmare il “collo di bottiglia del segnale” tra IA e 5G

Le bande di frequenza a onde millimetriche per le comunicazioni 5G (26/28 GHz) e le esigenze di interconnessione ad alta velocità da 10 Gbps+ delle apparecchiature AI impongono requisiti molto elevati in termini di “basse perdite” e “alta stabilità” nella trasmissione dei segnali PCB. I PCB tradizionali, a causa dei limiti delle proprietà dei materiali e dei processi, non riescono a soddisfare le prestazioni richieste in termini di attenuazione del segnale, riflessione e diafonia nelle applicazioni ad alta frequenza, diventando così un collo di bottiglia chiave che limita le prestazioni dei dispositivi 5G e AI.

(I) "Difetti" ad alta frequenza dei PCB ordinari

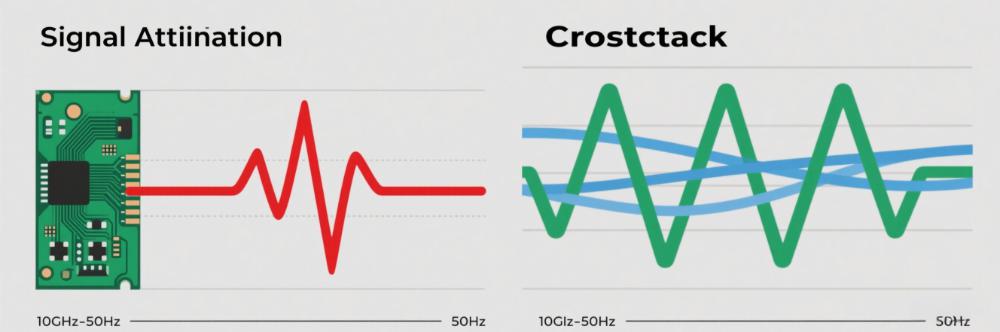

1. Maggiore attenuazione del segnale: L’“effetto pelle” dei segnali ad alta frequenza tende a concentrare la corrente sulla superficie dei conduttori (a 10 GHz la corrente si distribuisce solo entro 5 μm dalla superficie dello strato di rame), aumentando in modo significativo la resistenza equivalente. Allo stesso tempo, il fattore di perdita dielettrica (tanδ) dei substrati FR-4 standard è di circa 0,02 a 10 GHz e aumenta a 0,03 a 28 GHz, causando una perdita di energia superiore al 60% per segnali che percorrono più di 10 cm, il che non può soddisfare le esigenze di copertura a lunga distanza delle stazioni base 5G.

2. Grave interferenze di segnale: la lunghezza d’onda del segnale ad alta frequenza è estremamente corta (la lunghezza d’onda dell’onda millimetrica a 28 GHz è dell’ordine di 10 mm) e anche una piccola variazione nella lunghezza della linea può produrre sfasamenti. L’accoppiamento elettromagnetico (diafonia) tra linee adiacenti porta alla “diafonia” del segnale. Quando la velocità di trasmissione dei dati è di 10 Gbps, se la diafonia è superiore a -20 dB (accoppiamento del 10% dell’energia del segnale), ciò porterà direttamente a errori di trasmissione dei dati. I risultati dei test mostrano che la diafonia di un comune segnale a 10 Gbps può arrivare fino a -15 dB, mentre quella dei PCB orientati al 5G e all’IA deve essere mantenuta al di sotto di -25 dB.

(II) Percorsi di svolta tecnologica: “doppio aggiornamento” di processi e materiali

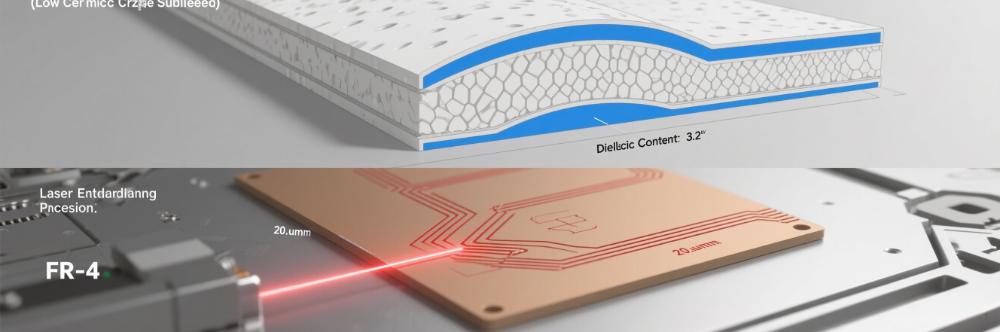

1. Selezione di materiale a bassa perdita: vengono impiegati substrati ad alta frequenza riempiti in ceramica con costante dielettrica Dk = 3,0±0,05. Per i PCB delle micro-stazioni base 5G a onde millimetriche, la perdita di trasmissione del segnale nell’intervallo di frequenza di 10 GHz è mantenuta a 0,25 dB/in, con una riduzione del 45% rispetto ai tradizionali substrati FR-4, raddoppiando praticamente la distanza di trasmissione del segnale ad alta frequenza. Allo stesso tempo, viene utilizzato il “rame foil a profilo molto basso (VLP)” per controllare la rugosità superficiale (Ra) a 0,3 μm, il che evita la “perdita per scattering” del segnale causata dal comune rame elettrolitico (Ra≈1,5 μm) e riduce la perdita di trasmissione dei segnali a 28 GHz del 15%-20%.

2. Ottimizzazione dei processi ad alta precisione: Un processo di "precisionecontrollo di impedenza+ le linee a bassa rugosità" sono fissate. Le linee di trasmissione sono lavorate con tecnologia di incisione laser con una rugosità dei bordi Ra<0,5μm. Il coefficiente di riflessione del segnale (S11) nella banda di frequenza a 28GHz è ottimizzato a -30dB, con un miglioramento del 20% rispetto al livello industriale, per consentire una trasmissione non distorta di segnali ad alta velocità da 10Gbps. Nel frattempo, la tecnologia di imaging diretto laser (LDI) viene utilizzata per ottenere un controllo della deviazione della larghezza della linea di ±0,005mm, con una precisione di adattamento dell’impedenza che raggiunge ±2%, molto superiore al livello di ±10% dei PCB tradizionali, riducendo il rischio di riflessione del segnale dal lato del processo.

(III) Effetti dell’applicazione: miglioramento delle prestazioni dei dispositivi 5G e IA

I risultati dei test di un produttore di apparecchiature per stazioni base 5G dimostrano che il modulo RF ottimizzato per le alte frequenze, con una copertura del segnale più ampia e una migliore stabilità della velocità, consente di ottenere una copertura del segnale più estesa del 15% e una stabilità della velocità superiore del 30% quando più utenti accedono simultaneamente. Sui collegamenti di interconnessione ad alta velocità dei server AI, il tasso di errore di bit della trasmissione del segnale a 10 Gbps è ridotto da 1e-12 (con PCB comuni) a 1e-15, soddisfacendo i requisiti dell’elaborazione dati AI in tempo reale a bassa latenza.

II. Progettazione ad alta densità di integrazione: la "rivoluzione spaziale" che abilita la capacità di calcolo dell'IA

Il continuo miglioramento della densità di potenza di calcolo dei chip AI (con la potenza di calcolo di un singolo chip che supera decine di TOPS) ha spinto le PCB a svilupparsi verso “alta densità e dimensioni ridotte”. Le PCB standard sono limitate dalla densità di cablaggio e dall’integrazione dei chip e non possono implementare il funzionamento parallelo su molti chip ad alta potenza di calcolo. I progressi nei colli di bottiglia dell’integrazione richiedono svolte nella progettazione strutturale.

(I) Innovazioni tecnologiche fondamentali

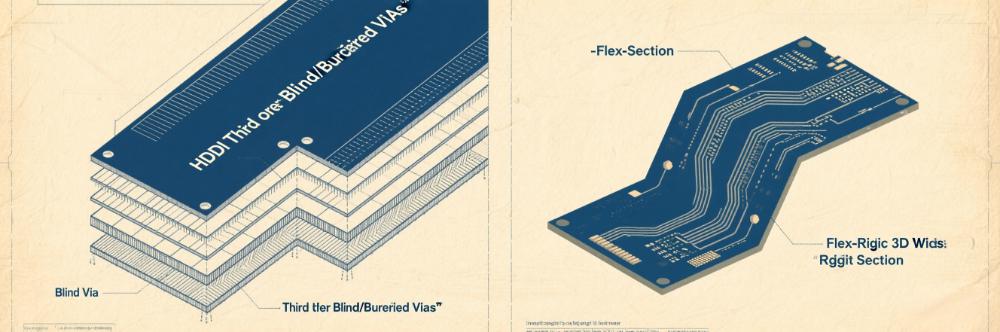

1. Tecnologia HDI con vias ciechi e sepolti di terzo ordine: Attraverso una tecnologia di lavorazione di microvia da 0,1 mm, la densità di cablaggio in un PCB viene aumentata a 200 linee/cm², il 50% in più rispetto ai PCB standard. In un PCB per una scheda di accelerazione AI, questa tecnologia supporta senza difficoltà fino a 8 chip ad alta potenza di calcolo, aumentando la densità di potenza di calcolo a 20 TOPS/cm² e fornendo un supporto di potenza di calcolo ad alta densità per i compiti di inferenza AI.

2. Combinazione flessibile-rigida + cablaggio 3D: viene adottata una struttura di cablaggio 3D che collega le schede madri rigide tramite componenti flessibili, riducendo i connettori del 60%, il percorso di trasmissione del segnale del 30% e mantenendo il ritardo del segnale entro 50 ns. Per i PCB dei terminali intelligenti, questa struttura non solo soddisfa la richiesta di dispositivi sottili e leggeri, ma garantisce anche la velocità di risposta per l’interazione AI in tempo reale.

Nelle applicazioni server per l’edge computing, la tecnologia di integrazione ad alta densità assegna il 40% dell’area del PCB e supporta l’elaborazione dati parallela a 16 canali, soddisfacendo la duplice esigenza di “dimensioni ridotte e potente capacità di calcolo” per l’inferenza AI in tempo reale e fornendo una piattaforma hardware per la distribuzione dell’AI in scenari edge.

III. Ottimizzazione del supporto di potenza di calcolo: infrangere il “dilemma della dissipazione del calore e dell’alimentazione elettrica” delle apparecchiature AI

Le profonde caratteristiche di consumo energetico delle apparecchiature AI (consumo energetico del singolo chip fino a 300 W) impongono enormi sfide alle prestazioni di dissipazione del calore e alla stabilità dell’alimentazione delle PCB. In caso di dissipazione del calore ritardata, la temperatura di giunzione del chip aumenterà, portando al calo della potenza di calcolo; un ripple eccessivo dell’alimentazione non può soddisfare le esigenze di consumo energetico istantaneo dei chip ad alta potenza di calcolo. È necessario ottimizzare simultaneamente la struttura e il design del circuito per superare tali vincoli.

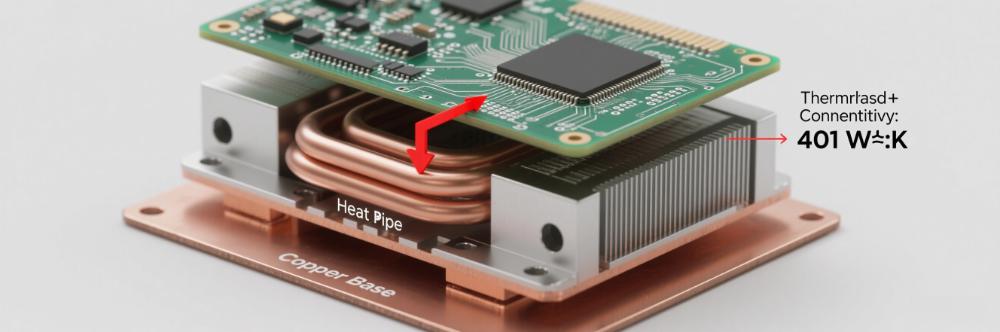

(I) Innovazione delle soluzioni di dissipazione del calore

È stata realizzata una struttura composita di dissipazione del calore con “base in rame + heat pipe integrate”, con la conducibilità termica del PCB aumentata a 5 W/(m·K), un incremento del 60% rispetto ai tradizionali substrati in alluminio. In un PCB per server AI, questa struttura può mantenere la temperatura di giunzione del chip al di sotto di 85℃ a una temperatura ambiente di 40℃, riducendo il calo di frequenza della potenza di calcolo causato dalle alte temperature.

(II) Ottimizzazione delle reti di distribuzione dell'energia elettrica

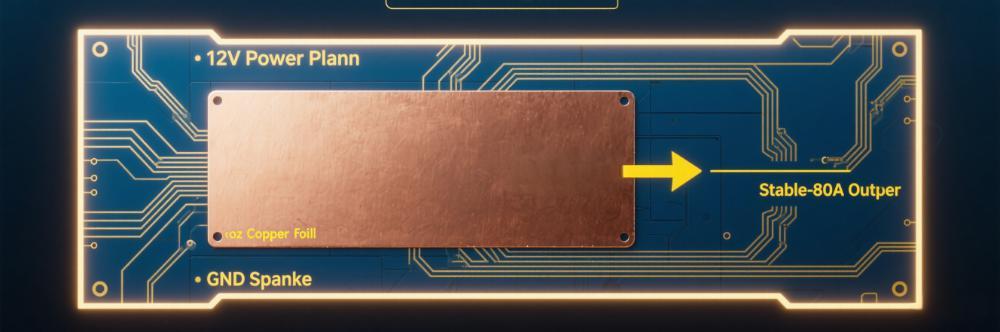

Utilizza un foglio di rame spesso 2 oz e un design del piano di alimentazione multi-gruppo per massimizzare la rete di distribuzione dell’alimentazione, controllando l’ondulazione dell’alimentazione entro ±2% e fornendo un’uscita affidabile ad alta corrente di 12V/80A. In una scheda di addestramento AI su PCB, la soluzione soddisfa le esigenze di consumo di potenza istantaneo dei chip ad alta potenza di calcolo, migliorando del 40% il funzionamento affidabile della scheda di addestramento sotto carico elevato a lungo termine e aumentando il tasso di utilizzo della potenza di calcolo dall’85% al 95%.