電子技術の継続的な進歩に伴い、デジタルシステムにおけるクロックの高周波化や立ち上がり時間の短縮が進む中で、PCBシステムは高性能なシステム構造となり、単に部品を支持するプラットフォームにとどまらなくなっている。電気的性能の観点から見ると、高速信号間のインターコネクションはもはや円滑でも透明でもなく、リード間のインターコネクションが及ぼす影響が高速PCBそして、ボードおよびプレーンの特性はもはや無視できません。高速信号インターコネクションによって引き起こされる反射、クロストーク、遅延、リンギングおよびインピーダンスマッチングなどのシグナルインテグリティの問題に適切に対処し、信号伝送の品質を確保できるかどうかが、設計の成否を左右します。

PCB信号インテグリティの基礎理論

・高速回路およびその判定原理

高速回路の定義には主に2つのバージョンがあります。

一方では、回路において、伝送線路上のデジタル信号の遅延が立ち上がり時間の20%を超える場合、その回路は高速回路と見なすことができます。

もう一方では、回路において、デジタルアナログ回路の周波数が45MHzから50MHzに達するかそれ以上になると、その回路は高速回路と見なされます。

基本的には、もしLリードの長さが~より長いTr回路は高速回路と見なされます。Lより小さいTrこの回路は低速回路と見なされる。ここで、Trパルスの立ち上がり時間を指します。

・信号伝送速度およびパルス立ち上がり時間

空気中における信号の伝送速度は 3 × 108m/s;PCB の材料である FR4 の誘電率は ε として表されるrつまり 4 です。PCB における信号伝送速度は、次の式を用いて計算できます 。

。

Vp15cm/ns に等しく、これはおよそ 6inch/ns です。パルス立ち上がり時間Tr=1/(10 xfクリック) かつ、100MHz 信号の立ち上がり時間は 1ns である。PCB 配線上の信号遅延が立ち上がり時間の 20% を超えると、信号に明らかなリンギングが発生する。立ち上がり時間が 1ns(100MHz)の方形波の場合、PCB の配線長が 0.2ns × 6 = 1.2inch を超えると、信号に深刻なリンギングが発生する。したがって、臨界長は 1.2inch(約 3cm)である。

・特性インピーダンス

特性インピーダンスは、反射、リンギング、オーバーシュートおよびアンダーシュートに影響を与えるインピーダンス整合において重要なパラメータであり、高速信号伝送の完全性に直接関係するため、高速設計において非常に重要である。

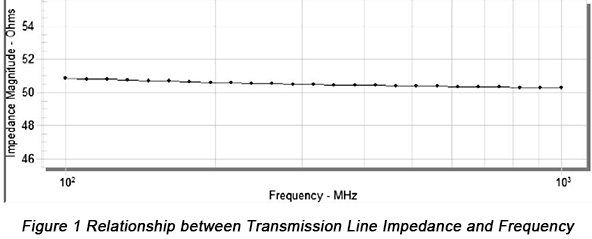

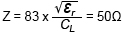

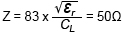

信号は伝送線路に沿って伝搬し、その電圧と電流の比は過渡インピーダンスと見なされる。伝送線路上の過渡インピーダンスは、式 によって計算される。 この式では、Cl単位が pF/inch(通常は 3.3 pF/inch)で表される、単位長さあたりの容量を指します。伝送線路に沿った過渡インピーダンスが一定値である場合、その値は伝送線路の特性インピーダンスと見なされます。PCB 上のマイクロストリップラインおよびストリップラインについては、その特性インピーダンスは、図1に示す伝送線路設計ツール Polar Si9000 を用いて算出することができます。

この式では、Cl単位が pF/inch(通常は 3.3 pF/inch)で表される、単位長さあたりの容量を指します。伝送線路に沿った過渡インピーダンスが一定値である場合、その値は伝送線路の特性インピーダンスと見なされます。PCB 上のマイクロストリップラインおよびストリップラインについては、その特性インピーダンスは、図1に示す伝送線路設計ツール Polar Si9000 を用いて算出することができます。

信号インテグリティに影響を与える要因とその対策

・インピーダンス整合

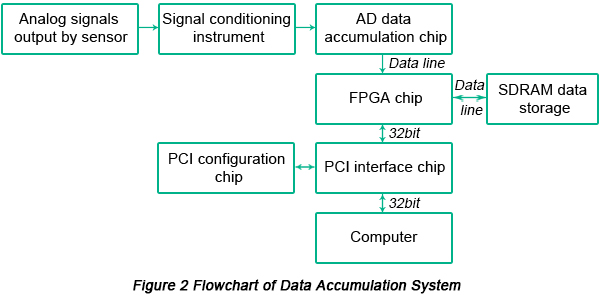

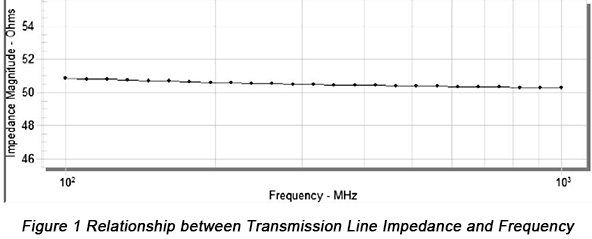

インピーダンスマッチングは、高速回路設計において、データを高速かつ正確に伝送するために必要である。データ収集システムは、一般にセンサ、信号調整装置、ADデータ収集チップ、FPGA、およびSDRAMで構成され、図2に示すようになっている。

AD9649 は、1.8V 電源で動作し、14 ビットデータラインによる並列サンプリングを行う AD チップとして適用される。サンプリング周波数は 20M に設定されている。PCI9054 は PCI インターフェースチップとして採用され、DMA データ転送をサポートする。93LC66B は PCI 設定用チップとして採用される。HY57V561620FTP-H はデータストレージとして用いられ、4 つの BANK から構成され、それぞれが 4M x 16bit のメモリ空間、13 本の行アドレス線および 9 本の列アドレス線を有する。EP1C6F256C8 は FPGA として選定され、端子電圧 3.3V、コア電圧 1.5V で動作する。PCI バスの幅は 32 ビットで、33MHz のクロックが読み書きクロックとして用いられ、読み書きの最大速度は毎秒 132MByte に達し、蓄積データの高速伝送をサポートできる。

PCB を設計する過程では、次の要素を考慮する必要があります。

a.デジタルとアナログの混在部分として、AD は PCB 設計における重要なポイントの一つである。デジタル部の周波数が高いため、アナログ部は干渉に非常に敏感である。適切な処理が行われない場合、デジタル信号はアナログ信号に干渉しやすくなり、その結果 EMI 問題が発生する。設計者が従うべき正しい原則は次のとおりである。第一に、混在信号を扱う PCB 上ではデジタルグラウンドとアナロググラウンドを分離すること。第二に、アナログおよびデジタル電子部品を分類し、アナログ領域にはアナロググラウンドを、デジタル領域にはデジタルグラウンドをそれぞれ配置すること。第三に、領域分割部付近でアナロググラウンドとデジタルグラウンドをビーズコアで接続することである。これらの対策により、デジタルグラウンドとアナロググラウンドの分離を実現することができる。

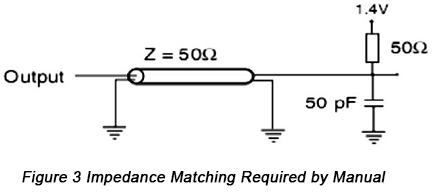

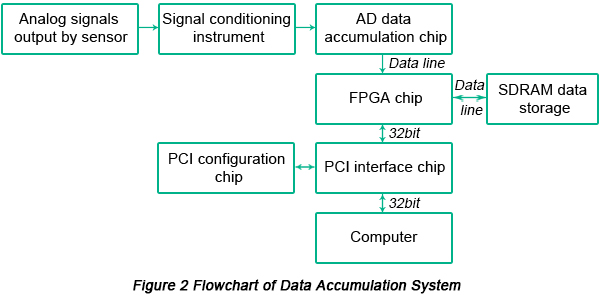

b.SDRAM はデータ蓄積システムに適用されており、マニュアルには、FPGA に接続されるデータラインは高速伝送を確保するために 50Ω のインピーダンスマッチングで構成しなければならないことが明記されている。これは図3に示されている。

FPGA が蓄積されたデータを SDRAM に書き込んだ後、データを保持するためにリフレッシュを継続的に実行する必要があり、各行のリフレッシュ周期は 64 ミリ秒より短くなければなりません。

Polar Si9000ソフトウェアによるインピーダンスマッチングの手順は、次のように示されます。

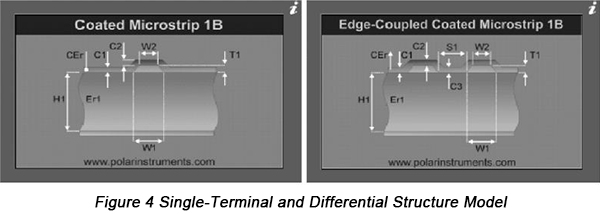

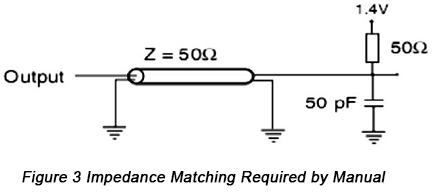

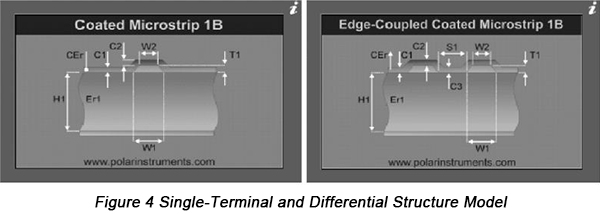

a.高速信号ラインは、可能な限りビアを避けてPCBの表面層を横切るようにする必要があります。ソフトウェアでは、図4に示すようにマイクロストリップライン構造モデルが選択されています。

50Ωのインピーダンスマッチングは一般的にシングルエンド配線で行われ、90Ωのインピーダンスマッチングは一般的に差動配線(USB2.0 の D+、D- など)で行われます。

b.必要なインピーダンス整合値および具体的な値PCB製造ソフトウェアインターフェース上には、誘電体厚さ、PCB材料の誘電率、銅箔厚さ、ソルダーレジスト(グリーンオイル)厚さ、およびソルダーレジストの誘電率などのパラメータが入力される技術が用いられる。

|

アイテム

|

説明

|

参照値および計算値

|

| H1 |

誘電体の厚さ(PP または基板材料) |

3.5~8.5ミル |

| Er1 |

基板材料の誘電率 |

4-4.6 |

| W1 |

信号ルーティング幅 |

インピーダンス値に基づいて |

| C1 |

基板材料のグリーンIOLの厚さ |

0.8ミル |

| C2 |

銅上のグリーンオイルの厚さ |

0.5ミル |

| CEr |

グリーンオイルの誘電率 |

3.3 |

| ゾ |

整合すべきインピーダンス値 |

単一端子:50Ω

差動:90Ω |

製造技術の具体的なパラメータは、~とのコミュニケーションを通じて把握することができるPCBメーカーこれによりリードの幅を算出できるようになります。差動マイクロストリップラインの場合は、リード間の距離(S1)も算出する必要があります。

c.リードの算出された幅が比較的大きく、PCB配線が完了できない場合は、設計要件を満たしたうえで、製造技術のパラメータを調整するために、PCBメーカーとより多くのコミュニケーションを行う必要があります。

・クロストーク

クロストークとは、伝送線路上で信号が伝送される際に、電磁結合の結果として隣接する伝送線路上に予期しない電圧ノイズ干渉が生じる現象を指す。クロストークが過度になると、回路が誤動作を起こし、システムが正常に動作しなくなる可能性がある。クロストークは電磁結合によって発生し、この結合は容量性結合と誘導性結合に分類される。前者は、干渉源における電圧変化の結果として生じる誘導電流によって引き起こされる電磁干渉であり、後者は、干渉源における電流変化の結果として生じる誘導電圧によって引き起こされる電磁干渉である。干渉源の状態が変化すると、被干渉対象には一連の干渉パルスが発生し、これは高速システムにおいて非常に一般的である。

クロストークへの対策は次のように示されます。

a.隣接する層間の配線方向には直交性を維持する必要があります。クロストークを低減するため、異なる信号線を持つ隣接層では同一方向の配線を避けるべきです。特に信号速度が比較的高い場合には、配線層を分離するためにグラウンド層を設け、信号線同士はグラウンド信号線によって分離することを検討する必要があります。

b.配線間のクロストークを低減するためには、配線間の間隔を十分に大きく取る必要があります。配線中心間の距離が配線幅の3倍以上であれば、電界の70%を相互干渉から抑制することができ、これを「3Wルール」と呼びます。

c.高速信号ラインが要件を満たしている場合、反射を低減または除去し、クロストークを減少させるために、終端にマッチングを施すことができる。

シグナルインテグリティ設計手法の適用

PCB設計の過程では、信号完全性理論に基づいて多くの設計ルールがまとめられてきた。これらを参考にしてPCB設計ルール、信号インテグリティをより良く確保することができる。PCB設計の過程では、次のような設計情報を詳細に把握しておく必要がある。

a.コンポーネントのレイアウト位置、特に大電力および放熱が大きいコンポーネントやチップ部品に関して特別な要件があるかどうか。

b.信号の分類、速度レート、伝送方向およびインピーダンス整合要件。

c.信号の駆動能力、主要信号および保護対策。

d.電源の種類、グラウンド、電源およびグラウンドのノイズ制限要件、電源プレーンとグラウンドプレーンの設定および分割。

e.クロックラインの種類と速度レート、クロックラインのソース、方向、クロックの遅延要件および最大配線要件。

エレクトロニクスの革新には、高速動作時の信号完全性を維持し、反射やクロストークといった問題を解決するための高度なPCB設計が求められます。正確な配線、部品配置、および適切なインピーダンスマッチングは、完璧な性能を確保するうえで極めて重要です。

PCBCart は、信号完全性の向上と真の設計精度を最優先した高性能 PCB ソリューションによって際立っています。最先端の材料およびプロセスに関する知識により、将来のアプリケーション向けの最高水準の PCB を保証します。PCBCart と提携して、電子機器プロジェクトを新たな高みへと引き上げましょう。今すぐお見積もりをご依頼いただき、当社のカスタムソリューションによるクラス最高の性能をご体験ください。

デザインを強化:今すぐ高速PCBのお見積もりを取得しましょう

役立つリソース:

•PCB高速信号回路設計における3つの配線手法

•高速PCBレイアウトにおける信号反射の抑制方法

•高速デジタル・アナログ混在回路におけるシグナルインテグリティ解析とPCB設計

•PCB設計におけるビアのインピーダンス制御とその信号品質への影響

•PCBCart のフル機能 PCB 製造サービス - 多彩な付加価値オプション

•PCBCart の高度な PCB アセンブリサービス - 1 個から対応

。

。 この式では、

この式では、