超大規模集積回路(SLSI)においてチップの集積度がますます高くなるにつれ、現代の電子システムは小型パッケージ、大規模化および高速化の方向へと発展しており、その結果、高速回路設計における配線や多層化の問題をどのように解析・処理するかといった、避けることのできない課題が生じている。現在、電子製品の高周波数は数百 MHz から数千 MHz に達しており、立ち上がりエッジおよび立ち下がりエッジも非常に急峻になっているため、この種の製品を設計する過程では、PCB レイアウトのルールや基板材料の誘電率がシステムの電気的性能にとって極めて重要となる。

現在の大半の電子製品研究において重要なプロセスおよび段階として、高速PCB設計では、タイミングの問題、ノイズ干渉、および EMI(電磁干渉)を含む主な課題が見られており、これらの解決策はシステム設計の正常な動作に関係している。

現在、従来の設計手法は製品の信頼性と成功率の低下を招いており、これにより組み込み応用システムにおける高速PCB設計の研究は、高い実用的価値と広い市場的期待を与えられている。

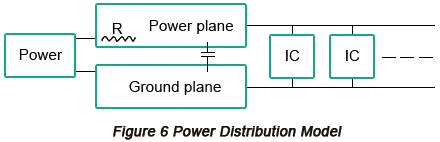

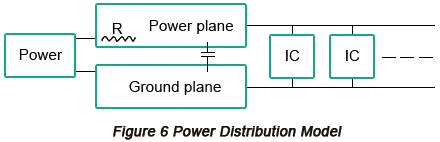

図1は、組み込み型RTU(遠隔端末装置)の機能フレームを示している。

図1から分かるように、本システムは、電力量ユニット、センサーユニットおよびアナログ量測定ユニットを含むデータ蓄積層、インターネット上のエンジニアセンターから受信したコマンドによってデータ蓄積層内のデータを調整するゲートウェイを含むデータ伝送層、そしてAPP監視ソフトウェアによって実装され、データをリアルタイムで保存・解析し、ユーザーインターフェースに向けたデータ曲線を生成するデータ処理層から構成される垂直型通信構造である。この構成により、データ蓄積の柔軟性と管理効率が向上する。

この組み込みIoT RTUシステムのハードウェアは主に、USB2.0、AT91SAM9263プロセッサ、CAN、SDRAM、NANDフラッシュ、データフラッシュ、イーサネットコントローラ、クロックチップ、RS232/485インターフェース、電源管理およびデータ蓄積部で構成されている。

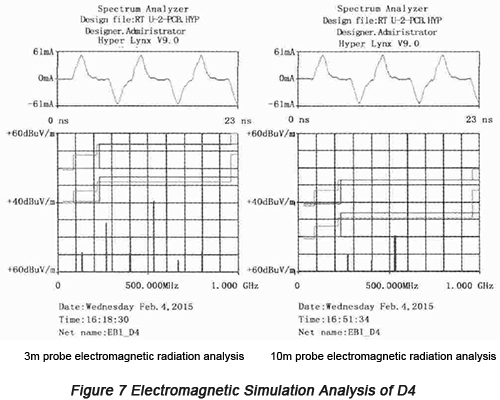

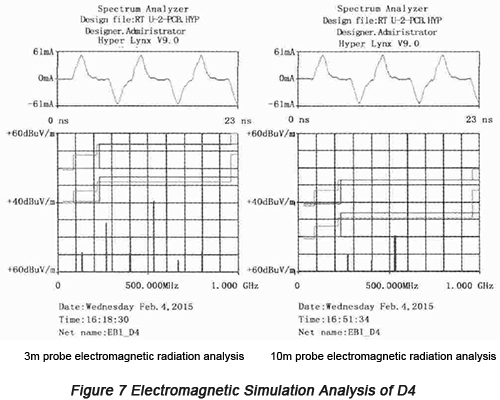

Linuxオペレーティングシステムで動作する本設計は、メモリおよびデバイス管理の能力が高く、複数のミッションに対するリアルタイムスケジューリングを実現している。その中には、ネットワーク接続、データ通信および設定の蓄積を担当する複雑なアルゴリズムと通信プロトコルが含まれている。図2は本稿で設計したRTU回路基板である。

IPv6 と IPv4 のデュアルスタックをサポートする本システムは、即時性およびリアルタイム性を実現することができます。データ保存に関しては、通信が遮断された状況下でもローカルストレージの要件を満たすことができます。通信インターフェースに関しては、RS485、RS232、CAN を含む各種フィールドデータ通信インターフェースを備え、Modbus RTU 通信プロトコルをサポートし、異なるインターフェースおよび異なる通信速度の要件を満たします。

・システムのPCBスタックアップ設計

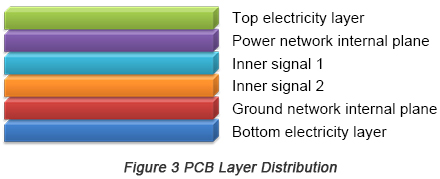

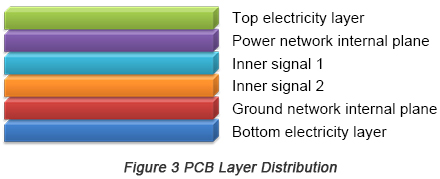

PCBの層数は、通常は設計の難易度に応じて2層から32層の範囲になります。本設計で採用した6層PCBは、部品パッケージの高密度、小さいレイアウト配線スペース、および高い信号周波数に基づいて決定されています。PCB層構成以下の図3に示されています。

このシステムでは、FLASH と SDRAM に対してストリップライン構成が採用されており、配線は Inner Signal 1 および Inner Signal 2 上に実装されています。

・本システムにおけるPCB制約ルール

高速PCB設計においては、インピーダンスの連続性とEMIは、配線の間隔・長さ・幅およびループの隣接処理によって大きく影響を受ける。部品配置と配線の品質は最終設計の成否に関係するため、PCBの制約ルールを合理的に策定しなければならない。

Hyper Lynx には、チャート解析に干渉する機能があり、IBIS モデルを適用することで、損失伝送、差動信号、および周波数とともに変化するスルーホールモデルを正確にシミュレーションすることができます。メインネットワークは、配線前に Line によってシミュレーションされ、PCB の積層構造と配線インピーダンスを改善し、高速 PCB ネットワークの配線制約ルールは、設計効率を高めるためにシミュレーション結果に基づいて事前に設計されます。

・このシステムのPCBシミュレーション

高速PCB設計の過程では、フロント端のシミュレーションには理想的な伝送線路モデルが適用され、一度にシミュレーションされる信号線の本数は限られている。しかし、PCBバック端の伝送線路は、実際にはスルーホールやプレーンの切り替えの影響を受けるPCBの配線である。このような状況下で得られるシミュレーション結果は、非常に信頼性が高い。

システムのコア回路設計の過程において、単一端子信号の終端マッチング抵抗は 40~60Ω の範囲であることが要求され、信号線間のクロストークしきい値は 165mV とする。また、DM9000 および DM9161 のネットワークコントローラを 100Mbps の通信速度に自己適応させるため、差動インピーダンスは 100±5Ω の範囲内でなければならない。PCBシミュレーションMentor Graphic が開発した Hyper Lynx シミュレーションソフトウェアによって、SDRAM、Ethernet 差動ライン、電源インテグリティおよび EMC 上で実装されている。

a. SDRAM 設計

ストリップライン設計の過程において、クロストークとスルーホールは、遅延を引き起こす主な要因である。ラインシミュレーションツールによって決定された配線ルールに従ってPCBを完成させたとしても、部品ピン数の多さやPCBサイズの制約など、いくつかの問題は避けられない。そのため、ボードシミュレーションツールを用いて複数のネットワークを適切にシミュレーションすることが必要である。

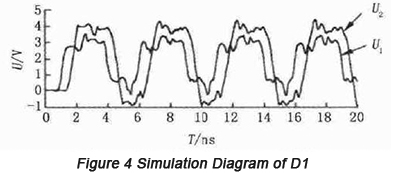

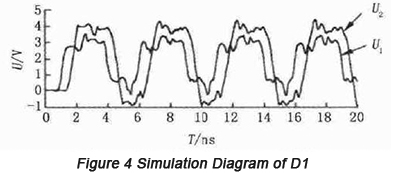

シミュレーション結果に基づくと、アナログネットワーク EBI_D0 および EBI_D2 のクロストーク強度は 165mV を超えている。2 つのネットワークは、黄色でマーキングされた領域においてスネーク配線同士の間隔が不適切であるため、EBI_D1 に影響を与え、結合箇所を形成している。配線間隔を広げることで、このような問題を解消できることが示される。しかし、実際に我々が懸念しているのは、なぜハックネットワークがこれほど強い干渉を受けるのかという点である。その原因は、おそらく不適切な抵抗値の選択によりインピーダンスがマッチングしていないことにある。現在のところ、終端抵抗の抵抗値は 43.1Ω に設定されている。220MHz で励振した条件下におけるネットワーク EBI_D1 の解析シミュレーション波形を、以下の図 4 に示す。

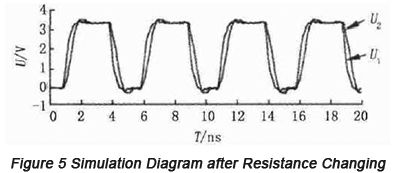

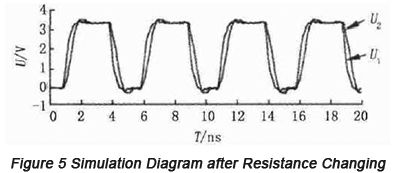

図4に基づくと、EMI_D1伝送線路上でインピーダンスの不連続が発生し、信号波形に歪みが生じている。起動不能といったシステム故障の原因にはならないものの、製品動作の安定性を保証することはほとんどできない。ボードシミュレーションに戻り、スルーホールおよび損傷シミュレーションを適用することで、EBI_D0およびEBI_D1の終端抵抗を46.9Ωに変更した。その結果、抵抗変更後のクロストークのシミュレーション図を図5に示す。

この図に基づくと、ネットワーク信号が改善され、EBI_D1 上で生じていた干渉強度が明らかに低減されたことが示される。

b. インターネット差動バス設計

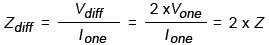

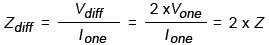

高速および3GIOインターコネクションの特性を備えたHyper Lynx開発のボードシミュレーションモジュールは、差動信号バスに基づく超高速シリアルデータパスおよびソース同期技術を適用し、高速PCB設計に対して便利かつ高効率な解決策を提供します。本システム内のDM9000およびDM9161には、それぞれ2組の高速差動信号バス、すなわちTX+、TX-およびRX+、RX-があり、差動インピーダンスは100Ωとなっています。伝送理論により、差動インピーダンスは次の式に基づいて算出できます。 。

。

この式において、Z は各信号線の伝送インピーダンスを指し、通信距離および耐ノイズ性能に重大な影響を与える。ここでは DM9000 を用いて、差動信号をネットワークの TP_E_TX+ および TP_E_TX- へ送信している。反射の影響を低減するために、スルーホールを介した信号線に 100Ω の抵抗を並列に配置している。

c. 本システムの電源インテグリティ設計

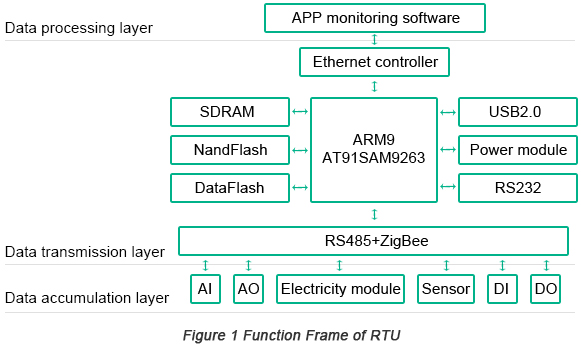

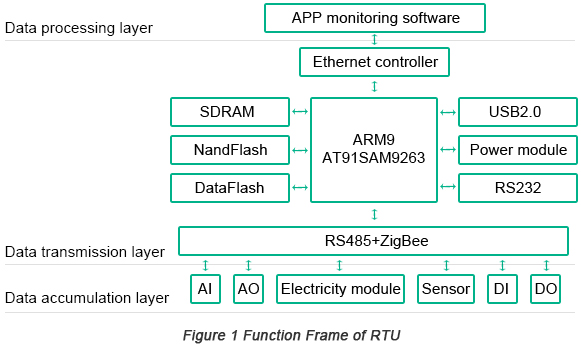

図6は基本的な電力分配モデルであり、電流は電源層を通じて各キャリアに伝送され、その後グラウンド層へと送られます。

高速PCB設計の過程では、各ユニットのエネルギー消費を回路システム内で計算し、電源ネットワークの幅を正しく配分し、適切に増幅する必要があります。

6層の電源インテグリティは次のように要約できる。最大電圧降下は2.1mVで、約0.06%に近い。最大電流密度は16.3mA/m²である。ある適切な範囲内では、電流密度が50mA/m²を超えると、PCBの温度が上昇し、動作過程においてメインチップおよび信号ラインに影響を及ぼす。銅箔幅を増やすことで電流密度を低減でき、信号配線の厚みを増すことはPCB温度の低下に有効である。

d. システムの電磁両立性解析

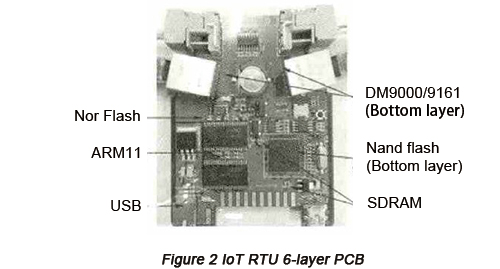

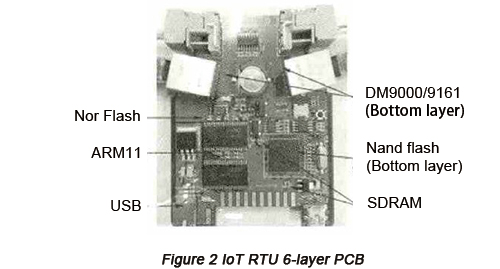

電磁干渉は通常、結合の形態によって有用な信号を伴うキャリアとして伝送される。本設計では、予備設計後のPCBの放射強度を解析するために、Hyper Lynxシミュレーションソフトウェアを適用した。重要な信号線D4は、ARM9とSDRAMの間で取り出され、プローブ位置はそれぞれ3mと10mに設定した。励振源が220MHzの場合、FCCおよびCISPRの国際規格に基づくシミュレーションデータが得られ、その結果を以下の図7に示す。

シミュレーション結果に基づくと、PCB との距離が短いことにより、回路基板からの放射が大きくなり、その放射は信号周波数の変化に伴って変動する。高速回路設計の過程では、ノイズ放射を低減しなければならない一方で、PCB の耐干渉性を最適化することができる。

。

。