高速電子システムに関して言えば、プリント基板設計の成否は、理論面と実践面の両方において電磁両立性(EMC)システムにおける高度な問題解決に直結する。EMC規格を満たすためには、高速PCB設計大きな課題に直面しているため、高速PCB設計者は設計プロセスにおいて従来の設計思想と手法を捨て去らなければならない。本稿では、実務の観点から、高速PCB設計プロセスにおける誤解と対策について主に分析する。

PCB がショッピングカートに正常に追加されました

高速電子システムに関して言えば、プリント基板設計の成否は、理論面と実践面の両方において電磁両立性(EMC)システムにおける高度な問題解決に直結する。EMC規格を満たすためには、高速PCB設計大きな課題に直面しているため、高速PCB設計者は設計プロセスにおいて従来の設計思想と手法を捨て去らなければならない。本稿では、実務の観点から、高速PCB設計プロセスにおける誤解と対策について主に分析する。

これまでのところ、高速PCB設計に関しては主に3つの設計手法があります。すなわち、ノイズおよび遅延PCBパターン設計手法、インピーダンスおよび伝搬遅延時間制御手法、そしてPCBインピーダンスをパラメータとした評価手法であり、このうち後者2種類の手法が中核となっています。PCB製造また、高速PCB製造伝送には多くの技術があり、一般的に使用される基本構造はマイクロストリップとストリップラインである。高速PCB伝送線路に関しては、Z0それがインピーダンスパラメータであり、tpdつまり、伝搬遅延時間が最も重要な変数である。実際には、マイクロストリップの構造がストリップラインの構造と異なれば、計算式も異なる。しかし、いずれの場合でも、インピーダンスは常に伝送線路の幾何学的構造によって決まる。多くの場合、PCB材料の一部の誘電率は、周波数、面積の吸水率、温度、および電気的特性の影響を受ける。2層または多層PCBでは、その誘電率はPCB材料中の樹脂とシリカの割合によって影響を受ける。

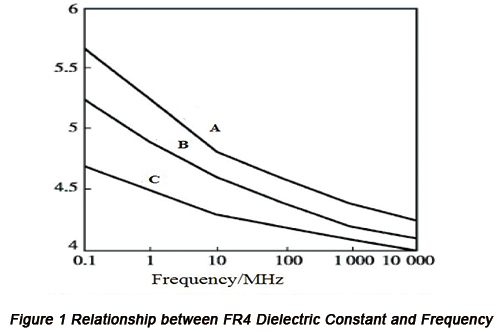

現在では、最も一般的に使用されているPCB材料FR4 です。通常、PCB 材料サプライヤーは、プロジェクト技術者がその材料を使用する際の基準となる比誘電率の値を示しています。実際の応用では、その値のパラメータは通常 1MHz の条件下で得られますが、高速な状況になると、図1に示すように比誘電率には明らかな変化が生じます。

図1の3本の曲線は、シリコンと樹脂の異なる配合比率を示している。3本の曲線のうち、曲線Aが最も高く、Bが中間、Cが最も低い。もし作業者がこの違いに気づかないと、インピーダンスおよび伝搬遅延時間に関して、計算やシミュレーション結果と実際の状況との間に大きなずれが生じる可能性があり、高速システムのシグナルインテグリティ設計に影響を及ぼすことになる。

ほとんどの資料では、PCB 配線において 90° コーナーは避けるべきだとされています。これはインピーダンスの不連続を引き起こす可能性があり、電磁干渉(EMI) 放射。理論の観点から見ると、90°コーナーでは線幅の変化が比較的大きく、その結果としてインピーダンスが大きくなり、深刻なインピーダンス不連続が生じる。実務の観点から見ると、電磁エネルギーは配線のコーナー部に集中しやすく、コーナーが鋭く尖っているほど、より多くのエネルギーが集中する。以上の分析に基づき、EMI 放射は 90° コーナーで最も顕著になる。

しかし、一部の研究者は、90°コーナーがインピーダンスに与える影響は10%以内であると指摘しています。配線幅が6milの場合、それがキーとなる長さになると、周波数はテラヘルツ帯域になります。したがって、実際の状況では、90°コーナーがインピーダンスの不連続を確実に引き起こすと推定できます。

したがって、実際の場面ではPCB配線少なくとも GHz 帯域内では、コストをかけてまで 90° コーナーを避ける必要はありません。

KNG による 20-H 原則の登場以来、それは高速 PCB 設計における主要な原則として受け入れられてきました。中には、この原則によって、対象となる PCB 層周辺の電磁密度をおよそ 70% 低減できると指摘する研究者もいます。さらに、外部への EMI 放射を低減するうえでも有効な役割を果たすとされています。しかし、多くの実験結果は、研究者たちの期待を裏付けてはいません。

いくつかの実験では、2層PCBに対しては20-Hルールがより深刻な放射を引き起こす一方で、多層PCBにおいては内部の中間層に20-Hルールを適用しても明確な改善はもたらされないことが示されている。

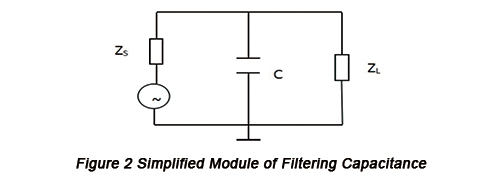

フィルタリング用コンデンサは、電子システムにおけるEMC問題を解決するために用いられる、実証済みで効果的かつ経済的な手段である。しかし、高速電子システムの登場により、フィルタリング用コンデンサの性能および適用設計に対して新たな要求が生じている。フィルタリング用コンデンサの簡略化モジュールを図2に示す。

次の要件を満たしていなければなりません:ZC< ZS// ZL(ZC=1/2πfC)。よくある誤解として、Z が… とさえ考えられていますCZ より小さいL、フィルタ用容量の目的を達成することができる。実際には、フィルタ用容量のパラメータは、Z の値がわからない限り決定することができない。Sと ZL決定されます。

しかし、高速回路では、Z も…Sノル ZLは純粋な抵抗であり、複素数値を必要とする。一方、ZC高速回路においては、純粋な静電容量というものは存在せず、等価直列抵抗(ESR)と等価直列インダクタンス(ESL)の両方を考慮しなければならない。これらすべてが、高速電子システムにおけるフィルタ用コンデンサの応用上の難点となる。もし設計者がこれらの側面を無視すると、計算やシミュレーション結果と実際との間に明らかな差異が生じる。

PCB設計者は、PCBレイアウトやPCB上の部品間の相互接続に最も注意を払う傾向があり、その重要性を無視しがちであるコンポーネント包装実際のところ、これは高速PCB設計に深刻な結果をもたらす可能性があります。シリコンパッケージは、接続ラインやリードを通して生じる寄生インダクタンス、寄生抵抗、寄生容量を介して、シリコンの性能に影響を与えます。これらのパラメータは、ノイズ、伝送遅延、エッジレート、および周波数応答を引き起こします。パッケージが異なれば、その寄生パラメータは大きく異なる可能性があります。同一の回路を持ちながらパッケージが異なるシリコンでは、その性能に異なる特徴が現れます。

実際、高速電子システムにおいては、シリコン設計、パッケージ設計、およびボードレベル設計は決して互いに独立したものではありません。シリコン側の設計フローにおいては、PCB に応じて適切なパッケージを選定する必要があります。シリコン設計の全体レイアウトは、技術的要因とボードレベル要因の両方から影響を受けます。シリコンパッケージに関しては、その PCB とのマッチングが必ず考慮すべき要素となります。さらに重要なことに、適切なパッケージはボードレベルのインテグリティおよび EMC/EMI の問題に対して大いに役立ちます。したがって、シリコンパッケージングは決して無視されたり軽視されたりすべきではありません。

PCB の信号伝送リードには、有用な信号を伝送する差動モード電流と、有用な情報を持たないコモンモード電流が存在し、どちらも EMI 放射を発生させる。

その比較的高い電流値のため、差動モード電流は回路設計者によって重視され、差動モード電流によるEMI放射を制御するための理論や手法が形成されてきた。その結果、一部のEDAツールには、差動モード電流によるEMI放射のシミュレーションおよび予測機能が備わっている。しかし、差動モード電流と比べて、コモンモード電流ははるかに小さいため、設計者がコモンモード電流によるEMI放射を軽視してしまいやすい。

しかしながら、最近の研究によれば、コモンモード電流はディファレンシャルモード電流よりはるかに小さいにもかかわらず、前者によって生成されるEMI放射干渉は後者によるものよりもはるかに大きいことが分かっている。現在に至るまで、コモンモード電流によるEMI放射は、高速・高性能回路基板における主要な放射干渉源の一つとなっている。さらに悪いことに、コモンモード電流EMI放射の発生要因は複雑であり、シミュレーションも予測も実現できていない。加えて、コモンモード電流EMI放射の制御に関する研究は、いまだ進行中である。

したがって、高速PCBを設計する際に、差動モード電流によるEMI放射のみに基づいてEMI放射をシミュレーションおよび予測することは信頼できません。

次の記事高速レイアウトのコツ

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

[email protected] [email protected]

[email protected] [email protected]

ご支援ありがとうございます!お寄せいただいたご意見は、サービス最適化のために詳細に検討させていただきます。お客様のご提案が最も価値のあるものとして採用された場合、100ドル分のクーポンを添えて、すぐにメールでご連絡いたします。