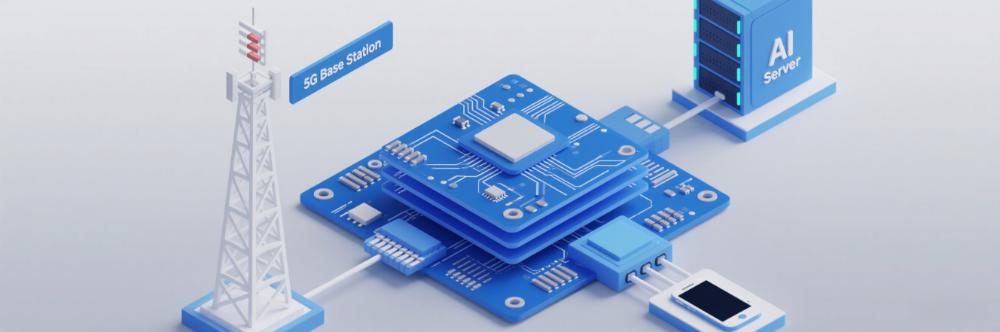

5G通信とAI技術の大規模な統合に伴い、電子機器は高速伝送、高い演算能力のサポート、高集積化へと急速に進化している。電子機器の中核キャリアであるプリント配線板(PCB)は、端末装置の動作効率、信号の安定性、および長期信頼性を直接左右し、5G基地局、AIサーバー、スマート端末などの重要アプリケーションの展開を支える基盤ハードウェアとなっている。5Gの高周波信号伝送要件とAIの高密度演算需要という両面に直面し、PCB技術は「低損失・高精度・高支持力」という三つの基本目標においてブレークスルーを図り、材料・プロセス・構造設計の全方位的なイノベーションシステムを構築する必要がある。

I. 高速・高周波信号の伝送:AI と 5G の「信号ボトルネック」をつなぐ

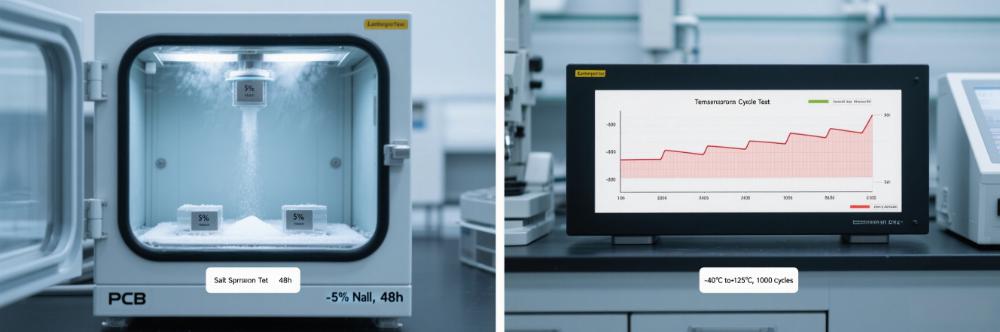

5G通信のミリ波帯域(26/28GHz)およびAI機器における10Gbps以上の高速インターコネクトのニーズは、PCB信号伝送の「低損失」と「高安定性」に対して非常に高い要求を課しています。一般的なPCBは、材料特性および製造プロセス上の制約により、高周波用途における信号減衰、反射、クロストーク性能を満たすことができず、その結果、5GおよびAI機器の性能を制約する重要なボトルネックとなっています。

(I) 一般的なPCBにおける高周波の「短所」

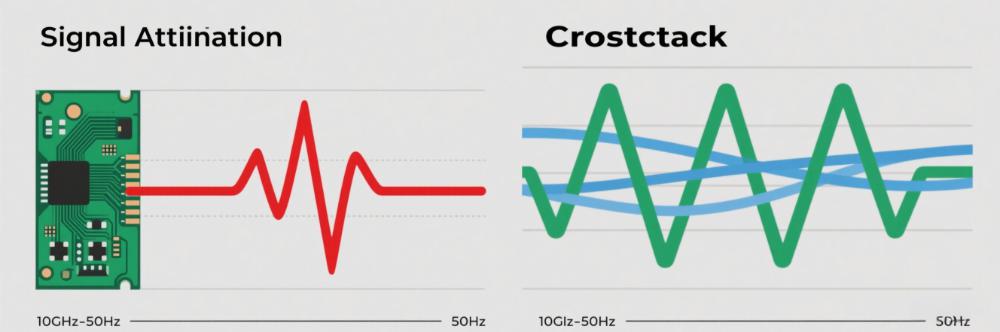

1. 信号減衰の増大:高周波信号の「表皮効果」により電流は導体表面に集中する傾向があり(10GHzでは銅層表面から約5μmの範囲にしか電流が広がらない)、等価抵抗が大幅に増加します。同時に、一般的なFR-4基板の誘電正接(tanδ)は10GHzで約0.02、28GHzでは0.03に達し、10cmを超えて伝送される信号では60%以上のエネルギー損失が発生します。そのため、5G基地局が求める長距離カバレッジ要求を満たすことができません。

2. 深刻な信号干渉:高周波信号の波長は極めて短く(28GHz ミリ波の波長は 10mm オーダー)、わずかな配線長の差でも位相ずれを引き起こします。隣接配線間の電磁結合(クロストーク)によって信号の「クロストーク」が発生します。データ伝送速度が 10Gbps の場合、クロストークが -20dB を超える(信号エネルギーの 10% が結合する)と、データ伝送エラーを直接引き起こします。テスト結果によると、一般的な 10Gbps 信号のクロストークは最大で -15dB に達する一方、5G および AI 向け PCB では -25dB 未満に抑える必要があります。

(II)技術的ブレイクスルーの道筋:プロセスと材料の「二重アップグレード」

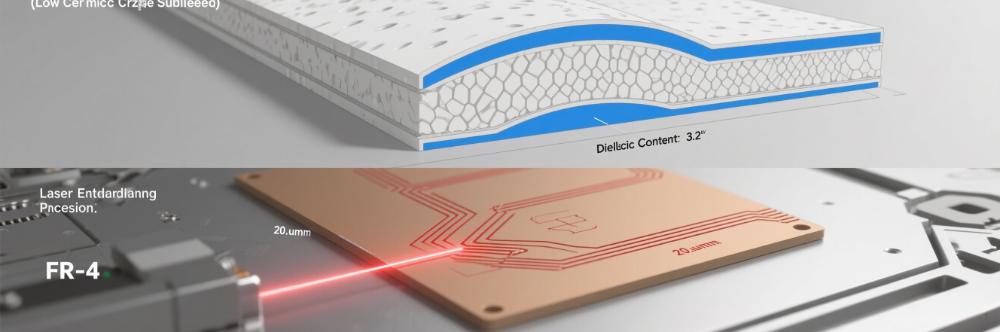

1. 低損失材料の選定:比誘電率 Dk = 3.0±0.05 の高周波セラミック充填基板を採用しています。5G ミリ波マイクロ基地局用 PCB においては、10GHz 帯域での信号伝送損失を 0.25dB/in に抑え、従来の FR-4 基板と比較して 45% 低減し、高周波信号の伝送距離を実質的に 2 倍にしています。同時に、「超低プロファイル(VLP)銅箔」を用いて表面粗さ(Ra)を 0.3μm に制御することで、一般的な電解銅箔(Ra≈1.5μm)による信号の「散乱損失」を回避し、28GHz 信号の伝送損失を 15%~20% 低減しています。

2. 高精度プロセスの最適化:「精密」の一つのプロセスインピーダンス制御+ 低粗さライン」が固定されています。伝送ラインはエッジ粗さ Ra<0.5μm のレーザーエッチング技術で加工されています。28GHz 帯域における信号の反射係数(S11)は -30dB に最適化されており、これは業界水準より 20% 優れており、高速 10Gbps 信号の歪みのない伝送を可能にします。同時に、レーザーダイレクトイメージング(LDI)技術を用いることで、ライン幅のばらつきを ±0.005mm に制御し、インピーダンス整合精度は ±2% に達しており、一般的な PCB の ±10% レベルをはるかに上回ることで、プロセス面からの信号反射リスクを低減しています。

(III) 応用効果:5GおよびAIデバイスの性能向上

ある5G基地局装置メーカーの試験結果によると、高周波数帯に最適化されたRFモジュールにより、信号カバレッジの拡大とレート安定性の向上が実現され、複数ユーザーが同時アクセスした場合でも、信号カバレッジが15%拡大し、レート安定性が30%向上することが示された。AIサーバーの高速インターコネクトリンクにおいては、10Gbps信号伝送のビット誤り率が(一般的なPCB使用時の)1e-12から1e-15へと低減され、低遅延AIリアルタイムデータ処理の要件を満たしている。

II. 高密度統合設計:AI計算能力を可能にする「宇宙革命」

AIチップの計算性能密度が継続的に向上し(単一チップの計算性能が数十TOPSを超えるレベルで動作することにより)、PCBは「高密度・小型化」へと発展している。標準的なPCBは配線密度やチップ集積度に制約があり、多数の高計算性能チップによる並列動作を実現できない。集積のボトルネックを打破するには、構造設計におけるブレークスルーが必要である。

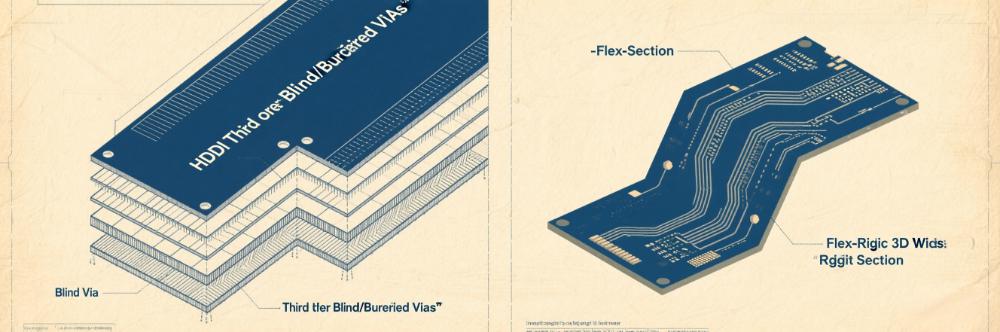

(I)中核となる技術革新

1. HDI 第3オーダー・ブラインド/ベリッドビア技術:0.1mmマイクロビア加工技術により、PCB の配線密度は標準的な PCB より 50%高い 200 本/cm² に向上します。AI アクセラレータカード用 PCB では、この技術により最大 8 個の高演算性能チップを無理なく搭載でき、演算密度を 20TOPS/cm² まで高め、AI 推論タスクに対して高密度な演算能力を提供します。

2. フレックス・リジッド一体構造+3D配線:フレキシブル部品によってリジッド基板同士を接続する3D配線構造を採用し、コネクタを60%削減し、信号伝送経路を30%短縮、信号遅延を50ns以内に抑えています。インテリジェント端末向けPCBにおいて、この構造はデバイスの薄型・軽量化ニーズを満たすだけでなく、リアルタイムAIインタラクションの応答速度も確保します。

エッジコンピューティング向けのサーバーアプリケーションにおいて、高密度実装技術によりPCB面積の40%を割り当て、16チャネルの並列データ処理をサポートすることで、AIのリアルタイム推論における「小型サイズと高い演算能力」という二重の要求を満たし、エッジシナリオでAIを展開するためのハードウェアプラットフォームを提供します。

III. コンピューティングパワー支援の最適化:AI機器の「放熱と電源供給のジレンマ」を打破する

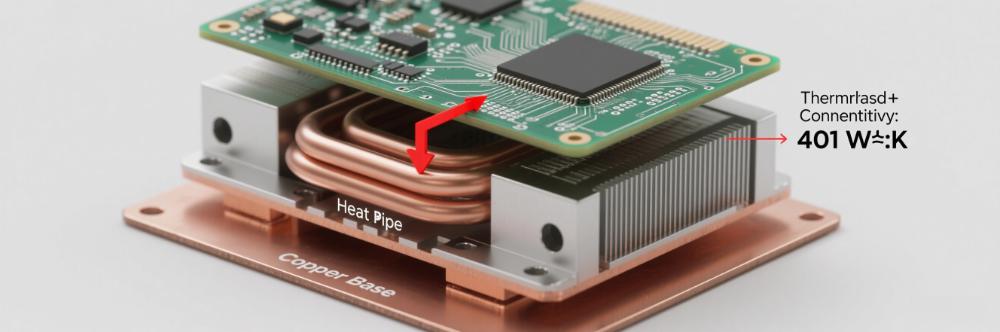

AI機器の深刻な消費電力特性(単一チップで最大300Wの消費電力)は、PCBの放熱性能および電源安定性に大きな課題をもたらします。放熱が遅れるとチップの接合部温度が上昇し、演算能力の低下を招きます。また、電源のリップルが過大であると、高い演算能力を持つチップの瞬時電力需要を満たすことができません。これらの制約を克服するためには、構造設計と回路設計を同時に最適化する必要があります。

(I) 放熱ソリューションの革新

「銅ベース+埋め込みヒートパイプ」の複合放熱構造を構築し、PCB の熱伝導率を 5W/(m·K) まで高めました。これは従来のアルミ基板と比べて 60%の向上に相当します。AI サーバー用 PCB において、この構造は周囲温度 40℃ の環境下でもチップ接合部温度を 85℃ 未満に制御し、高温による演算性能の周波数低下を抑制します。

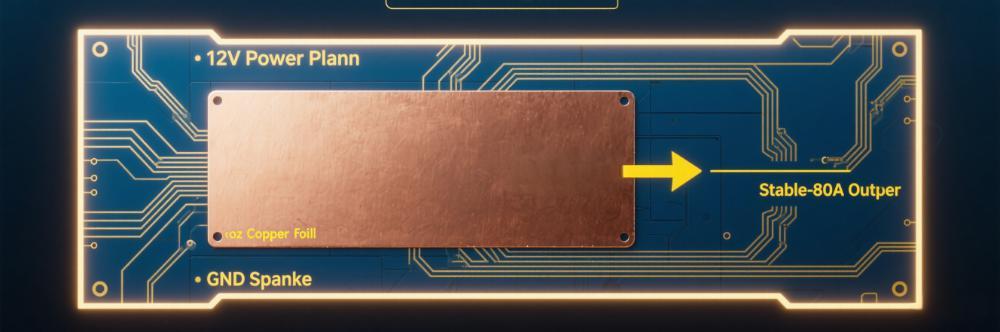

(II)配電ネットワークの最適化

2オンス厚の銅箔とマルチグループ電源プレーン設計を採用することで、電源分配ネットワークを最大化し、電源リップルを±2%以内に制御するとともに、12V/80Aの信頼性の高い大電流出力を実現します。PCB AIトレーニングカードにおいて、本ソリューションは高い演算能力を持つチップの瞬時電力消費要求を満たし、長時間の高負荷動作時におけるトレーニングカードの信頼性運転を40%向上させ、演算能力の利用率を85%から95%へと高めます。