ด้วยความก้าวหน้าอย่างต่อเนื่องของเทคโนโลยีอิเล็กทรอนิกส์ ความถี่สัญญาณนาฬิกาที่สูงขึ้นเรื่อย ๆ ในระบบดิจิทัล และเวลาขอบสัญญาณขาขึ้นที่สั้นลงเรื่อย ๆ ทำให้ระบบ PCB กลายเป็นโครงสร้างระบบที่มีประสิทธิภาพสูง ซึ่งมากกว่าการเป็นเพียงแพลตฟอร์มสำหรับรองรับอุปกรณ์เท่านั้น จากมุมมองด้านสมรรถนะทางไฟฟ้า การเชื่อมต่อระหว่างสัญญาณความเร็วสูงไม่สามารถถือได้ว่าเป็นการส่งผ่านที่ราบรื่นหรือโปร่งใสอีกต่อไป และอิทธิพลของการเชื่อมต่อระหว่างลายวงจรต่อแผงวงจรพิมพ์ความเร็วสูงและคุณสมบัติของแผงวงจรไม่สามารถละเลยได้อีกต่อไป การจัดการปัญหาความสมบูรณ์ของสัญญาณอย่างมีประสิทธิภาพ รวมถึงการสะท้อน การครอสทอล์ก ความหน่วง การเรียกใช้ และการแมตช์อิมพีแดนซ์ที่เกิดจากการเชื่อมต่อสัญญาณความเร็วสูง และการรับประกันคุณภาพของการส่งสัญญาณ เป็นปัจจัยที่กำหนดความสำเร็จของการออกแบบ

ทฤษฎีพื้นฐานของความสมบูรณ์ของสัญญาณบนแผงวงจรพิมพ์ (PCB)

• วงจรความเร็วสูงและหลักการกำหนดของมัน

คำจำกัดความของวงจรความเร็วสูงมีอยู่หลัก ๆ สองรูปแบบ ด้านหนึ่ง ในวงจรเมื่อความหน่วงของสัญญาณดิจิทัลบนสายส่งมีค่ามากกว่า 20% ของเวลาขอบสัญญาณขาขึ้น วงจรนี้สามารถถือได้ว่าเป็นวงจรความเร็วสูง อีกด้านหนึ่ง ในวงจรเมื่อความถี่ของวงจรดิจิทัลเชิงอนาล็อกถึงหรือเกินช่วง 45MHz ถึง 50MHz วงจรนั้นจะถือว่าเป็นวงจรความเร็วสูง

โดยพื้นฐานแล้ว ถ้าแความยาวของลีดมากกว่าทีรวงจรจะถือเป็นวงจรความเร็วสูง หากLน้อยกว่าทีรวงจรจะถือเป็นวงจรความเร็วต่ำ ที่นี่Trหมายถึงเวลาขอบขาขึ้นของพัลส์

• ความเร็วในการส่งสัญญาณและเวลาไต่ระดับขอบสัญญาณพัลส์

อัตราความเร็วในการส่งผ่านสัญญาณในอากาศคือ 3 x 108ม./วินาที; ค่าคงที่ไดอิเล็กทริกของ FR4 ซึ่งเป็นวัสดุของแผ่นวงจรพิมพ์ แสดงเป็น εรนั่นคือ 4. อัตราความเร็วในการส่งสัญญาณใน PCB สามารถคำนวณได้โดยใช้สูตร .

.

Vpเท่ากับ 15 ซม./นาโนวินาที ซึ่งประมาณ 6 นิ้ว/นาโนวินาที เวลาไต่ขึ้นของขอบสัญญาณพัลส์ทีร=1/(10 xฟคลิก) และเวลาขอบขาขึ้นของสัญญาณ 100MHz คือ 1ns เมื่อความหน่วงของสัญญาณบนการเดินลาย PCB มากกว่า 20% ของเวลาขอบขาขึ้น จะเกิดการสะท้อนอย่างเห็นได้ชัดบนสัญญาณ สำหรับสัญญาณสี่เหลี่ยมที่มีเวลาขอบขาขึ้น 1ns (100MHz) เมื่อความยาวการเดินลายของ PCB มากกว่า 0.2ns x 6 = 1.2 นิ้ว จะเกิดการสะท้อนรุนแรงบนสัญญาณ ดังนั้น ความยาววิกฤตคือ 1.2 นิ้ว (ประมาณ 3 ซม.)

• อิมพีแดนซ์ลักษณะเฉพาะ

อิมพีแดนซ์ลักษณะเฉพาะเป็นพารามิเตอร์ที่สำคัญในการแมตช์อิมพีแดนซ์ ซึ่งมีผลต่อการสะท้อน การเรียก การโอเวอร์ชูตและอันเดอร์ชูต และเกี่ยวข้องโดยตรงกับความสมบูรณ์ของการส่งสัญญาณความเร็วสูง ซึ่งมีความสำคัญอย่างมากในการออกแบบความเร็วสูง

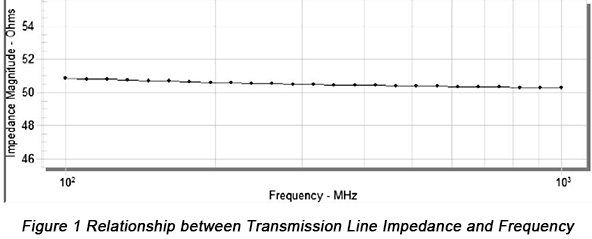

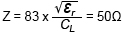

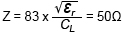

สัญญาณถูกส่งผ่านตามสายส่ง ซึ่งอัตราส่วนระหว่างแรงดันไฟฟ้าและกระแสไฟฟ้าถูกมองว่าเป็นอิมพีแดนซ์ชั่วขณะ อิมพีแดนซ์ชั่วขณะบนสายส่งถูกคำนวณโดยใช้สูตร ในสูตรนี้คlหมายถึงค่าความจุต่อหนึ่งหน่วยความยาว ซึ่งมีหน่วยเป็น pF/นิ้ว (โดยปกติจะเป็น 3.3 pF/นิ้ว) เมื่ออิมพีแดนซ์ชั่วขณะตามแนวสายส่งมีค่าเป็นค่าคงที่ ค่านี้จะถือเป็นอิมพีแดนซ์ลักษณะเฉพาะของสายส่ง สำหรับไมโครสตริปไลน์และสตริปไลน์บนแผ่น PCB สามารถคำนวณค่าอิมพีแดนซ์ลักษณะเฉพาะได้ด้วยเครื่องมือออกแบบสายส่ง Polar Si9000 ดังแสดงในรูปที่ 1

ในสูตรนี้คlหมายถึงค่าความจุต่อหนึ่งหน่วยความยาว ซึ่งมีหน่วยเป็น pF/นิ้ว (โดยปกติจะเป็น 3.3 pF/นิ้ว) เมื่ออิมพีแดนซ์ชั่วขณะตามแนวสายส่งมีค่าเป็นค่าคงที่ ค่านี้จะถือเป็นอิมพีแดนซ์ลักษณะเฉพาะของสายส่ง สำหรับไมโครสตริปไลน์และสตริปไลน์บนแผ่น PCB สามารถคำนวณค่าอิมพีแดนซ์ลักษณะเฉพาะได้ด้วยเครื่องมือออกแบบสายส่ง Polar Si9000 ดังแสดงในรูปที่ 1

ปัจจัยที่มีผลต่อความสมบูรณ์ของสัญญาณและแนวทางแก้ไข

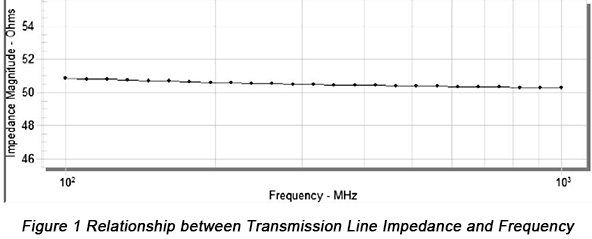

• การแมตช์อิมพีแดนซ์

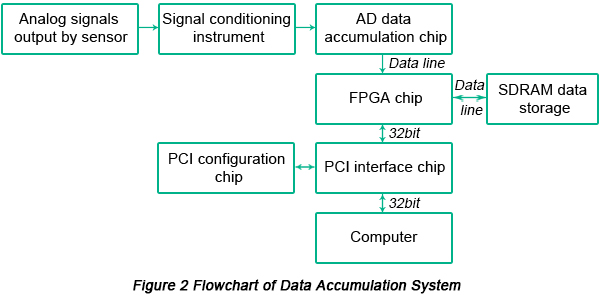

การแมตช์อิมพีแดนซ์เป็นสิ่งจำเป็นในการออกแบบวงจรความเร็วสูงเพื่อให้มั่นใจถึงการส่งผ่านข้อมูลที่รวดเร็วและถูกต้อง ระบบสะสมข้อมูลโดยทั่วไปประกอบด้วยเซนเซอร์ เครื่องมือปรับสภาพสัญญาณ ชิปสะสมข้อมูล AD, FPGA และ SDRAM ดังแสดงในรูปที่ 2

AD9649 ถูกใช้เป็นชิป AD ด้วยแหล่งจ่ายไฟ 1.8V และการสุ่มตัวอย่างแบบขนานผ่านบัสข้อมูล 14 บิต ความถี่ในการสุ่มตัวอย่างถูกตั้งไว้ที่ 20M เลือกใช้ PCI9054 เป็นชิปอินเทอร์เฟซ PCI ซึ่งรองรับการส่งถ่ายข้อมูลแบบ DMA เลือกใช้ 93LC66B เป็นชิปกำหนดค่าของ PCI ใช้ HY57V561620FTP-H เป็นหน่วยเก็บข้อมูล ซึ่งประกอบด้วย 4 BANK โดยแต่ละ BANK มีพื้นที่หน่วยความจำขนาด 4M x 16 บิต มีสายแอดเดรสแถว 13 เส้น และสายแอดเดรสคอลัมน์ 9 เส้น เลือกใช้ EP1C6F256C8 เป็น FPGA โดยมีแรงดันเทอร์มินัล 3.3V และแรงดันแกน 1.5V บัส PCI มีความกว้าง 32 บิต พร้อมสัญญาณนาฬิกา 33MHz ที่ใช้เป็นสัญญาณนาฬิกาสำหรับการเขียนและอ่าน และความเร็วสูงสุดของการเขียนและอ่านสูงถึง 132MByte ต่อวินาที ซึ่งสามารถรองรับการส่งถ่ายข้อมูลความเร็วสูงของข้อมูลที่สะสมได้

ควรคำนึงถึงองค์ประกอบต่อไปนี้ในกระบวนการออกแบบแผงวงจรพิมพ์ (PCB):

a.ในฐานะที่เป็นส่วนผสมระหว่างดิจิทัลและแอนะล็อก วงจรแปลงสัญญาณ AD เป็นหนึ่งในจุดสำคัญของการออกแบบ PCB เนื่องจากส่วนดิจิทัลมีความถี่สูง ส่วนแอนะล็อกจึงมีความไวต่อสัญญาณรบกวนมาก หากไม่มีการจัดการที่เหมาะสม สัญญาณดิจิทัลจะมีแนวโน้มไปรบกวนสัญญาณแอนะล็อก ทำให้เกิดปัญหา EMI หลักการที่ผู้ออกแบบควรปฏิบัติคือ: ประการแรก กราวด์ดิจิทัลและกราวด์แอนะล็อกควรถูกแยกออกจากกันบน PCB ที่มีสัญญาณผสมกัน; ประการที่สอง ควรจัดกลุ่มอุปกรณ์อิเล็กทรอนิกส์แบบแอนะล็อกและดิจิทัล โดยให้กราวด์แอนะล็อกกระจายอยู่ในบริเวณแอนะล็อก และกราวด์ดิจิทัลกระจายอยู่ในบริเวณดิจิทัล; ประการที่สาม ให้เชื่อมต่อกราวด์แอนะล็อกและกราวด์ดิจิทัลด้วยลูกปัดแม่เหล็กบริเวณแนวแบ่งเขต มาตรการเหล่านี้สามารถทำให้เกิดการแยกกราวด์ดิจิทัลและกราวด์แอนะล็อกได้อย่างมีประสิทธิภาพ

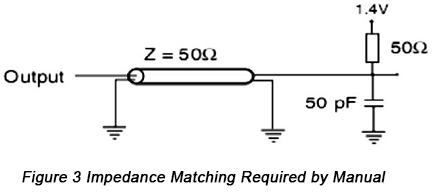

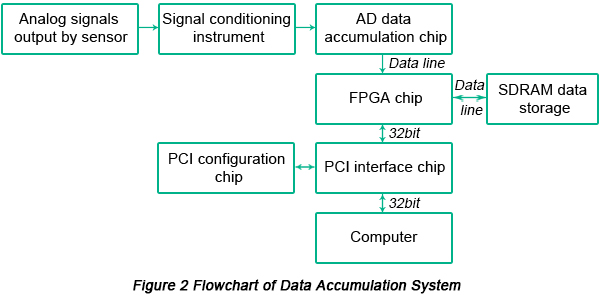

ข.SDRAM ถูกนำมาใช้ในระบบสะสมข้อมูล และในคู่มือได้ระบุไว้อย่างชัดเจนว่า เส้นสัญญาณข้อมูลที่เชื่อมต่อกับ FPGA จะต้องถูกกำหนดค่าให้มีการแมตช์อิมพีแดนซ์ที่ 50Ω เพื่อให้มั่นใจในการส่งข้อมูลความเร็วสูง ดังที่แสดงในรูปที่ 3

หลังจากที่ FPGA เขียนข้อมูลสะสมลงใน SDRAM แล้ว จำเป็นต้องทำการรีเฟรชอย่างต่อเนื่องเพื่อคงสภาพข้อมูลไว้ และคาบเวลารีเฟรชของแต่ละแถวต้องเร็วกว่า 64 มิลลิวินาที

ขั้นตอนของการแมตช์อิมพีแดนซ์ด้วยซอฟต์แวร์ Polar Si9000 แสดงดังต่อไปนี้:

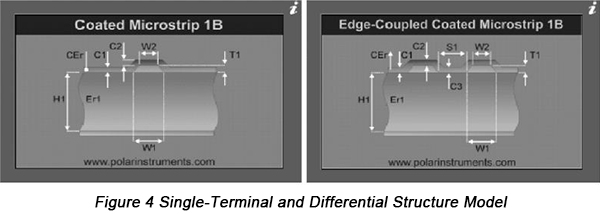

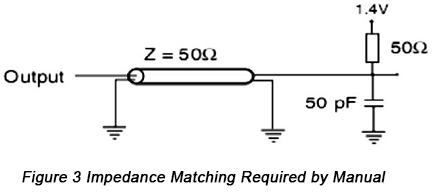

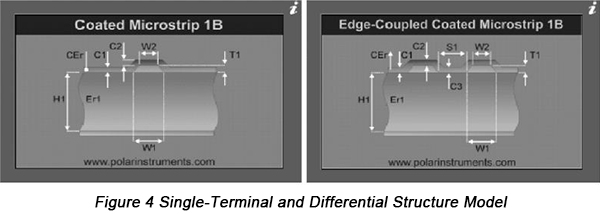

a.สายสัญญาณความเร็วสูงควรวิ่งผ่านบนผิวด้านบนของแผ่น PCB และควรหลีกเลี่ยงการใช้รูให้มากที่สุด โครงสร้างไมโครสตริปลายน์ถูกเลือกใช้ในซอฟต์แวร์ ดังแสดงในรูปที่ 4

การแมตช์อิมพีแดนซ์ที่ 50Ω โดยทั่วไปจะดำเนินการกับการเดินสายแบบขั้วเดียว และการแมตช์อิมพีแดนซ์ที่ 90Ω โดยทั่วไปจะดำเนินการกับการเดินสายแบบดิฟเฟอเรนเชียล (เช่น USB2.0 D+, D-)

ข.ค่าการแมตช์อิมพีแดนซ์ที่จำเป็นและค่าที่เฉพาะเจาะจงของการผลิตแผงวงจรพิมพ์เทคนิคจะถูกกรอกลงในส่วนติดต่อผู้ใช้ของซอฟต์แวร์พร้อมด้วยพารามิเตอร์ต่าง ๆ รวมถึงความหนาของไดอิเล็กทริก ค่าคงที่ไดอิเล็กทริกของวัสดุ PCB ความหนาของฟอยล์ทองแดง ความหนาของน้ำมันสีเขียว และค่าคงที่ไดอิเล็กทริกของน้ำมันสีเขียว

|

รายการ

|

คำอธิบาย

|

ค่าอ้างอิงและค่าที่คำนวณได้

|

| H1 |

ความหนาของไดอิเล็กทริก (วัสดุ PP หรือแผ่นบอร์ด) |

3.5-8.5ล้าน |

| Er1 |

ค่าคงที่ไดอิเล็กทริกของวัสดุบอร์ด |

4-4.6 |

| W1 |

ความกว้างของการกำหนดเส้นทางสัญญาณ |

ขึ้นอยู่กับค่าความอิมพีแดนซ์ |

| C1 |

ความหนาของชั้นไอโอแอลสีเขียวของวัสดุฐาน |

0.8ล้าน |

| C2 |

ความหนาของน้ำมันสีเขียวบนทองแดง |

0.5ล้าน |

| CEr |

ค่าคงที่ไดอิเล็กทริกของกรีนออกซ์ |

3.3 |

| โซ |

ค่าความต้านทานที่ต้องทำการแมตช์ |

เทอร์มินัลเดี่ยว: 50Ω

ดิฟเฟอเรนเชียล: 90Ω |

สามารถทราบพารามิเตอร์เฉพาะของเทคนิคการผลิตได้ผ่านการสื่อสารกับผู้ผลิตแผงวงจรพิมพ์เพื่อให้สามารถคำนวณความกว้างของลายวงจรนำสัญญาณได้ สำหรับไมโครสตริปไลน์แบบดิฟเฟอเรนเชียล จะต้องคำนวณระยะห่างระหว่างลายวงจรนำสัญญาณ (S1) ด้วย

ค.หากความกว้างของลายวงจรที่คำนวณได้มีขนาดค่อนข้างใหญ่และไม่สามารถทำการเดินลายบนแผ่น PCB ได้สำเร็จ จำเป็นต้องมีการสื่อสารเพิ่มเติมกับผู้ผลิตแผ่น PCB เพื่อปรับพารามิเตอร์ในเทคนิคการผลิตให้สอดคล้องกับข้อกำหนดของการออกแบบ

• การรบกวนสัญญาณ

ครอสทอล์กหมายถึงสัญญาณรบกวนแรงดันไฟฟ้าที่ไม่คาดคิดบนสายส่งที่อยู่ติดกัน อันเกิดจากการคัปปลิงทางแม่เหล็กไฟฟ้าเมื่อมีการส่งสัญญาณบนสายส่ง ครอสทอล์กที่มากเกินไปอาจทำให้วงจรกระตุ้นการทำงานผิดพลาด ส่งผลให้ระบบไม่สามารถทำงานได้ตามปกติ ครอสทอล์กเกิดจากการคัปปลิงทางแม่เหล็กไฟฟ้า และการคัปปลิงแบ่งออกเป็นการคัปปลิงแบบความจุไฟฟ้าและการคัปปลิงแบบการเหนี่ยวนำ แบบแรกคือสัญญาณรบกวนทางแม่เหล็กไฟฟ้าที่เกิดจากกระแสเหนี่ยวนำซึ่งเกิดจากการเปลี่ยนแปลงของแรงดันไฟฟ้าที่แหล่งรบกวน ส่วนแบบหลังคือสัญญาณรบกวนทางแม่เหล็กไฟฟ้าที่เกิดจากแรงดันเหนี่ยวนำซึ่งเกิดจากการเปลี่ยนแปลงของกระแสไฟฟ้าที่แหล่งรบกวน เมื่อสถานะของแหล่งรบกวนเปลี่ยนไป จะเกิดพัลส์รบกวนต่อเนื่องบนวัตถุที่ถูกรบกวน ซึ่งพบได้บ่อยมากในระบบความเร็วสูง

มาตรการในการจัดการกับการรบกวนสัญญาณข้ามช่องสัญญาณมีดังต่อไปนี้:

a.ควรรักษาความตั้งฉากของทิศทางการเดินสายระหว่างเลเยอร์ที่อยู่ติดกัน ควรหลีกเลี่ยงการใช้ทิศทางเดียวกันในเลเยอร์ที่อยู่ติดกันซึ่งมีสัญญาณคนละเส้นกันเพื่อลดการเกิดครอสทอล์ก โดยเฉพาะอย่างยิ่งเมื่ออัตราความเร็วของสัญญาณค่อนข้างสูง ควรพิจารณาใช้กราวด์เพื่อแยกเลเยอร์การเดินสาย และควรแยกเส้นสัญญาณออกจากกันด้วยเส้นสัญญาณกราวด์

ข.เพื่อเป็นการลดการรบกวนระหว่างสาย การเว้นระยะห่างระหว่างสายควรมีขนาดมากเพียงพอ เมื่อระยะห่างระหว่างจุดกึ่งกลางของสายไม่น้อยกว่าสามเท่าของความกว้างของสาย จะสามารถป้องกันสนามไฟฟ้าได้ 70% จากการรบกวนซึ่งกันและกัน ซึ่งเรียกว่าหลักการ 3W

ค.ในกรณีที่สายสัญญาณความเร็วสูงเป็นไปตามข้อกำหนด สามารถทำการแมตช์ที่ขั้วต่อร่วมเพื่อช่วยลดหรือขจัดการสะท้อน และเพื่อลดการรบกวนระหว่างสัญญาณ

การประยุกต์ใช้วิธีการออกแบบความสมบูรณ์ของสัญญาณ

ในกระบวนการออกแบบ PCB ได้มีการสรุปกฎการออกแบบจำนวนมากขึ้นอยู่กับทฤษฎีความสมบูรณ์ของสัญญาณ โดยอ้างอิงจากกฎเหล่านี้กฎการออกแบบ PCBความถูกต้องของสัญญาณสามารถทำได้ดีขึ้น ในกระบวนการออกแบบ PCB จำเป็นต้องทราบข้อมูลการออกแบบอย่างละเอียด รวมถึง:

a.ตำแหน่งการจัดวางคอมโพเนนต์ มีข้อกำหนดพิเศษใดหรือไม่สำหรับคอมโพเนนต์ที่มีกำลังไฟสูงและการกระจายความร้อนสูงบนคอมโพเนนต์แบบชิป

ข.การจำแนกสัญญาณ อัตราความเร็ว ทิศทางการส่งสัญญาณ และข้อกำหนดการแมตช์ความต้านทาน

ค.ความสามารถในการขับสัญญาณ สัญญาณหลัก และมาตรการป้องกัน

d.ประเภทของเพาเวอร์ กราวด์ ข้อกำหนดขีดจำกัดสัญญาณรบกวนของเพาเวอร์และกราวด์ การตั้งค่าพื้นที่เพาเวอร์และพื้นที่กราวด์และการแบ่งแยก

จ.ประเภทและอัตราความเร็วของสายสัญญาณนาฬิกา แหล่งที่มาของสายสัญญาณนาฬิกา ทิศทาง ข้อกำหนดด้านความหน่วงของสัญญาณนาฬิกา และข้อกำหนดการเดินสายสูงสุด

นวัตกรรมด้านอิเล็กทรอนิกส์ต้องการการออกแบบแผงวงจรพิมพ์ (PCB) ที่ซับซ้อนเพื่อรักษาความถูกต้องของสัญญาณที่ความเร็วสูง โดยแก้ไขปัญหาต่าง ๆ เช่น การสะท้อนสัญญาณและการรบกวนระหว่างสัญญาณ การวางลายวงจรอย่างแม่นยำ การจัดวางอุปกรณ์ และการแมตช์อิมพีแดนซ์อย่างถูกต้องล้วนมีความสำคัญอย่างยิ่งเพื่อให้มั่นใจถึงประสิทธิภาพการทำงานที่ไร้ที่ติ

PCBCart โดดเด่นด้วยโซลูชัน PCB ประสิทธิภาพสูงที่ให้ความสำคัญกับความสมบูรณ์ของสัญญาณที่ดีขึ้นและความแม่นยำของการออกแบบอย่างแท้จริง ความเชี่ยวชาญด้านวัสดุและกระบวนการที่ล้ำสมัยของเราช่วยรับประกันแผ่นวงจรพิมพ์ระดับแนวหน้าสำหรับการใช้งานในอนาคต ร่วมเป็นพาร์ทเนอร์กับ PCBCart เพื่อยกระดับโครงการอิเล็กทรอนิกส์ของคุณให้ก้าวไปอีกขั้น ขอใบเสนอราคาวันนี้และสัมผัสประสิทธิภาพระดับแนวหน้าด้วยโซลูชันแบบกำหนดเองของเรา

ยกระดับการออกแบบของคุณ: ขอใบเสนอราคา PCB ความเร็วสูงอย่างปลอดภัยตอนนี้

แหล่งข้อมูลที่เป็นประโยชน์:

•เทคนิคการเดินสาย 3 แบบในการออกแบบวงจรสัญญาณความเร็วสูงบนแผ่นวงจรพิมพ์ (PCB)

•วิธีการลดการสะท้อนสัญญาณในการออกแบบเลย์เอาต์ PCB ความเร็วสูง

•การวิเคราะห์ความถูกต้องของสัญญาณและการออกแบบ PCB บนวงจรผสมดิจิทัล-อนาล็อกความเร็วสูง

•การควบคุมอิมพีแดนซ์ของเวียและอิทธิพลต่อความสมบูรณ์ของสัญญาณในการออกแบบแผงวงจรพิมพ์ (PCB)

•บริการผลิตแผงวงจรพิมพ์ (PCB) แบบครบวงจรจาก PCBCart - ตัวเลือกเสริมที่เพิ่มมูลค่าหลากหลาย

•บริการประกอบแผงวงจรพิมพ์ขั้นสูงจาก PCBCart - เริ่มต้นเพียง 1 ชิ้น

.

. ในสูตรนี้

ในสูตรนี้