ระบบอิเล็กทรอนิกส์สมัยใหม่กำลังพัฒนาไปในทิศทางของแพ็กเกจขนาดเล็ก ขนาดวงจรรวมขนาดใหญ่ และความเร็วสูง เนื่องจากความหนาแน่นของชิปใน SLSI (super-large-scale integration) เพิ่มสูงขึ้นอย่างต่อเนื่อง ซึ่งก่อให้เกิดปัญหาที่หลีกเลี่ยงไม่ได้บางประการ เช่น วิธีการวิเคราะห์และจัดการกับปัญหาการเชื่อมต่อและการซ้อนทับกันในงานออกแบบวงจรความเร็วสูง ปัจจุบันความถี่วิทยุของผลิตภัณฑ์อิเล็กทรอนิกส์สูงถึงระดับหลายร้อยหรือหลายพันเมกะเฮิรตซ์ และทั้งขอบสัญญาณขาขึ้นและขาลงมีความชันสูงมาก ทำให้กฎการวางลายวงจร PCB และค่าคงที่ไดอิเล็กทริกของวัสดุฐานมีความสำคัญอย่างยิ่งต่อสมรรถนะทางไฟฟ้าของระบบในกระบวนการออกแบบผลิตภัณฑ์ดังกล่าว

ในฐานะกระบวนการและขั้นตอนที่สำคัญในงานวิจัยผลิตภัณฑ์อิเล็กทรอนิกส์ส่วนใหญ่ในปัจจุบันแผงวงจรพิมพ์ความเร็วสูงการออกแบบได้พบปัญหาหลักต่าง ๆ รวมถึงปัญหาเรื่องเวลา การรบกวนจากสัญญาณรบกวน และ EMI (การรบกวนทางแม่เหล็กไฟฟ้า) ซึ่งวิธีการแก้ไขนั้นเกี่ยวข้องกับการทำงานตามปกติของการออกแบบระบบ

ปัจจุบัน วิธีการออกแบบแบบดั้งเดิมทำให้ความน่าเชื่อถือและอัตราความสำเร็จของผลิตภัณฑ์อยู่ในระดับต่ำ ซึ่งทำให้การวิจัยด้านการออกแบบ PCB ความเร็วสูงในระบบประยุกต์แบบฝังตัวมีคุณค่าทางปฏิบัติสูงและได้รับความคาดหวังอย่างกว้างขวางในตลาด

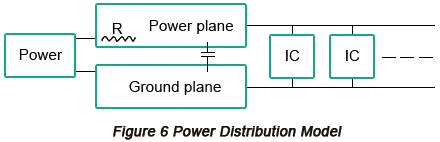

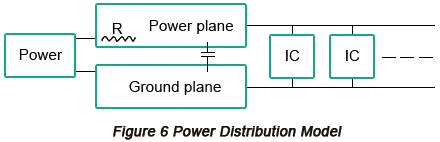

รูปที่ 1 แสดงโครงสร้างการทำงานของ RTU (remote terminal unit) แบบฝังตัว

จากรูปที่ 1 จะเห็นได้ว่าระบบนี้เป็นโครงสร้างการสื่อสารในแนวตั้ง ซึ่งประกอบด้วย ชั้นการสะสมข้อมูลที่มีหน่วยพลังงานไฟฟ้า หน่วยเซนเซอร์ และหน่วยวัดปริมาณแบบแอนะล็อก ชั้นการส่งผ่านข้อมูลที่มีกเกตเวย์ซึ่งปรับแต่งข้อมูลในชั้นการสะสมข้อมูลผ่านคำสั่งจากศูนย์วิศวกรที่รับข้อมูลจากอินเทอร์เน็ต และชั้นการประมวลผลข้อมูลที่ดำเนินการโดยซอฟต์แวร์ตรวจสอบแบบแอปพลิเคชัน (APP) เพื่อจัดเก็บและวิเคราะห์ข้อมูลแบบเรียลไทม์ และสร้างกราฟข้อมูลแสดงต่อส่วนติดต่อผู้ใช้ เพื่อเพิ่มความยืดหยุ่นและประสิทธิภาพในการจัดการของการสะสมข้อมูล

ฮาร์ดแวร์ของระบบ RTU IoT แบบฝังตัวนี้ประกอบด้วย USB2.0, โปรเซสเซอร์ AT91SAM9263, CAN, SDRAM, Nand Flash, Data Flash, คอนโทรลเลอร์ Ethernet, ชิปนาฬิกา, อินเทอร์เฟซ RS232/485, ส่วนจัดการพลังงาน และส่วนสะสมข้อมูล

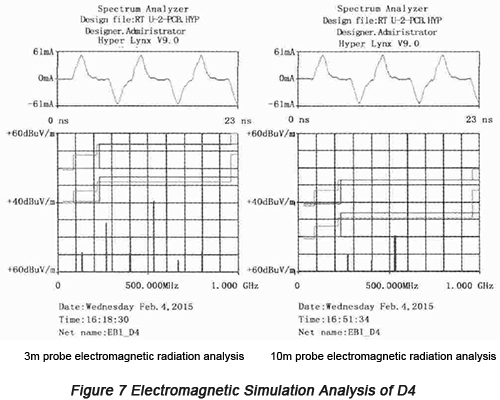

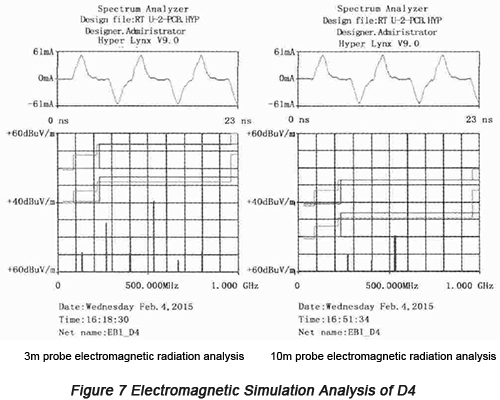

ด้วยการทำงานบนระบบปฏิบัติการลินุกซ์ การออกแบบนี้มีความสามารถที่สูงขึ้นในการจัดการหน่วยความจำและอุปกรณ์ ทำให้สามารถดำเนินการจัดตารางเวลางานแบบหลายภารกิจในเวลาจริง ซึ่งประกอบด้วยอัลกอริทึมที่ซับซ้อนและโพรโทคอลการสื่อสาร เพื่อรับผิดชอบการเชื่อมต่อเครือข่าย การสื่อสารข้อมูล และการสะสมการกำหนดค่า รูปที่ 2 แสดงแผงวงจร RTU ที่ออกแบบในบทความนี้

ด้วยการรองรับการทำงานแบบดูอัลสแตกของ IPv6 และ IPv4 ระบบนี้สามารถตอบสนองความต้องการด้านความรวดเร็วและความสามารถแบบเรียลไทม์ได้ ในด้านการจัดเก็บข้อมูล ระบบสามารถตอบสนองความต้องการในการจัดเก็บข้อมูลภายในเครื่องได้แม้ในกรณีที่การสื่อสารถูกตัดขาด ในด้านอินเทอร์เฟซการสื่อสาร ระบบมีอินเทอร์เฟซการสื่อสารข้อมูลภาคสนามที่หลากหลาย ได้แก่ RS485, RS232 และ CAN รองรับโปรโตคอลการสื่อสาร Modbus RTU และสามารถตอบสนองความต้องการของอินเทอร์เฟซที่แตกต่างกันและอัตราการสื่อสารที่หลากหลาย

• การออกแบบการซ้อนชั้น PCB ของระบบ

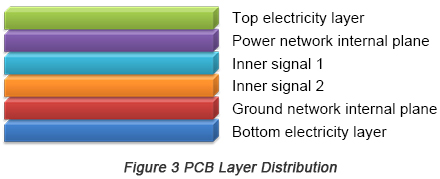

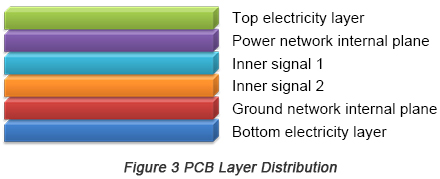

จำนวนชั้นของแผงวงจรพิมพ์ (PCB) โดยทั่วไปจะอยู่ในช่วง 2 ถึง 32 ชั้น ขึ้นอยู่กับความยากง่ายของการออกแบบ แผงวงจรพิมพ์แบบ 6 ชั้นในงานออกแบบนี้ถูกกำหนดขึ้นตามความหนาแน่นของแพ็กเกจชิ้นส่วน อวกาศการวางเลย์เอาต์และการเดินสายที่มีจำกัด และความถี่สัญญาณที่สูงการกระจายชั้น PCBดังแสดงในรูปที่ 3 ด้านล่าง

การกำหนดค่าเส้นสตริปถูกนำมาใช้สำหรับ FLASH และ SDRAM ในระบบนี้ และการเดินสายถูกดำเนินการบน Inner Signal 1 และ Inner Signal 2

• กฎข้อจำกัดของ PCB ในระบบนี้

ในการออกแบบ PCB ความเร็วสูง ความต่อเนื่องของอิมพีแดนซ์และ EMI ได้รับผลกระทบอย่างมากจากระยะห่าง ความยาวและความกว้างของลายวงจร รวมถึงการจัดการลูปที่อยู่ติดกัน คุณภาพของการจัดวางและการเดินสายของอุปกรณ์สัมพันธ์โดยตรงกับความสำเร็จของการออกแบบขั้นสุดท้าย ดังนั้นจึงจำเป็นต้องกำหนดกฎข้อบังคับของ PCB ให้เหมาะสม

Hyper Lynx มีฟังก์ชันสำหรับการวิเคราะห์การรบกวนของสัญญาณในแผนภูมิ และสามารถประยุกต์ใช้โมเดล IBIS เพื่อจำลองการส่งสัญญาณที่มีการสูญเสีย สัญญาณดิฟเฟอเรนเชียล และโมเดลรูทะลุที่เปลี่ยนแปลงตามความถี่ได้อย่างแม่นยำ โดยจะทำการจำลองโครงข่ายหลักก่อนการเดินลายด้วย Line เพื่อปรับปรุงโครงสร้างการซ้อนชั้นของ PCB และอิมพีแดนซ์ของการเดินลาย และออกแบบกฎข้อบังคับสำหรับการเดินลายโครงข่ายความเร็วสูงของ PCB ก่อนการจำลองผลลัพธ์เพื่อเพิ่มประสิทธิภาพในการออกแบบ

• การจำลอง PCB ของระบบนี้

ในกระบวนการออกแบบ PCB ความเร็วสูง จะใช้แบบจำลองสายส่งในอุดมคติสำหรับการจำลองที่ปลายด้านหน้า โดยจำลองสายสัญญาณจำนวนจำกัดในแต่ละครั้ง อย่างไรก็ตาม สายส่งที่ปลายด้านหลังของ PCB นั้นแท้จริงแล้วคือร่องรอยลายวงจรบน PCB ซึ่งได้รับอิทธิพลจากรูผ่านและการเลื่อนของระนาบ ภายใต้สภาวะเช่นนี้ ผลการจำลองที่ได้จึงมีความน่าเชื่อถืออย่างยิ่ง

ในกระบวนการออกแบบวงจรแกนหลักของระบบ ต้องกำหนดให้ค่าความต้านทานแมตช์ปลายทางของสัญญาณแบบขั้วเดียวอยู่ในช่วง 40 ถึง 60Ω และค่าขีดจำกัดครอสทอล์กระหว่างสายสัญญาณอยู่ที่ 165mV นอกจากนี้ เพื่อให้ตัวควบคุมเครือข่าย DM9000 และ DM9161 สามารถปรับตัวเองให้เข้ากับอัตราความเร็วการสื่อสารที่ 100Mbps ได้ ค่าความต้านทานเชิงผลต่างจะต้องอยู่ในช่วง 100±5Ωการจำลอง PCBถูกนำไปใช้โดยซอฟต์แวร์จำลอง Hyper Lynx ที่พัฒนาโดย Mentor Graphic บน SDRAM, สายสัญญาณดิฟเฟอเรนเชียล Ethernet, ความสมบูรณ์ของพลังงาน และ EMC

a. การออกแบบ SDRAM

ในกระบวนการออกแบบสตริปลายน์ ครอสทอล์กและรูทะลุเป็นสาเหตุหลักที่ทำให้เกิดความหน่วงเวลา แม้ว่าแผ่น PCB จะถูกทำให้เสร็จสมบูรณ์ตามกฎการเดินลายที่กำหนดโดยเครื่องมือจำลองลายเส้น แต่ก็ยังคงมีปัญหาบางอย่างที่หลีกเลี่ยงไม่ได้ เช่น จำนวนขาของอุปกรณ์ที่มากเกินไปและขนาดแผ่น PCB ที่จำกัด ดังนั้นจึงมีความจำเป็นต้องจำลองเครือข่ายหลายเครือข่ายอย่างเหมาะสมผ่านเครื่องมือจำลองระดับบอร์ด

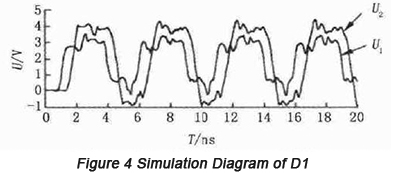

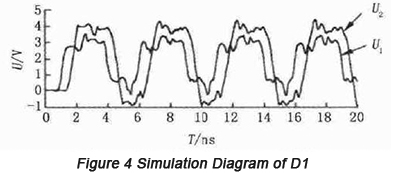

จากผลการจำลอง ความเข้มของสัญญาณครอสทอล์กของเครือข่ายอนาล็อก EBI_D0 และ EBI_D2 มีค่ามากกว่า 165mV เครือข่ายทั้งสองส่งผลกระทบต่อ EBI_D1 และค้นหาตำแหน่งการคัปปลิง เนื่องจากระยะห่างระหว่างลายวงจรแบบงูในบริเวณที่ทำเครื่องหมายสีเหลืองไม่เหมาะสม สามารถอธิบายได้ว่าการเพิ่มระยะห่างของการเดินลายวงจรจะช่วยขจัดปัญหาดังกล่าวได้ อย่างไรก็ตาม สิ่งที่เรากังวลจริง ๆ คือเหตุใดเครือข่าย hack จึงได้รับสัญญาณรบกวนรุนแรงเช่นนี้ เหตุผลอาจอยู่ที่การเลือกตัวต้านทานที่ไม่เหมาะสม ทำให้ค่าความต้านทานอิมพีแดนซ์ไม่แมตช์ จนถึงตอนนี้ ค่าความต้านทานของตัวต้านทานเทอร์มิเนชันที่กำหนดคือ 43.1Ω ภายใต้เงื่อนไขการกระตุ้นที่ความถี่ 220MHz คลื่นการจำลองเชิงวิเคราะห์ของเครือข่าย EBI_D1 แสดงดังรูปที่ 4 ด้านล่าง

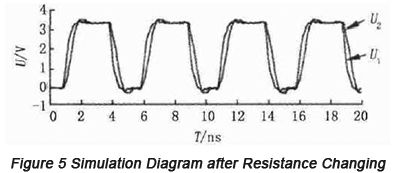

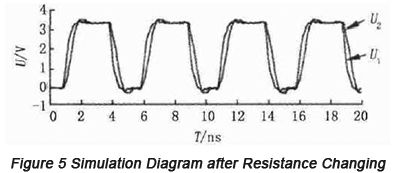

จากรูปที่ 4 ความไม่ต่อเนื่องของอิมพีแดนซ์เกิดขึ้นบนสายส่ง EMI_D1 และเกิดการบิดเบือนกับคลื่นสัญญาณ แม้จะไม่ทำให้เกิดความล้มเหลวของระบบในขั้นเริ่มต้น แต่ก็ยากที่จะรับประกันเสถียรภาพของการทำงานของผลิตภัณฑ์ เมื่อย้อนกลับไปที่การจำลองบนบอร์ด ได้มีการใช้รูทะลุและการจำลองความเสียหายเพื่อเปลี่ยนค่าความต้านทานปลายสายของ EBI_D0 และ EBI_D1 ให้เป็น 46.9Ω ดังนั้น แผนภาพการจำลองของครอสทอล์กหลังจากมีการเปลี่ยนค่าความต้านทานจึงแสดงไว้ในรูปที่ 5 ด้านล่าง

จากรูปนี้สามารถแสดงให้เห็นได้ว่าสัญญาณเครือข่ายได้รับการปรับปรุงดีขึ้น และความเข้มของสัญญาณรบกวนที่เกิดขึ้นบน EBI_D1 ลดลงอย่างเห็นได้ชัด

b. การออกแบบบัสดิฟเฟอเรนเชียลอินเทอร์เน็ต

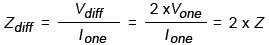

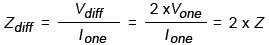

ด้วยคุณสมบัติการเชื่อมต่อความเร็วสูงและ 3GIO โมดูลจำลองบอร์ดที่พัฒนาโดย Hyper Lynx ใช้เส้นทางข้อมูลอนุกรมความเร็วสูงพิเศษและเทคโนโลยีการซิงโครไนซ์ต้นทางบนพื้นฐานของบัสสัญญาณดิฟเฟอเรนเชียล ซึ่งมอบวิธีการแก้ปัญหาที่สะดวกและมีประสิทธิภาพสูงสำหรับการออกแบบ PCB ความเร็วสูง ทั้ง DM9000 และ DM9161 ในระบบนี้มีบัสสัญญาณดิฟเฟอเรนเชียลความเร็วสูงสองคู่: TX+, TX- และ RX+, RX- โดยมีอิมพีแดนซ์ดิฟเฟอเรนเชียลเท่ากับ 100Ω ตามทฤษฎีการส่งผ่าน อิมพีแดนซ์ดิฟเฟอเรนเชียลสามารถคำนวณได้จากสูตร: .

.

ในสูตรนี้ Z หมายถึงอิมพีแดนซ์การส่งผ่านของแต่ละสายสัญญาณ ซึ่งมีผลสำคัญต่อระยะทางการสื่อสารและความสามารถในการต้านทานสัญญาณรบกวน ที่นี่เลือกใช้ DM9000 เพื่อส่งสัญญาณดิฟเฟอเรนเชียลไปยังเครือข่าย TP_E_TX+ และ TP_E_TX- เพื่อให้ลดผลกระทบจากการสะท้อน จึงวางตัวต้านทานค่า 100Ω แบบขนานกับสายสัญญาณพร้อมทั้งใช้รูทะลุ (through-hole)

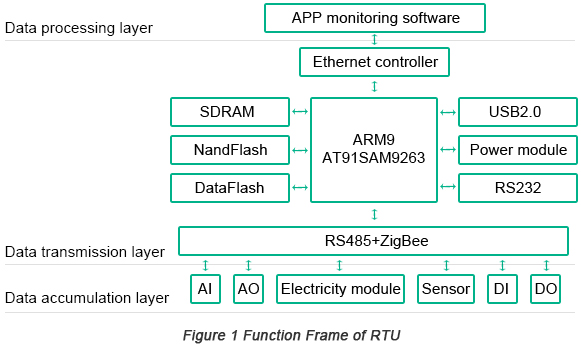

c. การออกแบบความสมบูรณ์ของกำลังไฟของระบบนี้

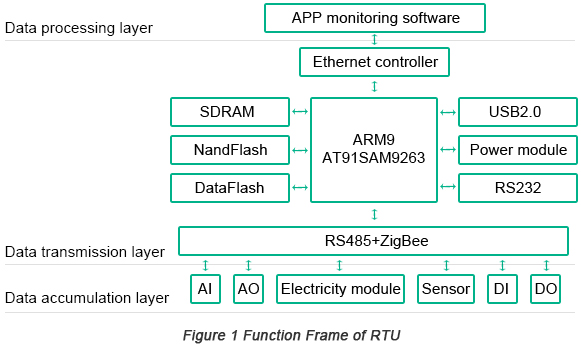

รูปที่ 6 เป็นแบบจำลองการกระจายกำลังไฟฟ้าพื้นฐาน ซึ่งกระแสไฟฟ้าจะถูกส่งไปยังตัวนำแต่ละตัวผ่านชั้นจ่ายไฟ จากนั้นจึงส่งต่อไปยังชั้นกราวด์

ในกระบวนการออกแบบ PCB ความเร็วสูง จำเป็นต้องคำนวณการใช้พลังงานในแต่ละหน่วยของระบบวงจร โดยต้องกระจายความกว้างของโครงข่ายจ่ายไฟให้ถูกต้องและขยายให้เหมาะสม

ความสมบูรณ์ของพลังงานไฟฟ้าของบอร์ด 6 ชั้นสามารถสรุปได้ดังนี้: แรงดันตกคร่อมสูงสุดคือ 2.1mV คิดเป็นประมาณ 0.06%; ความหนาแน่นกระแสสูงสุดคือ 16.3mA/m²; ภายในช่วงที่เหมาะสม หากความหนาแน่นกระแสเกิน 50mA/m² อุณหภูมิของ PCB จะสูงขึ้น ซึ่งจะส่งผลกระทบต่อชิปหลักและลายสัญญาณระหว่างการทำงาน การเพิ่มความกว้างของลายทองแดงสามารถช่วยลดความหนาแน่นกระแส และการเพิ่มความหนาของลายสัญญาณจะช่วยลดอุณหภูมิของ PCB ได้

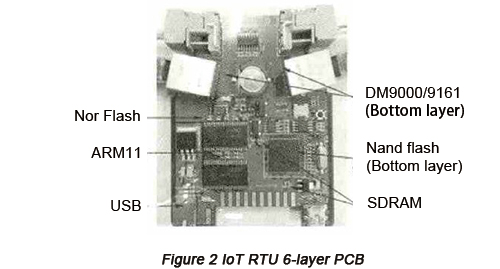

d. การวิเคราะห์ความเข้ากันได้ทางแม่เหล็กไฟฟ้าของระบบ

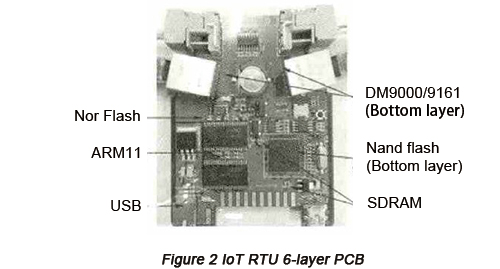

สัญญาณรบกวนแม่เหล็กไฟฟ้ามักถูกส่งผ่านในรูปแบบของคลื่นพาหะที่มีสัญญาณที่เป็นประโยชน์ในลักษณะของการคัปปลิง ในการออกแบบนี้ได้ใช้ซอฟต์แวร์จำลอง Hyper Lynx เพื่อวิเคราะห์ความเข้มของการแผ่รังสีของแผงวงจรพิมพ์ (PCB) หลังการออกแบบเบื้องต้น โดยเลือกเส้นสัญญาณที่สำคัญ D4 ระหว่าง ARM9 และ SDRAM พร้อมตำแหน่งหัววัดที่ระยะ 3 เมตร และ 10 เมตร ตามลำดับ ภายใต้เงื่อนไขที่ใช้แหล่งกระตุ้นความถี่ 220MHz สามารถได้มาซึ่งข้อมูลการจำลองตามมาตรฐานสากลของ FCC และ CISPR ซึ่งแสดงไว้ในรูปที่ 7 ด้านล่าง

จากผลการจำลองพบว่า ระยะห่างที่สั้นจากแผงวงจรพิมพ์ (PCB) ทำให้เกิดการแผ่รังสีสูงจากแผงวงจร และระดับการแผ่รังสีจะเปลี่ยนแปลงไปตามความถี่ของสัญญาณ ในกระบวนการออกแบบวงจรความเร็วสูง สามารถปรับให้เหมาะสมด้านการป้องกันสัญญาณรบกวนของ PCB ได้ ในขณะเดียวกันก็ต้องลดการแผ่รังสีของสัญญาณรบกวนลงด้วย

.

.