PCB erfolgreich in Ihren Warenkorb gelegt

Einfluss des PCB-Layouts auf die EMV-Leistung von Elektronikprodukten

• Einfluss von gemeinsamer Code-Interferenz auf das innere PCB-Signal

Leiterbahnen im Inneren von Leiterplatten (Printed Circuit Boards, PCB) weisen parasitäre Parameter in Bezug auf die Referenzmassefläche auf, und wenn Funktionssignale innerhalb der Leiterplatte übertragen werden, ist derselbe gleichpotentielle Knoten im selben Netz der Schaltung nicht mehr gleichpotentiell. Der Stromichim Inneren der Leiterplatte beginnt es am Quellende, durchläuft eine Reihe von Trägern und kehrt zur Signalquelle zurück, wodurch ein Signal entsteht. Darüber hinaus,ichdazu neigt, entlang des Weges mit geringer Impedanz zu fließen, sodassichbleibt in der Regel unverändert bei stabiler Impedanz.

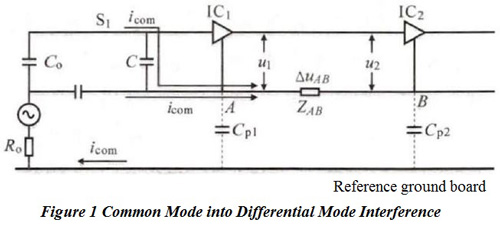

Abbildung 1 zeigt den Prozess, bei dem Gleichtaktstörungen innerhalb der Leiterplatte in Differenzmodusstörungen umgewandelt werden. ichdbezieht sich auf den differentiellen Modusstrom, der innerhalb der Leiterplatte fließt, währendichcombezieht sich auf den Gleichtaktstrom, der entweder von außerhalb der Leiterplatte ausgeht und über die Referenzmasseplatte in die Leiterplatte fließt oder von innerhalb der Leiterplatte ausgeht und über die Referenzmasseplatte in das Innere der Leiterplatte zurückkehrt. Hochfrequenzichcomhat zwei Wege: der erste führt von PunktAzeigenBinnerhalb der Leiterplatte beginnend bei GND; die zweite ist von PunktAzeigenBbeginnend ab Hafen S1zur Leiterplatte im Inneren durch die Kapazität C. ErdungsimpedanzZABführt zur Erzeugung von ΔuAB, sodass beim Anlegen eines normalen Signals an den IC2, Verformung wird stattfinden, um Signal- und Gleichtaktstörungen in Gegentaktstörungen umzuwandeln, die gemäß der Formel, die lautet, einen Einfluss auf das normale Signal ausübenu2=u1-ΔuAB.

Daher, sobaldichcomgelangt über den I/O‑Port oder durch Weltraumstrahlung in das Innere der Leiterplatte (PCB), kann die Gleichtakt-Filterkapazität auf den Signalleitungen der Leiterplatte die Störung nur nach GND ableiten. Die Voraussetzung für dieses Ergebnis ist, dass GND als niedrige Impedanz für den Signalrückfluss betrachtet wird und der Strom stets in Richtung der niedrigsten Impedanz fließt.

• Schlüssel zur Umsetzung des EMV-Designs: Erdungsimpedanz in der Leiterplatte

Der Grund für die Entstehung von EMV durch Hochfrequenzsignale liegt darin, dass das Signalbezugsniveau GND seine Eigenschaft des niedrigen Impedanzwertes nicht aufrechterhalten kann. Mit der Zunahme der ImpedanzZGNDdes Referenzniveaus nimmt auch die Qualität der Signalübertragung ab. Um das Problem der Hochfrequenzstörungen zu lösen, werden übliche Methoden verwendet inEMV-Designwie Filter, Masse und Abschirmung, die eng mit „Masse“ verbunden sind.

Ein Filter kann als Kondensator gegen Masse betrachtet werden, mit zwei Strukturen: Bei der einen wird der X‑Kondensator mit der Signalbezugserde verbunden, bei der anderen wird das Signal über einen Y‑Kondensator oder eine unterschiedliche Erdverbindung innerhalb der Leiterplatte mit dem Metallgehäuse verbunden. Abschirmung kann als Ergebnis der Ausdehnung der Leiterplattenmasse in den Raum betrachtet werden. Der Zweck von Filter oder Abschirmung besteht darin, hochfrequente Gleichtaktstörungen über einen Bypass mit niedriger Impedanz zu führen, damit sie nicht in das normale Betriebssignal einfließen. Ebenso funktionieren all diese Methoden nur, wenn die Masse eine niedrige Impedanz aufweist.

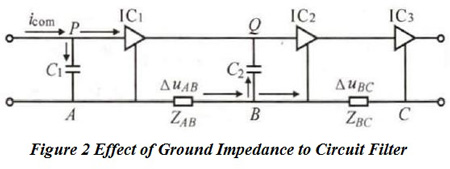

Abbildung 2 zeigt die Auswirkung der Erdimpedanz auf den Schaltungsfilter. ichcomfließt gemäß der Reihenfolge der IC1→IC2→IC1und wenn es zu einem Punkt fließtP,ichcomwird in die Abzweigstromkreise der IC fließen1undC1durch die es von PunktAzuB. Wenn die Impedanz zwischen PunktAundB, das istZAB, ist weit geringer als die Impedanz zwischen PunktPund IC1. In diesem Moment,ichcomfließt von PunktPzuA, IC1Filter kann realisiert werden. Wennichcomfließt zum PunktB, Stromkreise werden auftreten, dieB→CundB→F. Wenn das PCB-Layout nicht gut kontrolliert ist, ist die Impedanz zwischen PunktBundC, das istZBC,ZBC目标语言:de Zu übersetzender Text (bitte nur den Inhalt selbst übersetzen, keine Erklärungen hinzufügen):ZC2+ZF.ZFbezieht sich auf die Impedanz zwischen PunktFund IC2.ichcomfließt rückwärts zur IC2Eingangsport durchC2wenn eine Kapazität, die ursprünglich ausschließlich für IC verwendet wurde2spielt eine Rolle bei der Störung der Signalinvasion.

Um ein Bezugspotential mit niedriger Impedanz zu erzeugen, wird es üblicherweise als Fläche ausgeführt. Allgemein gesprochen kann ein Leiter, dessen Längen-Breiten-Verhältnis kleiner als 5 ist, im Bereich der Technik als niederimpedant angesehen werden. Die Impedanz von Leiterbahnen wird nicht durch ihren Grad an Länge oder Dicke bestimmt. In der traditionellenGrundsätze des PCB-Designsdaher wird eine einpunktige Erdung von analogen Schaltungen dringend empfohlenLeiterplatten-Layout-PrinzipDie Mehrpunkt-Erdung von Digitalschaltungen und die gemischte Erdung von digitalen Modulen und Schaltungen sind nicht mehr geeignet, um EMV-Probleme zu lösen.

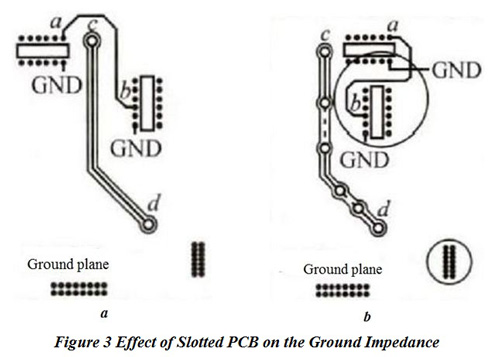

Da alle Rückströme aller Signale einen integrierten Massebezug mit niedriger Impedanz aufweisen müssen, können 4‑lagige oder mehrlagige Leiterplatten mit integrierter Massefläche diese Anforderung erfüllen, während kostengünstige einlagige Leiterplatten dies nicht können. Wenn aufgrund von Kosteneinschränkungen eine doppellagige Leiterplatte verwendet werden muss, sollte für die Signale innerhalb der Leiterplatte eine relativ integrierte Massefläche entworfen werden. In der praktischen Anwendung wird die Masseimpedanz der Leiterplatte sowohl von ihrer Form als auch von Signaldurchkontaktierungen, Rissen und Schlitzen beeinflusst. Abbildung 3a und 3b zeigen jeweils ein schlechtes und ein hervorragendes Design einer Massefläche mit niedriger Impedanz.

In dieser Abbildung befinden sich alle Komponenten auf der Vorderseite der Leiterplatte, während die Massefläche auf der Rückseite liegt. Die Chips sind über Leiterbahnen verbunden.aban der Vorderseitecdwird auf der Rückseite Zeilen gedruckt. Unter dem Einfluss hochfrequenter Gleichtaktstörungen von außen wird der durchcdwird zur Zunahme von führenZGNDRückfluss gedruckter Zeilen.ZGNDschwankt im Prozess der Signalübertragung, was zu einer niedrigen Signalqualität führt. Daher werden Schichten gedruckter Leiterbahnen zwischencdkann im Verlauf des PCB-Layout-Designs immer wieder über Durchkontaktierungen ausgetauscht werden, sodassZGNDwird verringert. Außerdem werden zwei ICSmit empfindlichen Signalen können so angeordnet werden, dass GND lokal zu einer relativ integrierten Massefläche wird, um sicherzustellen, dass das Signal im Prozess der Signalübertragung nicht gestört wird. Achten Sie darauf, dass Durchkontaktierungen nicht zu dicht angeordnet werden dürfen, da sonst auch Risse in der Massefläche verursacht werden, was zur Eskalation vonZGND.

Stacking-Design von Leiterplatten

Das EMC-Design eignet sich am besten für 4-lagige Leiterplatten. Aus Sicht der EMS sind entweder ein Metallgehäuse oder eine Metallschirmung lokal empfindlicher Schaltungen in der Lage, Störungsprobleme zu lösen. Aus Sicht der EMI kommt es manchmal vor, dass 4-lagige Leiterplatten die Anforderungen an die Begrenzung der Strahlungsabgabe nicht erfüllen und die Anzahl der Lagen erhöht werden muss, da mehrlagige Leiterplatten Signale mit hoher du/dtund dich/dtSorgen Sie während des Übertragungsvorgangs für eine kleinere Signalschleifenfläche und stellen Sie für Hochgeschwindigkeitssignale einen Rückfluss mit niedriger Impedanz bereit.

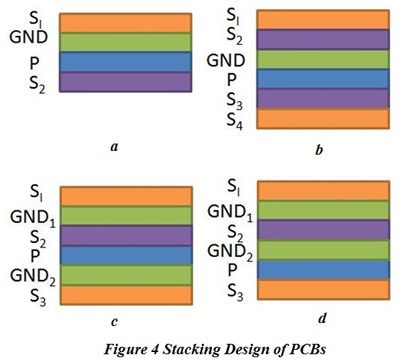

Das Grundprinzip vonPCB-Stacking-Designbesteht darin, die Hochgeschwindigkeitssignallage und die Versorgungsebene an die Masseebene angrenzend anzuordnen. Abbildung 4 zeigt das Stapeldesign von 4‑lagigen und 6‑lagigen Leiterplatten. S1in Abbildung 4a bezieht sich auf die Hochgeschwindigkeitssignallage, während Abbildung 4b, 4c und 4d drei gewöhnliche 6-lagige PCB-Designs darstellen.

Unter den drei 6-lagigen Leiterplattendesigns, Designbist das Schlimmste und S2Die Schicht sollte eine Hochgeschwindigkeitssignalschicht sein. S2Schicht im Designcunddist eine Hochgeschwindigkeitssignalleitung. Entwurfcist die beste, weil jede Signallage eng an die Massefläche angrenzt, um den kürzesten Signalrückflussweg und S sicherzustellen2und P-Schichten werden durch GND abgeschirmt1und GND2. Im Vergleich zum Designc, S3im Designdist weit von der GND-Schicht entfernt, und P kann aufgrund des Designs nur die einseitige Wirkung anstelle der beidseitigen Wirkung erreichenc.

Äquivalente Antenne in Leiterplatten

Die grundlegende Funktion einer Antenne besteht darin, drahtlose Funkwellen auszusenden und zu empfangen. Im Strahlungsprozess kann Hochfrequenzstrom in eine elektromagnetische Welle umgewandelt werden; im Empfangsprozess wird die elektromagnetische Welle in Hochfrequenzstrom umgewandelt. Die Strahlung im EMV-Bereich bezieht sich hauptsächlich auf die Fernfeldstrahlung. Die Bildung einer Antenne hängt von zwei grundlegenden Bedingungen ab: einer HF-Signalquelle und einer bestimmten Länge von Leitern, die mit der HF-Signalquelle verbunden sind. Im Ingenieurwesen geht man davon aus, dass ein Antenneneffekt auftritt, wenn die Leiterlänge der folgenden Formel entspricht, die lautetl=λ/20. Wennl=(λ/4)n, der Antenneneffekt ist am größten beinals natürliche Zahl.

Wenn ein Signal innerhalb einer Leiterplatte übertragen wird, hat eine innere Schleife denselben Effekt wie eine Schleifenantenne. Je größer die Schleifenfläche ist, desto stärker ist der Antenneneffekt. Eine strenge Kontrolle der Leiterplattenschleifen kann Gleichtaktstörungen wirksam unterbinden, was in der Praxis umsetzbar ist. Allerdings führt eine Vergrößerung der Leiterbahnlänge zu einem deutlichen Stabantenneneffekt, daher sollte die Länge der Verbindungssignale im Prozess des Leiterplattenlayouts so weit wie möglich reduziert werden.

Wenn relativ hochZGNDfindet auf dem Rückflussweg von hohem d stattu/dtSignale, die innerhalb der Leiterplatte übertragen werden, Gleichtakt-Treiberquelleucomwird stattfinden mitichcomvorbeifließendZGNDzusammen mit angeschlossenen Leiterbahnen oder I/O-Anschlüssen, die nach außen abstrahlen können.

Wenn Leiterplatten relativ klein sind, können die inneren Leiterbahnen aufgrund ihrer begrenzten Länge die Anforderungen an die Antennenabstrahlung nicht erfüllen. Unter dieser Bedingung können I/O-Kabel als Verlängerung der Leiterbahnen betrachtet werden, sodass die Abstrahlungsanforderungen erfüllt werden können. Selbst wenn keine direkte Verbindung zu einem I/O-Anschluss besteht, sollte das Übersprechen zwischen I/O-Kabeln unterbunden werden.

Übersprechen in Leiterplatten und seine Abhilfen

• Kopplung zwischen gedruckten Leiterbahnen auf der Leiterplatte und der Bezugserde

Da bei der EMV hauptsächlich hochfrequente Gleichtaktsignale betrachtet werden, lassen sich Verteilungsparameter weder innerhalb noch außerhalb der Leiterplatte (PCB) vermeiden. Zwischen der Leiterplatte und der Bezugserde tritt eine kapazitive Kopplung auf, deren verteilte Kapazität sich aus Plattenkapazität und natürlicher Kapazität im kleinstmöglichen Abstand zusammensetzt. Die Plattenkapazität ist direkt proportional zur Größe der Leiterplatte und umgekehrt proportional zum Abstand zwischen Leiterplatte und Erde. Die natürliche Kapazität im kleinstmöglichen Abstand ist direkt proportional zum äquivalenten Durchmesser der Leiterbahnen innerhalb der Leiterplatte. Daher existiert, unabhängig davon, wo die Leiterplatte platziert wird – selbst unendlich weit von der Erde entfernt – stets eine verteilte Kapazität zwischen den inneren Leiterbahnen und der Erde. In einer Leiterplatte beträgt die verteilte Kapazität einer relativ zusammenhängenden GND-Fläche zur Bezugsmasseplatte ungefähr 10 pF, und die verteilte Kapazität der inneren Leiterbahnen zur Bezugsmasseplatte liegt ungefähr im Bereich von 0,001 pF bis 0,1 pF oder darunter. Die verteilte Kapazität der Leiterbahnen in der Mitte der Leiterplatte ist deutlich geringer als die der Leiterbahnen am Rand der Leiterplatte.

• Kopplung innerhalb der Leiterplatte

a. Theorie der Kopplung innerhalb der Leiterplatte und ihr Einfluss auf das Signal

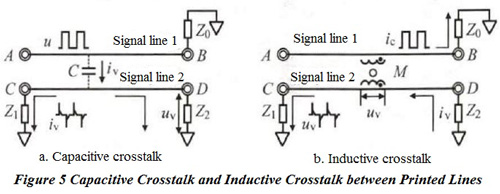

Die Kopplung innerhalb der Leiterplatte besteht aus kapazitiver Kopplung und induktiver Kopplung, deren Theorie in Abbildung 5 dargestellt ist.

In dieser Abbildung, beideABundCDsind parallele gedruckte Linien mit kleinem Abstand zwischen zwei Linien. Z0bezieht sich auf den Träger der Signalleitung 1, während Z1und Z2beziehen sich jeweils auf Träger der Signalleitung 2. In Abbildung 5a, wenn die Signalspitzenspannung auf der gedruckten LeitungABistu, die Anstiegszeit des Signals ist Δt und die Kreisfrequenz ist ω, die Spannung von Z2wirst du seinv=[Z1Z2/(Z1+Z2)]cΔu/Δt. Obwohlchat einen sehr niedrigen Wert, den Wert von Δu/dtkann sehr hoch sein, und ihr Produkt kann nicht vermieden werden. In Abbildung 5b, wenn der Spitzenstrom des Signals anABist ichc, die Anstiegszeit des Signals ist Δtund die Kreisfrequenz ist ω, die gegenseitige Induktivitätmzwischen 2 gedruckten Linien hindurchführenCDauf dem die induzierte Spannung U istv=mωic. Obwohl der Wert vonmist so klein, kann die Signalfrequenz erhöht werden. Daher kann ihr Produkt nicht vermieden werden.

Infolgedessen stehen sowohl die kapazitive Kopplung als auch die induktive Kopplung mit den verteilten Parametern der beiden Leiterbahnen in Zusammenhang.coderm. Während des PCB-Layouts werden Werte voncundmkann durch Vergrößerung des Abstands zwischen parallelen Leitungen verringert werden. In praktischen Schaltungen macht die kapazitive Kopplung den größten Teil der digitalen Schaltung aus, und wennLeiterplattenebeneWenn keine Glättung, Schlitze oder Risse vorhanden sind, wird das induktive Übersprechen einen größeren Einfluss haben als das kapazitive Übersprechen. Wenn jedoch die Fläche der Leiterplatte begrenzt ist, kann das Übersprechen nicht allein durch Vergrößerung des Abstands zwischen parallelen Leitungen behandelt werden. Um die kleinstmöglichen verteilten Parameter zwischen zwei benachbarten parallelen Leitungen beizubehalten, sollte im Projektionsbereich ein integriertes Flächendesign vorgesehen werden, und es ist am besten, wenn sich oben und unten Masseebenen befinden.

b. Einfluss des Schirm-Erdungsleiters auf die Reduzierung von Übersprechen

Der Grad des Übersprechens wird von vielen Faktoren bestimmt, wie z. B. der Signalfrequenz, der Anstiegszeit des Signals, dem Abstand zwischen den Signalleitungen, dem Treiberport und den elektrischen Eigenschaften des Empfangsports sowie der Anzahl der PCB-Lagen. Das Übersprechen kann verringert werden, indem eine durchgehende Massefläche unter den Leiterbahnen vorgesehen wird, und es kann eine abgeschirmte Masseleitung zwischen den Signalen hinzugefügt werden.

Im Prozess des PCB-Layouts können zwei Aspekte dazu beitragen, Übersprechen zu verhindern. Erstens sollten empfindliche innere Schaltungen und äußere Schaltungen getrennt werden. Zweitens sollte das Übersprechen zwischen inneren Schaltungen oder Rauschschaltungen und anderen Signalen unterbunden werden. Beim praktischen PCB-Layout sollten in derselben Lage oder zwischen verschiedenen Lagen der Leiterplatte detaillierte Tests durchgeführt werden, um festzustellen, ob ein Risiko für Übersprechen besteht oder nicht.

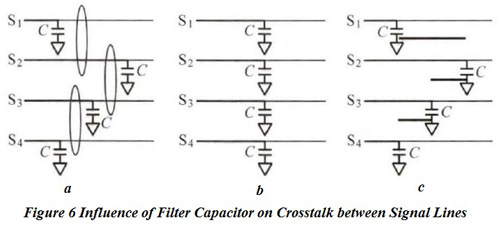

Während des PCB-Layout-Prozesses sollten einige Signalleitungen mit denselben Eigenschaften gleichzeitig, in derselben Richtung und mit gleicher Dichte geführt werden. Wenn die Begrenzung des PCB-Raums dazu führt, dass Filterkomponenten nicht in derselben Leitung platziert werden können, neigt dies dazu, Übersprechen zwischen den Signalen zu verursachen. Diese Situation ist in Abbildung 6 unten dargestellt.

c. Einfluss des Schirmerdungskabels auf den Randeffekt

Wenn hochsensible Signalleitungen oder Signalleitungen mit hoher du/dt, dich/dtsind entlang der Leiterplattenkante angeordnet, haben sie ein höheres EMV-Risiko als diejenigen, die in der Mitte der Leiterplatte angeordnet sind. Es ist für Signalleitungen am Rand leichter, aufgrund einer größeren parasitären Kapazität hochfrequente Störungen oder äußere Strahlung zu empfangen.

Aufgrund der begrenzten Leiterplattenfläche ist es äußerst schwierig, das PCB-Layout in der Designdatei nach dem 20H-Prinzip zu gestalten. „Packet“ kann verwendet werden, um Störungen und äußere Abstrahlung zu reduzieren. Packet-Leitungen müssen keine spezifischen Anforderungen wie Dicke und Form erfüllen. Üblicherweise kann, wenn eine Signalleitung zu nah am Rand der Leiterplatte liegt, um dort Kupfer aufzubringen, eine Masseleitung im Bereich von 7 bis 10 mil als Abschirmung hinzugefügt werden.

d. Gegenseitige Beeinflussung zwischen digitalen und analogen Schaltungen

Wenn eine Leiterplatte Hochgeschwindigkeits-Digitalschaltungen und niederpegelige analoge Signale enthält, wird bei schlechtem Leiterplattendesign in der Regel Übersprechen von digitalen Störungen auf die analogen Signale erzeugt. Die gegenseitige Beeinflussung zwischen digitalen und analogen Schaltungen wird durch die folgenden Gründe verursacht. Erstens wird Übersprechrauschen durch parasitäre Kapazitäten und parasitäre Induktivitäten verursacht. Zweitens führt eine schlechte Entkopplung der Versorgungsspannungswelligkeit und der Versorgung der Digitalchips zu Versorgungsrauschen. Drittens verursachen Erdungsimpedanz und die Anordnung der Systemmasse Rauschen. Das Problem des Rauschens sollte in der Reihenfolge Versorgung, Signal und Masse behandelt werden.

Hilfreiche Ressourcen:

•Die umfassendste Einführung in automatisierte EMI- und EMC‑Werkzeuge

•Sicherstellung eines erfolgreichen ersten Durchlaufs im PCB-EMV-Design

•Designregeln für die Leiterplattenpartitionierung zur Verbesserung der EMV

•Leiterplattendesign für Hochfrequenzschaltungen und elektromagnetische Verträglichkeit

•Drei Designaspekte zur Sicherstellung der EMV von Laptop‑Leiterplatten

•Umfassender Leiterplatten-Fertigungsservice von PCBCart – zahlreiche Mehrwertoptionen

•Fortschrittlicher Leiterplattenbestückungsservice von PCBCart – ab 1 Stück