Die grundlegendste Form des fertigungsgerechten Designs, wie sie auf Leiterplatten (PCBs) angewendet wird, ist die Verwendung von Designregeln und Designregelprüfungen in PCB-Designsoftware. Die Designregelprüfung (DRC) ist der Prozess, bei dem ein Design daraufhin überprüft wird, ob es den Fertigungsmöglichkeiten einesLeiterplattenherstellerTypischerweise erhält der Designer die höchsten Toleranzen, die ein Leiterplattenhersteller unterstützt, vom Hersteller, lädt diese Toleranzen in sein Designprogramm und führt dann einen Designregeltest für sein geplantes Design durch. Designregelprüfungen sind üblicherweise in Leiterplattendesign-Software integriert und werden normalerweise nicht als Zusatzdienstleistung betrachtet. Fortgeschrittenere Software zur Analyse der fertigungsgerechten Konstruktion ist ebenfalls verfügbar, um nach komplexeren und weniger offensichtlichen Konstruktionsfehlern zu suchen. TypischerweiseDFM-Softwareprüfungwird von Leiterplattenherstellern den Kunden als zusätzlicher Service angeboten. Der Grund für diese Unterscheidung liegt in den zusätzlichen Kosten für hochwertige DFM-Software und der zusätzlichen Schulung, die für deren Nutzung erforderlich ist.

1. Ausgehungerte Thermik

Starved Thermals treten auf, wenn die mit einer Pad verbundenen Thermal-Relief-Leitungen nicht ordnungsgemäß mit der zugehörigen Kupferfläche verbunden sind. Häufig besteht zwar der Abstand zwischen den Vias eine grundlegende Designregelprüfung, aber die angeschlossenen Thermal-Relief-Leitungen werden unterbrochen und die betroffenen Vias werden unangemessen von ihren zugewiesenen Kupferflächen isoliert. Dieses Problem tritt am häufigsten auf, wenn mehrere Vias in unmittelbarer Nähe zueinander platziert werden.

2. Säurefallen

Wenn zwei Leiterbahnen in einem sehr spitzen Winkel zusammengeführt werden, kann es passieren, dass die zum Entfernen des Kupfers von der Rohplatine verwendete Ätzlösung an diesen Verbindungsstellen „gefangen“ wird. Diese Falle wird allgemein als Säurefalle bezeichnet. Säurefallen können dazu führen, dass Leiterbahnen von ihren zugewiesenen Netzen getrennt werden und diese Leiterbahnen offen bleiben. Das Problem der Säurefallen wurde in den letzten Jahren dadurch verringert, dass Hersteller auf photoaktivierte Ätzlösungen umgestiegen sind. Es ist also weiterhin ratsam, darauf zu achten, dass Ihre Leiterbahnen keine spitzen Winkel bilden, aber das Problem ist heute weniger gravierend als früher.

3. Silbers

Wenn sehr kleine Bereiche einer Kupferfläche nur durch eine schmale Leiterbahn mit größeren Bereichen derselben Kupferfläche verbunden sind, kann es während der Fertigung passieren, dass sie abbrechen, auf andere Teile der Leiterplatte „wandern“ und unbeabsichtigte Kurzschlüsse verursachen. Die durch Silvers verursachten Probleme wurden in den letzten Jahren dadurch verringert, dass Hersteller auf photoaktivierte Ätzlösungen umgestiegen sind. Obwohl Silvers in Designs weiterhin vermieden werden sollten, stellen sie heute nicht mehr ein so großes Problem dar wie früher.

4. Unzureichender Ringdurchmesser

Vias werden hergestellt, indem durch Pads auf beiden Seiten einer Leiterplatte gebohrt und die Wände dieser Löcher beschichtet werden, um die beiden Seiten der Leiterplatte zu verbinden. Wenn die im Design angegebene Padgröße zu klein ist, kann das Via ausfallen, da das Bohrloch einen zu großen Teil der Pads einnimmt. Die minimale Breite des Ringes (Annular Ring) ist üblicherweise Teil des DRC-Prozesses. Dieses Problem wird hier erwähnt, da es nicht selten vorkommt, dass Bohrungen verfehlt werden beiPrototyping-Platinen.

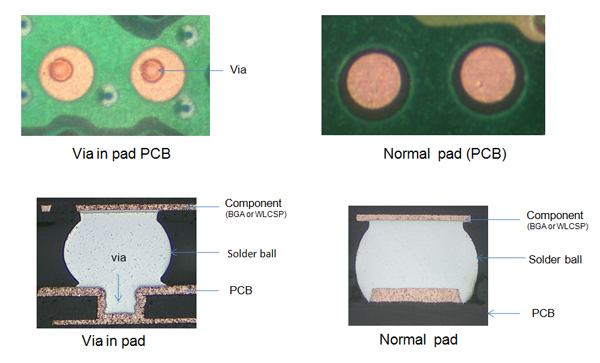

5. Via in Pads

Gelegentlich kann es praktisch sein, eine Via so zu gestalten, dass sie sich innerhalb eines PCB-Pads befindet. Allerdings können Vias in Pads Probleme verursachen, wenn die Leiterplatte bestückt wird. Die Via zieht Lötzinn vom Pad ab und führt dazu, dass das mit dem Pad verbundene Bauteil nicht richtig montiert wird.

Das Bild unten zeigt den Unterschied zwischenüber in PadPCB und normales PCB.

6. Kupfer zu nah am Rand der Leiterplatte

Normalerweise wird dies während der Designregelprüfungen erkannt: Wenn Kupferschichten zu nah am Rand einer Leiterplatte platziert werden, können diese Schichten beim Zuschneiden der Platte während des Fertigungsprozesses miteinander kurzgeschlossen werden. Solche Fehler sollten in der Regel durch die inPCB-Design-SoftwareEin Leiterplattenhersteller, der eine DFM-Prüfung durchführt, wird dieses Problem ebenfalls erkennen.

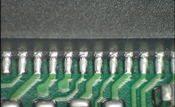

7. Fehlende Lötstoppmaske zwischen den Pads

Bei sehr eng beieinander liegenden Bauteilen mit kleinem Pin-Abstand ist es aufgrund der standardmäßigen Designeinstellungen durchaus üblich, dass sich zwischen den Pins keine Lötstoppmaske befindet. Das Fehlen dieser Lötstoppmaske kann dazu führen, dass beim Anbringen des fein gepitchten Bauteils auf die Leiterplatte während der Montage leichter Lötbrücken entstehen.

Wir haben bereitgestelltprofessionelle LeiterplattenbestückungsdiensteSeit Jahren sind wir in der Lage, das Fehlen von Lötstopplack zwischen den Pads zu vermeiden. Das untenstehende Bild zeigt unseren hochpräzisen Lötstopplack zwischen 0,4-mm-Raster-QFN-Pads.

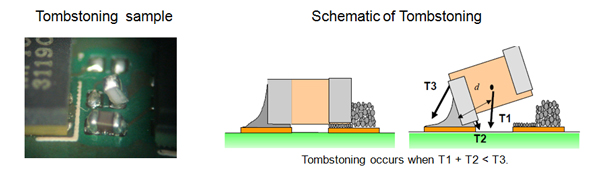

8. Tombstoning

Wenn kleine passive oberflächenmontierte Bauteile mittels Reflow-Lötverfahren auf eine Leiterplattenbaugruppe gelötet werden, kommt es häufig vor, dass sie sich an einem Ende anheben und „tombstonen“. Tombstoning kann die Ausbeute von Leiterplatten erheblich beeinträchtigen und die Produktionskosten schnell in die Höhe treiben. Die Ursache für Tombstoning können fehlerhafte Lötpad-Layouts und ein unausgewogener thermischer Ausgleich an den Pads des Bauteils sein. Tombstoning kann durch den Einsatz von DFM-Prüfungen wirksam verhindert werden.

Das folgende Bild zeigt ein Beispiel für Tombstoning und dessen Schaltplan.

Haben Sie eine PCB-Design-Datei zur Hand? PCBCart kümmert sich um Ihre Leiterplattenfertigung!