Hochdichte Verbindungstechnologie (HDI) Leiterplatten sind für leistungsstarke und miniaturisierte Elektronik konzipiert und haben sich zum Arbeitspferd in allem entwickelt – von Smartphones bis hin zu komplexen Luft- und Raumfahrtsystemen. Im Kern vonHDI-LeiterplatteDie Leistungsfähigkeit hängt von der Präzision der Microvias ab – jener winzigen, lasergebohrten Löcher, die in dichten Designs eine zuverlässige Verbindung von Lage zu Lage ermöglichen. Darüber hinaus erfordert das Ausschöpfen des vollen Potenzials von HDI-Leiterplatten zur Sicherstellung überlegener elektrischer Leistung, struktureller Integrität und Herstellbarkeit die Optimierung von drei entscheidenden Prozessen: Microvia-Bohrung, Kupferbeschichtung und -füllung. Dieser Artikel beginnt damit, umsetzbare Strategien zur Verfeinerung jedes Schrittes zu erörtern, indem er auf Industriestandards, fortschrittliche Techniken und bewährte Verfahren aus der Leiterplattenfertigung zurückgreift.

1. Optimierung des Microvia-Bohrens: Präzision, Materialkompatibilität und Defektvermeidung

Das Bohren von Microvias bildet im Grunde die Grundlage des HDI‑Leiterplattendesigns. Bereits geringfügige Unstimmigkeiten in diesem Prozess können die nachfolgenden Beschichtungs- und Füllprozesse beeinträchtigen. Um die bestmögliche Leistung zu erzielen, sollten sich HDI‑Leiterplattenfertigungen durch Präzision, sorgfältige Materialauswahl und strikte Einhaltung von Normen auszeichnen.

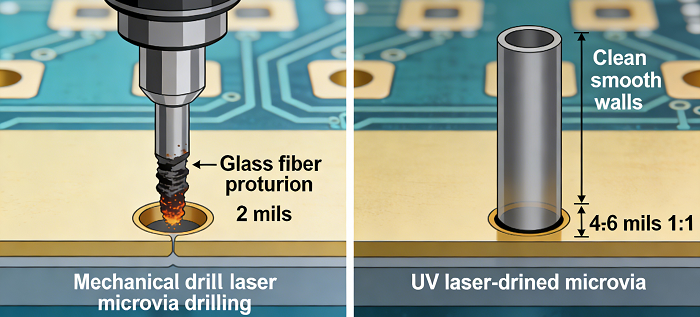

Definieren Sie Microvias bisIPC-SpezifikationDas typische Microvia, wie von der IPC definiert, weist ein Aspektverhältnis von 1:1 auf, eine maximale Tiefe von 0,25 mm (0,010 Zoll), und sein Durchmesser liegt zwischen 4 und 6 mil. Ein Aspektverhältnis größer als 1:1 erhöht die Wahrscheinlichkeit von Zuverlässigkeitsproblemen wie nicht gleichmäßiger Beschichtung oder Rissen im Hohlraum; daher ist für Hochzuverlässigkeitsanwendungen ein konservativeres Aspektverhältnis von ≤0,8:1 wünschenswert. Die bevorzugte Methode zur Herstellung von Microvias umfasstLaserbohrenEs erreicht eine Genauigkeit von bis zu 99,3 %, die von mechanischem Bohren nicht übertroffen wird. Bei sehr kleinen Durchmessern und dünnen Dielektrikschichten bleibt das Laserbohren unübertroffen. Fortschrittliche Lasersysteme minimieren Schäden durch Wärmeeinwirkung und verringern Harzverschmierung sowie Glasfaserüberstand. Dadurch treten Defekte bei diesen beiden häufigen Problemen seltener auf, was die Haftung der Beschichtung beeinträchtigen kann.

Der Erfolg bei der Bohrbarkeit beginnt mit der Materialauswahl: Wählen Sie nur lasertaugliche dielektrische Materialien mit flachen oder verteilten Glasstrukturen. Beispiele sind ein hochwertiges Harzsystem, das speziell für den Einsatz beim Laserbohren entwickelt wurde, oder nicht verstärkte Aufbaufolien. Diese ermöglichen eine gleichmäßige Laserablation, um ungleichmäßige Via-Konizität und das Verkohlen des Materials zu verhindern. Materialien mit nicht übereinstimmenden Wärmeausdehnungskoeffizienten sollten vermieden werden, da sie während des Bohrprozesses zu einer Fehlregistrierung zwischen Capture-Pad und Zielpad führen können. Stellen Sie außerdem die Homogenität des Aufbaus sicher – das Mischen von Materialien mit unterschiedlichen Laserenergie-Absorptionsraten führt zu inkonsistenter Bohrqualität. Harzreiche oder Glasgewebe mit niedriger Oberflächenrauheit (1035, 1067, 1086) ermöglichen eine bessere Ablationsgleichmäßigkeit und minimales Schmieren.

Dem Vorbohren und der Reinigung nach dem Bohren sollte die gleiche Bedeutung beigemessen werden. Substratoberflächen dürfen keine Verunreinigungen aufweisen, um ein Verlaufen des Bohrers zu vermeiden. Sobald das Bohren abgeschlossen ist, müssen nach einer geeigneten Plasmaätzung oder einem speziellen Reinigungsverfahren Harzverschmierungen und Rückstände entfernt werden, insbesondere bei 2-HDI-Leiterplatten und komplexen 6-Lagen-Designs. Dieser Prozess beseitigt jede Barriere für die Kupferhaftung und verringert das Risiko der Hohlraumbildung in den nachfolgenden Beschichtungsprozessen.

2. Optimierung der Kupferbeschichtung: Homogenität, Haftung und Rel

Die Kupferbeschichtung ist ein Verfahren, das bei Mikrovia‑Verbindungen eingesetzt wird. Die Qualität des Kupferbeschichtungsprozesses beeinflusst sowohl die Signalintegrität als auch die Robustheit der Verbindungen. Der Kupferbeschichtungsprozess muss durch die richtige Kombination von Kupferbeschichtungsmethoden, Parametern und Fertigung optimiert werden.

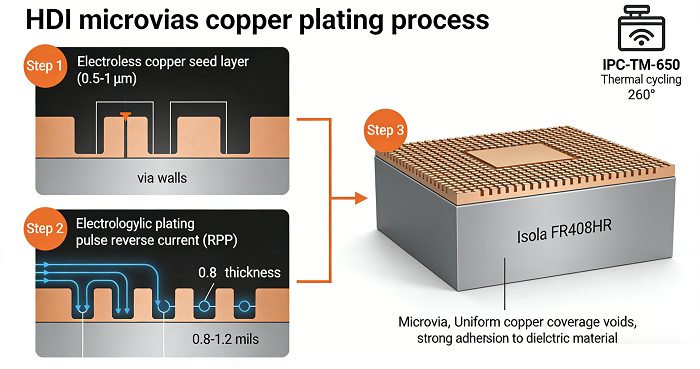

Beginnen Sie mit einer soliden Vorgrundlage—stromlose KupferbeschichtungDiese Technologie erzeugt eine dünne, gleichmäßige Schicht, üblicherweise 0,3 bis 0,6 mil, an den Lochwänden für eine vollständige Abdeckung von Microvias. Eine effektive Vorbereitung für die Beschichtung ist für eine gute Haftung von größter Bedeutung; andernfalls kann sich die Beschichtung bei vorhandenen Verunreinigungen an den Lochwänden leicht ablösen.

Wählen Sie das geeignete Galvanisierungsverfahren entsprechend den Konstruktionsanforderungen aus:

· Wrap-BeschichtungDiese Art der Beschichtung, die optimal eingesetzt wird, um eine verbesserte Interkonnektivität zwischen den Lagen zu gewährleisten, überzieht die Seiten der Vias mit Kupfer und verlängert das Kupfer in die Oberflächenpads. Dies führt zu hoher mechanischer Festigkeit, erfordert jedoch Präzision, um eine übermäßige Kupferabscheidung zu verhindern, die die Platzierung von Fine-Pitch-Bauteilen beeinträchtigen kann.

· Button (Spot)-BeschichtungDas Verfahren begünstigt die Abscheidung von Kupfer in Form von Durchkontaktierungsbohrungen und Pads und verringert die insgesamt auf der Oberfläche der Leiterplatte vorhandene Kupfermenge. Es ist sehr nützlich bei Leiterplattendesigns, bei denen eine effektive Kontrolle über die Wandstärke der Durchkontaktierungsbohrung erforderlich ist.

· Puls-/Reverse-Puls-Galvanisierung (RPP) vs. Gleichstrom-Galvanisierung (DC):RPP-Beschichtung, die im Vergleich zur DC-Beschichtung eine verbesserte Kupferverteilung bietet, verbessert die Kupferverteilung, was bei Leiterplatten mit dicken Substraten und gestapelten MicroVia-Strukturen noch wichtiger wird. RPP verhindert das Verstopfen von Pasten in den Löchern.

Prozessparameter können optimiert werden, um potenzielle Probleme wie inhomogene Abscheidung zu minimieren. Stromdichte (verringert für eine glattere Abscheidung, aber erhöht für eine höhere Produktionsrate), Rührgeschwindigkeit (unterstützt eine gleichmäßige Verteilung der Lösung) und Temperatur können gesteuert werden. Der Beschichtungsprozess sollte halbautomatische oder automatische Beschichtungsanlagen mit Submikrometer-Präzision (±0,1 µm) umfassen. Die Kupferdicke sollte idealerweise zwischen 0,8 und 1,2 mil liegen, was einen idealen Kompromiss zwischen Leitfähigkeit und Herstellbarkeit darstellt. Zusätzlich sollten Anoden und Beschichtungszusätze, wie Nivelliermittel, von guter Qualität sein, um Verunreinigungen zu minimieren und die Oberfläche zu glätten.

IPC-Spezifikationen sollten für die Zuverlässigkeit der Beschichtung befolgt werden. Stellen Sie sicher, dass die Zielpadgröße mindestens 80 % der Via-Größe beträgt, um Spannungskonzentrationen zu vermeiden, und dass es keinen Abstand zwischen demLötstoppmaskeund Microvias, um das Hochziehen des Lots während des Reflow-Lötens zu vermeiden. Überwachen Sie den Widerstandstest nach dem Thermozyklustest gemäß den Spezifikationen von IPC-TM-650 2.6.27, wobei die Änderung des maximal zulässigen Widerstands 5 % nicht überschreiten darf.

3. Optimierung der Füllung von Microvias in Leiterplatten durch Ebenheit

Mikrovias-Füllungbeseitigt Hohlräume, verbessert die mechanische Robustheit und ermöglicht Planarität für Komponenten wieBGAsOb Mikrovias mit Kupfer oder Harzen gefüllt oder vermieden werden sollen, hängt von ihrer Verwendung und Art ab, aber die Optimierung liegt in der Anwendung von Techniken, die auf Planarität, Defektreduzierung und Konvergenz mit den Designanforderungen abzielen.

Schritt 1: Bestimmen Sie zunächst die Art der Füllung, die

· Gefüllte Microvias: Via-in-PadVergrabene und blinde Microvias müssen gefüllt werden. Eine Kupferfüllung ist notwendig, um Hohlräume unter dem Kupfer zu vermeiden, die während des Reflow-Lötzyklus zu Spannungskonzentrationen führen. Das Füllen mit Harz verringert jedoch die Signallaufzeit und erhöht die Planarität. Die Verarbeitung umfasst das Aufbringen einer Schicht konformer Beschichtung über die Microvias, gefolgt von einer gepulsten Kupferschicht.

· Ungefüllte Microvias:verwendbar in nicht-kritischenBlind Viaswerden nicht in Bauteilpads verwendet, aber in modernen Hochzuverlässigkeitsdesigns wurden sie nahezu vollständig eliminiert.

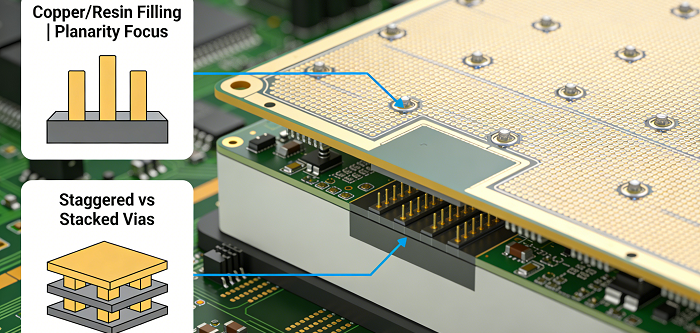

Betonung der Ebenheit für verbesserte Designs. Unvollständiges Füllen führt zu Vertiefungen, die sich nachteilig auf die Qualität der Lötverbindung bei feineren Leiterbahnabständen auswirken können. Semi-additive Prozesse, wie beispielsweise mSAP, basieren auf der Verwendung von Kupferfolie, um die für gestapelte Vias und Via-in-Pad-Designs erforderliche Ebenheit bereitzustellen. Die Planarisierung der Leiterplatte nach dem Füllen sorgt für die notwendige Ebenheit, deren Fehlen Lötperlendefekte in BGA-Gehäusen verursacht.

Bewältigen Sie Füllherausforderungen, indem Sie Prozesse optimieren und Technologie nutzen. Setzen Sie Simulationssoftware ein, um Konizitätsprobleme zu simulieren und zu verringern, indem Sie die Kathodengröße optimieren und unterschiedliche Schichtdicken einsetzen, um die Konizität um bis zu 40 % zu reduzieren. Um die Füllung in lasergebohrten Löchern zu verbessern, beheben Sie durch Erwärmung verursachte Schäden, indem Sie vor dem Füllen eine Lochreinigung vornehmen, da Asche in den Löchern die Füllung verhindert. Verwenden Sie neue Beschichtungslösungen und -anlagen, um Füllraten mit geringerem Aufwand und geringeren Kosten zu optimieren.

Balancieren Sie die Flexibilität im Design sorgfältig mit den anfallenden Implementierungskosten. Gestaffelte Microvias sind in der Befüllung kostengünstiger als gestapelte Vias und bieten zudem eine höhere Robustheit gegenüber thermischer Belastung. Stapeln Sie in der Microvia-Struktur nicht mehr als zwei Lagen; für mehr als zwei wird empfohlen, eine Staffelung zu verwenden. Wenn ausreichend Platz vorhanden ist, werden übersprungene Vias, die mechanisch gebohrt werden, zu einer kostengünstigen Alternative zu lasergebohrten, gestapelten Vias für Mehrlagenverbindungen.

Fazit

Die Optimierung des Bohrens von Microvias, der Kupferbeschichtung und des Füllens ist eine integrierte und sorgfältige Aufgabe, die große Aufmerksamkeit für Material, Prozess und Industriestandards erfordert. Die Nutzung der Möglichkeiten des Laserbohrens, des Pulsplattierens und des selektiven Füllens ermöglicht die Herstellung von HDI-Leiterplatten, die in der Lage sind, die Miniaturisierung und Funktionalität der Elektronik der nächsten Generation zu bewältigen. Die strikte Einhaltung von Standards wie IPC-T-50M und IPC-2226 stellt sicher, dass alle Designs nicht nur herstellbar, sondern auch zuverlässig und frei von Defekten sind. Die Prozessüberwachung vom Bohren bis zum Reflow-Löten ermöglicht die Korrektur inhärenter und potenziell unbemerkter Fertigungsfehler und gewährleistet so die optimale Funktionalität der resultierenden HDI-Leiterplatten.

Hilfreiche Ressourcen

•3 Schlüssel zur Entwicklung einer erfolgreichen HDI-Leiterplatte

•Faktoren, die die Qualität der BGA-Montage beeinflussen

•Lösung von Signalintegritätsproblemen in HDI-Leiterplatten

•Abnahmekriterien gemäß IPC-A-600 in der Leiterplattenfertigung

•Häufige Defekte in der Leiterplattenbestückung und wie man sie verhindert