Con la creciente complejidad del diseño de PCB, el suministro de energía estable y confiable se ha convertido en una nueva tendencia de investigación sobrediseño de PCB de alta velocidad. Especialmente cuando el número de componentes de conmutación sigue mejorando constantemente y el Vcore disminuye de forma continua, la fluctuación de la energía tiende a ejercer una influencia mortal sobre el sistema. Por lo tanto, mantener la estabilidad del sistema de alimentación se ha convertido en un punto clave en el diseño de PCB de alta velocidad.

Sin embargo, como resultado de la existencia de la impedancia del sistema de potencia, la corriente transitoria de carga genera una caída de tensión relativamente grande en dicha impedancia, lo que conduce a la inestabilidad del sistema. Para garantizar que se suministre energía normal a cada componente desde el principio hasta el final, es necesario controlar la impedancia en el sistema de potencia, lo que significa que dicha impedancia debe reducirse tanto como sea posible.

La aplicación de condensadores de desacoplo es una forma eficaz de suprimir la impedancia en el sistema de alimentación. Este artículo analiza las razones de la supresión de impedancia en el sistema de alimentación mediante condensadores de desacoplo y enumera métodos en cuanto a la selección de dichos condensadores. Además, investiga principalmente cómo determinar la posición del condensador de desacoplo basándose en el análisis armónico para maximizar la supresión de la impedancia en el sistema de alimentación.

Análisis de impedancia

La alimentación y la tierra pueden considerarse como un gran condensador de placas cuya capacidad se calcula según la fórmulaC=kAr/d

En esta fórmula,kes 0,2249 pulgadas;Ase refiere al área paralela entre dos planos;rse refiere a la constante dieléctrica del medio y es 4,5 para el material de placa FR4 de uso común;dse refiere a la distancia entre la alimentación y tierra. Se toma como ejemplo una PCB con un tamaño de 2x1 pulgadas. La capacitancia del condensador formado por la alimentación y tierra con un área paralela de 20 mils es aproximadamente 0,2249x4,5x2x1/0,02 = 101,2 pF. Con base en esta fórmula, se puede indicar que la capacitancia de desacoplo en el sistema de alimentación es tan pequeña que la impedancia correspondiente será muy grande, generalmente de un par de ohmios. Por lo tanto, está muy lejos de ser suficiente para disminuir la impedancia mediante el auto-desacoplo en el sistema de alimentación.

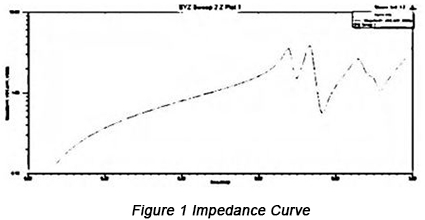

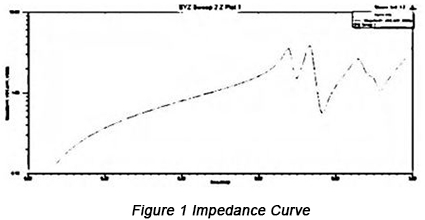

Se utiliza una herramienta de simulación SIWAVE a un nivel de 2.5D para realizar la simulación de impedancia en el dispositivo activo. Se selecciona la red de alimentación y tierra U41 para calcular los parámetros XYZ con un barrido de 0 a 1 GHz, a través del cual se obtiene una curva de impedancia que se muestra en la Figura 1 a continuación.

En el diagrama se puede observar que la curva de impedancia cambia con la variación de la frecuencia y que la impedancia cambia considerablemente en los puntos de inflexión en los valores de 670 MHz, 730 MHz y 870 MHz.

Métodos de prohibición

• Análisis teórico sobre la prohibición de impedancia mediante condensador de desacoplo

Dado que es imposible reducir la impedancia mediante el desacoplo de la propia alimentación, es necesario aplicar un condensador de desacoplo para limitar la impedancia.

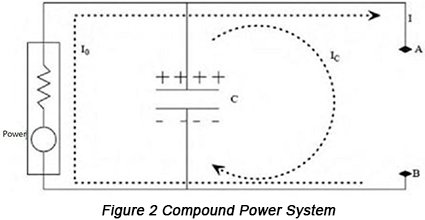

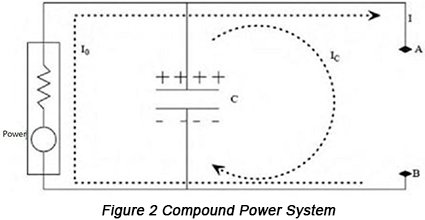

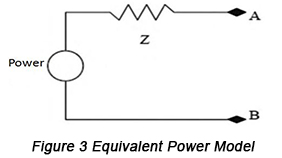

La Figura 2 es un diagrama del sistema de potencia compuesto. La Figura 3 indica este sistema de potencia en un modelo de potencia equivalente.

Se puede aplicar una fórmula para representar este circuito:V=ZxL. Debe lograrse una circunstancia en la que, incluso si la corriente transitoria de carga mantiene un gran cambio entre el punto A y el punto B, la variación de voltaje tenga que ser muy pequeña entre los dos puntos. Con base en la fórmula, este objetivo nunca puede alcanzarse a menos que el valor de la impedancia (Z) es suficientemente pequeño. En la Figura 3, la aplicación del condensador de desacoplo es útil para la implementación de este objetivo, por lo que se puede indicar que el condensador de desacoplo es capaz de disminuir la impedancia en el sistema de potencia desde la perspectiva de la equivalencia. Además, desde la perspectiva de los principios de los circuitos, se puede mantener la misma conclusión. El condensador presenta baja impedancia frente a señales de corriente alterna. Como resultado, la participación del condensador seguramente reduce la impedancia de corriente alterna en el sistema de potencia.

• Selección de la capacitancia del condensador de desacoplo

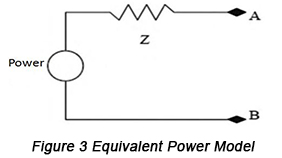

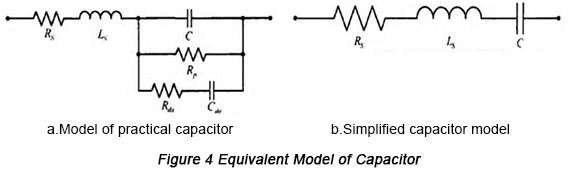

Nunca existe un condensador ideal, siempre presenta parámetros parásitos. La mayor influencia en el rendimiento de alta frecuencia del condensador proviene de la ESR (Resistencia Serie Efectiva) y la ESL (Inductancia Serie Efectiva). La Figura 4 muestra el modelo equivalente teniendo en cuenta los parámetros parásitos.

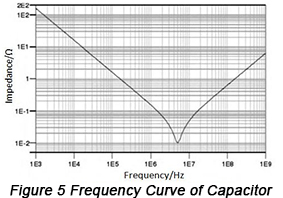

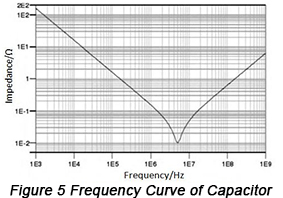

El condensador también puede considerarse como un circuito armónico en serie, cuya frecuencia armónica en serie sigue la fórmula:f=1/2PIFC. Cuando se mantiene en una circunstancia de baja frecuencia, muestra capacitancia. Sin embargo, cuando la frecuencia aumenta, muestra constantemente su inductancia. Dicho de otro modo, su impedancia aumentará primero y luego disminuirá con la escalada de la frecuencia, y el valor mínimo de la impedancia equivalente tiene lugar en la frecuencia armónica en serie.f0. En este momento, la reactancia capacitiva y la reactancia inductiva se compensan correctamente, mostrando la equivalencia entre el valor de la impedancia y el ESR con la menor resistencia equivalente del condensador. La curva de frecuencia del condensador se muestra en la Figura 5.

Por lo tanto, en el proceso de selección de condensadores, el punto de frecuencia armónica del condensador elegido se sitúa adyacente al punto de frecuencia que sufrirá el desacoplo. Su rendimiento capacitivo debe aprovecharse y utilizarse plenamente antes de la frecuencia de auto-resonancia siempre que sea posible.

En la siguiente tabla se muestran diferentes condensadores con distintas capacitancias, compatibles con diferentes frecuencias armónicas propias.

|

Capacitancia

|

DIP (MHz)

|

STM (MHz)

|

| 1,0μF |

2,5 |

5 |

| 0,1 μF |

8 |

16 |

| 0,01 μF |

25 |

50 |

| 1000pF |

ochenta |

160 |

| 100pF |

250 |

500 |

| 10pF |

ochocientos |

1,6(GHz) |

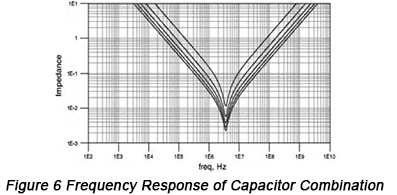

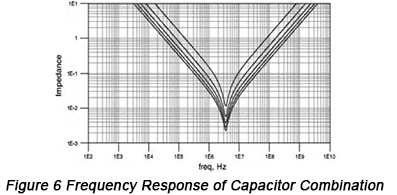

Generalmente, se requiere aplicar las propiedades armónicas del condensador de desacoplo y se obtiene la impedancia de entrada más baja mediante la combinación en paralelo de condensadores. La respuesta en frecuencia en paralelo del mismo tipo de condensadores se ilustra en la Figura 6 a continuación.

Basado en este método, el ESR y el ESL equivalentes pueden reducirse en gran medida. Para múltiples condensadores (n) con la misma capacitancia, la capacitancia equivalente C se convierte en nC después de la combinación, mientras que la inductancia equivalenteLse convierteL/n, la ESR equivalente se convierte en R/n. Sin embargo, la frecuencia armónica permanece sin cambios. Se puede ver que, dado que las frecuencias armónicas propias son las mismas para diferentes tipos de condensadores, cuanto mayor sea el número de condensadores en paralelo, menor será la impedancia en las zonas capacitiva e inductiva, manteniéndose inalterado el punto de frecuencia armónica propia.

En conclusión, en el proceso de selección de los condensadores de desacoplo, la frecuencia de desacoplo debe considerarse como el punto de frecuencia de auto-resonancia del desacoplo para poder elegir el condensador correspondiente. Además, la aplicación en paralelo de múltiples condensadores con la misma capacitancia es capaz de mejorar la capacidad de desacoplo y reducir la impedancia.

• Determinación de las posiciones de los condensadores de desacoplo

Después de la selección de los condensadores de desacoplo, es necesario tener en cuenta sus posiciones. El plano de alimentación y el plano de tierra pueden considerarse como una red compuesta por múltiples inductores y condensadores o como una cavidad resonante. A cierta frecuencia, se produce la resonancia entre inductores y condensadores, lo que influye en la impedancia del sistema de alimentación. Con el aumento de la frecuencia, la impedancia cambia constantemente, especialmente cuando la resonancia en paralelo se mantiene notable; la impedancia también aumenta de forma considerable. Por lo tanto, se deben determinar las posiciones específicas de los condensadores de desacoplo junto con el análisis armónico de la PCB.

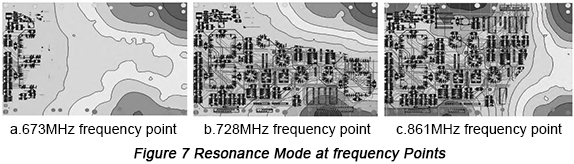

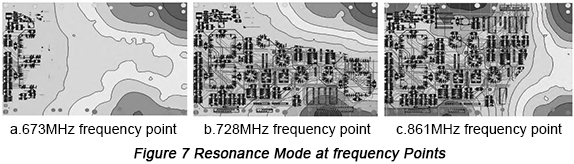

Con la función de análisis de resonancia aplicada de la herramienta de simulación SIWAVE, se obtienen parámetros equivalentes que incluyen resistencia, capacitancia e inductancia. Además, debe realizarse el análisis de resonancia de la PCB obteniendo el modo de resonancia en diferentes puntos de frecuencia, como se muestra en la Figura 7.

En combinación con la Figura 1, se puede observar que varios puntos de frecuencia con una impedancia relativamente alta son compatibles con los puntos de frecuencia en los que se genera la resonancia. Por lo tanto, con el resultado del análisis de resonancia, se puede concluir que en la zona con resonancia grave se deben colocar condensadores de desacoplo con una capacitancia adecuada para reducir la impedancia.

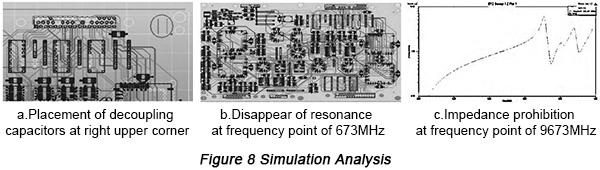

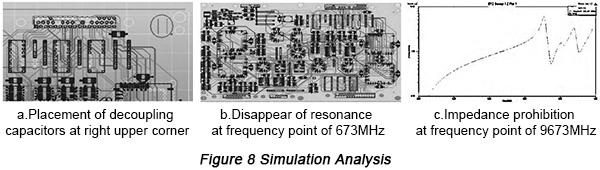

Tomando como ejemplo el punto de frecuencia de 673 MHz, se pueden colocar condensadores de desacoplo en paralelo de modo que la resonancia desaparezca y la impedancia correspondiente quede suprimida, como se muestra en la Figura 8.

Basándose en el análisis de resonancia de la PCB, se pueden determinar las posiciones correspondientes en las que tiene lugar la resonancia, en función de lo cual se colocan en paralelo condensadores de tamaño adecuado para impedir la impedancia.