PCB がショッピングカートに正常に追加されました

電子製品のEMC性能に対するPCBレイアウトの影響

・共通コード干渉がPCB内部信号に与える影響

プリント基板(PCB)の内部プリント配線は、基準グランド板に対して寄生パラメータを有しており、機能信号がPCB内部で伝送される際、回路内の同一ネットワークにおける同一等電位ノードは、もはや等電位ではなくなる。電流私PCB内部では、信号はソース端から出発し、一連のキャリアを通過して信号源へと戻り、信号を形成します。さらに、私その結果、インピーダンスの低い経路に沿って流れる傾向があるため私通常は、インピーダンスの安定性により不変に保たれます。

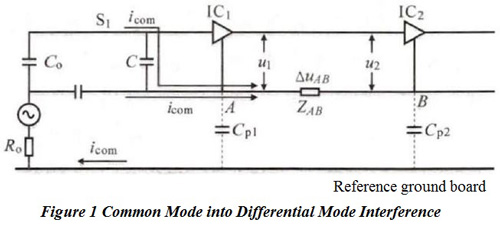

図1は、PCB内部でコモンモード干渉が差動モード干渉に変換される過程を示している。 私dPCB 内部を流れる差動モード電流を指し、一方で私コムPCBの外部から発生し、基準グラウンド板を通ってPCB内部へ流れ込む、またはPCB内部から発生し、基準グラウンド板を通ってPCB内部へ戻るコモンモード電流を指す。高周波私コム2つの経路があります。1つ目は、点からA指し示すBPCB の内部で GND から始まり、2 つ目はポイントからA指し示すBポートSから開始1コンデンサ C によって内部の PCB へ。グラウンドインピーダンスZABΔ の生成につながるuABしたがって、通常の信号がICに伝達されるとき2、変形が生じると信号に影響を与え、コモンモード干渉が差動モード干渉に変換され、その結果として、次の式に基づいて通常の信号に影響を及ぼす。u2=u1-ΔuAB.

したがって、~するとすぐに私コムI/Oポートまたは空間放射を通じてPCB内部に侵入した場合、PCBの信号ライン上の差動モードフィルタ容量は、干渉をGNDへバイパスして抑制することしかできない。この結果の前提条件は、GNDが信号の帰還電流に対して低インピーダンスと見なされ、電流は常に低インピーダンスの方向へ流れるということである。

・EMC設計実装の要点:PCBにおけるグラウンドインピーダンス

高周波信号によってEMCが発生する理由は、信号の基準レベルであるGNDが低インピーダンスという特性を維持できなくなることにある。インピーダンスの増加に伴いZGND基準レベルから離れると、信号伝送の品質も低下します。高周波干渉の問題を解決するために、一般的な方法が用いられておりEMC設計例えば、「グラウンド」と密接に接続されているフィルタ、グラウンド、およびシールドなど。

フィルタは、グランドに対するコンデンサとみなすことができ、その構成には2種類あり、1つはXコンデンサを信号リファレンスグランドに接続する方式、もう1つはYコンデンサやPCB内部の異なるグランド接続によって信号を金属シェルに接続する方式である。シールドは、PCBグランドが空間へ拡張された結果とみなすことができる。フィルタやシールドの目的は、高周波のコモンモード干渉が低インピーダンスのバイパスを通過するようにして、正常動作中の信号へ流れ込むのを防ぐことである。同様に、グランドが低インピーダンスでなければ、これらすべての手法は機能しない。

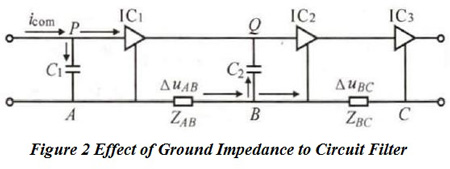

図2は、接地インピーダンスが回路フィルタに及ぼす影響を示している。 私コムICのシーケンスに従って流れる1→IC2→IC1そして、それが一点に流れ込むときP,私コムICの分岐回路に流れ込みます1そしてC1それが点から流れ出る経路AへB. もし、ある点間のインピーダンスがAそしてBつまりZABは、点間のインピーダンスに比べてはるかに小さいPおよびIC1この瞬間に私コム点から流れるPへA、IC1フィルタを実現することができる。いつ私コムポイントへの流れB、分岐回路が発生し、それらはB→CそしてB→Q. PCB レイアウトが適切に管理されていない場合、ポイント間のインピーダンスはBそしてCつまりZBC,ZBC>>ZC2+ZQ。ZQ点間のインピーダンスを指すQおよびIC2。私コムIC に逆流する2入力ポート経由C2もともとIC専用に使用されていた容量が2信号侵入干渉において役割を果たす。

低インピーダンスの基準レベルを実現するために、通常それは面として設計されます。一般的に言えば、長さと幅の比率が 5 未満の導体は、工学分野において低インピーダンスと見なすことができます。プリント配線のインピーダンスは、その長さや太さの程度によって決まるものではありません。従来のPCB設計の原則そのため、アナログ回路では単点接地が強く推奨されます。PCBレイアウトの原則デジタル回路の多点接地やデジタルモジュール回路と他回路の混合接地では、もはやEMC問題に対処することはできない。

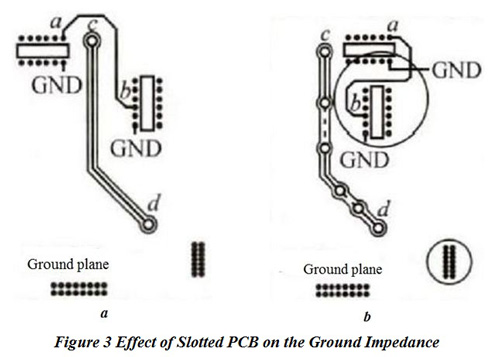

すべての信号のリターン電流が、低インピーダンスの一体化されたグラウンドを通ることを確保しなければならないため、一体型グラウンドプレーンを備えた4層または多層基板はこの要件を満たすことができるが、低コストの単層基板では不可能である。コストの制約から2層基板を使用しなければならない場合、PCB 内部の信号に対して、できるだけ一体化されたグラウンドプレーンを設計する必要がある。実際の応用において、PCB グラウンドのインピーダンスは、その形状だけでなく、信号配線のスルーホールやクラック、スロット加工によっても影響を受ける。図3aと図3bはそれぞれ、不適切な設計と優れた低インピーダンス・グラウンドプレーン設計の例を示している。

この図では、すべての部品がPCBの表面側にあり、グラウンドプレーンは裏面にあります。チップ同士はプリント配線によって接続されています。ab前面側でcd外側からの高周波コモンモード干渉の圧力を受けて、背面側に印刷されたラインは、スロット加工によって形成されるcd~の増加につながるZGND印刷された行の逆流。ZGND信号伝送の過程で変動し、その結果、信号の品質が低下する。したがって、印刷配線の層間でcdPCB レイアウト設計の過程でのスルーホールを介して何度も何度も交換することができるためZGND減少されます。さらに、2つのICS感度の高い信号を持つ配線はまとめて配置し、GND を局所的に比較的一体化したグラウンドプレーンとすることで、信号伝送の過程で信号が干渉を受けないようにします。スルーホールを高密度に配置してはならないことに注意してください。そうしないとグラウンドプレーンに亀裂が生じ、さらに悪化を招くことになります。ZGND。

PCBの積層設計

EMC設計は4層PCBに最適です。EMSの観点から見ると、金属シェルまたは局所的に感度の高い回路の金属シェルシールドのいずれも、干渉問題を解決することができます。EMIの観点から見ると、4層基板では放射エミッション制限の要件を満たせない場合があり、その場合は層数を増やす必要があります。多層基板は、高dを持つ信号を扱うことができるためです。u/dtそして d私/dt伝送過程において信号ループ面積を小さくし、高速信号のリターン電流に対して低インピーダンスの経路を提供する。

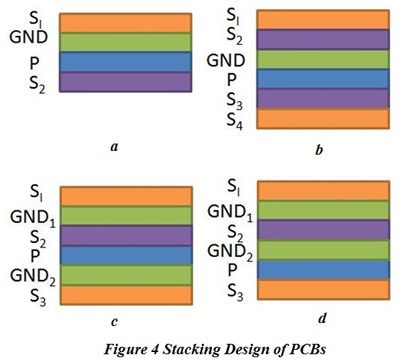

の基本原理PCBスタッキング設計は、高速信号層および電源プレーンをグラウンドプレーンに隣接して配置することです。図4に4層および6層基板のスタックアップ設計を示します。S1図4aは高速信号層を示し、図4b、図4cおよび図4dは3つの一般的な6層PCB設計を示している。

3つの6層PCB設計の中で、設計b最悪であり、Sです2レイヤーは高速信号レイヤーであるべきです。S2デザインにおけるレイヤーcそしてdは高速信号層です。設計c最も優れているのは、各信号層がグラウンドプレーンに密接して隣接しており、信号の最短のリターンパスとSを確保するためであるためです。2P層はGNDによってシールドされています1および GND2・設計と比較してc、S3デザイン中dGND層から遠く、設計上の理由により、Pは両面効果ではなく片面効果しか得られませんc。

PCB における等価アンテナ

アンテナの基本的な機能は、無線電波を放射および受信することである。放射の過程では、高周波電流が電磁波に変換され、受信の過程では、電磁波が高周波電流に変換される。EMC 分野における放射とは主に遠方界放射を指す。アンテナの形成は、RF 信号源と、その RF 信号源に接続されたある長さの導体という 2 つの基本条件に依存している。工学の分野では、導体の長さが次の式に従うとき、アンテナ効果が生じると考えられている。l=λ/20. のときl=(λ/4)n、アンテナ効果が最大となるのはn自然数として。

信号がPCB内部で伝送される際、内部ループはループアンテナと同じ効果を持ちます。ループ面積が大きいほどアンテナ効果は強くなります。厳密なPCBループ制御は、差動モード干渉を効果的に抑制でき、実務上も実現可能です。しかし、プリント配線の長さが長くなると顕著なロッドアンテナ効果を引き起こすため、PCBレイアウトの過程ではインターコネクト信号の長さを可能な限り短くする必要があります。

比較的高い場合ZGND高 d の逆流経路上で発生するu/dtPCB内部で伝送される信号、コモンモードドライバのソースuコムとともに行われます私コム流れ過ぎるZGND、および接続されたプリント配線や I/O ステーブルとともに、外部へ放射する可能性があります。

PCB のサイズが比較的小さい場合、長さの制約により内部プリント配線ではアンテナ放射要件を満たすことができません。このような条件では、I/O ケーブルはプリント配線の延長とみなすことができ、放射要件を満たすことが可能になります。I/O ケーブルに直接接続されていない場合でも、I/O ケーブル間のクロストーク結合は抑制しなければなりません。

PCB内部のクロストークとその対策

・PCBプリント配線と基準グラウンド間の結合

EMC は主に高周波のコモンモード信号を扱うため、PCB の内外において分布定数を避けることはできない。PCB と基準グラウンドとの間には容量結合が生じ、その分布容量は、最小空間内における平板容量と自然容量によって構成される。平板容量は PCB のサイズに正比例し、PCB とグラウンド間の距離に反比例する。最小空間内の自然容量は、PCB 内部のプリント配線の等価直径に正比例する。したがって、PCB がどこに配置されていても、たとえ無限遠のグラウンドから離れている場合であっても、内部プリント配線とグラウンドとの間には常に分布容量が存在する。PCB において、比較的一体化された GND プレーンと基準グラウンド板との分布容量はおよそ 10pF であり、内部プリント配線と基準グラウンド板との分布容量はおよそ 0.001pF から 0.1pF 程度、あるいはそれ以下の範囲となる。PCB 中央部のプリント配線の分布容量は、PCB の端部にあるプリント配線の分布容量よりもはるかに小さい。

・PCB 内部の結合

a. PCB内部の結合の理論とその信号への影響

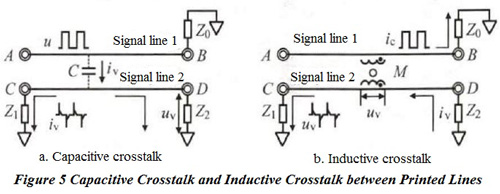

PCB 内部の結合には、図5に示す理論に基づく容量結合と誘導結合が含まれる。

この図では、両方ともABそしてCD2 本の線の間隔が狭く、平行に印刷された線です。Z0信号線1のキャリアを指し、一方 Z は1とZ2信号線2の搬送体をそれぞれ参照する。図5aにおいて、プリント線上の信号ピーク電圧がABはu信号の立ち上がり時間を Δt、角周波数を ω とすると、Z の電圧は2u になりますv=[Z1Z2/(Z1+Z2)]cΔu/Δtしかしc非常に低い値を持つため、Δ の値はu/dt非常に高くなる可能性があり、その生成物は回避できない。図5bでは、信号のピーク電流がABは私ですc、信号の立ち上がり時間は Δ ですt角周波数が ω であるとき、相互インダクタンスはm2本の印刷された線の間を通過しますCDその上に誘導される電圧は u ですv=mωic. の価値はしかしm非常に小さいため、信号周波数を高くすることができます。したがって、それらの積は避けることができません。

その結果、容量結合と誘導結合の両方が、2 本のプリント配線の分布定数と関連しているcまたはm. PCB レイアウト中、値はcとmは、平行線間の距離を大きくすることで低減できる。実際の回路では、容量性結合がデジタル回路の大部分を占めており、そしてPCBプレーン表面が滑らかでなく、スロットやクラックが存在しない場合、誘導性クロストークは容量性クロストークよりも大きな影響を及ぼします。しかし、PCB の面積が限られているときは、並走配線間の距離を広げるだけではクロストークに対処できません。隣接する 2 本の並走配線間の分布定数を最小に保つためには、投影領域内に一体化されたプレーン設計を配置し、上下にグラウンド層を設けるのが最善です。

b. シールド接地線によるクロストーク低減への影響

クロストークの程度は、信号周波数、信号の立ち上がり時間、信号線間の距離、ドライバポートおよび受信ポートの電気的特性、そしてPCB層数など、多くの要素によって決まります。クロストークは、プリント配線の下に一体型のグラウンドプレーンを設けたり、信号間にシールド用グラウンド線を追加したりすることで低減できます。

PCBレイアウトの過程では、クロストークを防止するために2つの側面が有効です。第一に、感度の高い内部回路と外部回路を分離する必要があります。第二に、内部回路またはノイズ回路と他の信号との間のクロストークを防止する必要があります。実際のPCBレイアウトにおいては、同一層内およびPCB内の異なる層間で詳細なテストを行い、クロストークのリスクが存在するかどうかを検出する必要があります。

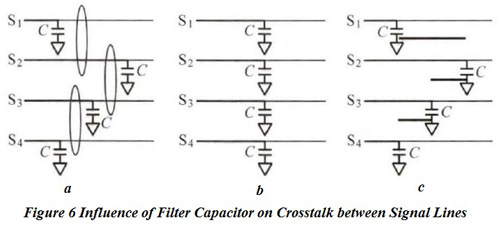

PCBレイアウトの過程では、同じ属性を持つ一部の信号線は、同じタイミング・同じ方向で、かつ一定の密度を保って配線する必要があります。もしPCBのスペース制約により、フィルタ部品を同一ライン上に配置できない場合、信号間のクロストークが発生しやすくなります。この状況は、下記の図6に示されています。

c. シールド接地線がエッジ効果に与える影響

高感度の信号ラインや、高い d を持つ信号ラインの場合u/dt, d私/dtPCB の端に配置されている場合、PCB の中央に配置されている場合よりも EMC のリスクが高くなります。端にある信号線は、より大きな寄生容量により、高周波干渉や外部放射を受けやすくなります。

PCB の面積に制約がある場合、設計ファイル内で 20H 原則に従って PCB をレイアウトすることは非常に困難です。「パケット」を用いることで、干渉や外部放射を低減することができます。パケットラインは、太さや形状などの特定の要件を満たす必要はありません。通常、信号線が PCB の端に近すぎて銅箔を張れない場合、7〜10mil の範囲のグランドラインをシールドとして追加することができます。

d. デジタル回路とアナログ回路間の相互干渉

高速デジタル回路と微小アナログ信号を同一のPCB上に実装する場合、不適切なPCBレイアウトでは、デジタルノイズによってアナログ信号にクロストークが発生しやすくなります。デジタル回路とアナログ回路の相互干渉は、主に以下の要因によって引き起こされます。第一に、寄生容量および寄生インダクタンスによるクロストークノイズです。第二に、電源リップルやデジタルチップ電源のデカップリング不良によって電源ノイズが生じます。第三に、グラウンドインピーダンスおよびシステムグラウンドの取り方が原因でノイズが発生します。ノイズ問題への対処は、電源、信号、グラウンドの順に行うべきです。