PCB設計の複雑さが増大するにつれて、安定かつ信頼性の高い電源は、研究の新たな潮流となっている高速PCB設計特に、スイッチング素子の数が継続的に増加し、Vcore が継続的に低下している場合、電源の変動はシステムに致命的な影響を及ぼしがちです。したがって、電源システムの安定性を維持することは、高速 PCB 設計における重要なポイントとなっています。

しかし、電力系統インピーダンスの存在により、負荷の過渡電流によって電力系統インピーダンスに比較的大きな電圧降下が生じ、それが系統の不安定を引き起こす。始めから終わりまで各コンポーネントに正常な電力を供給するためには、電力系統内のインピーダンスを制御しなければならず、つまりインピーダンスを可能な限り低減する必要がある。

デカップリングコンデンサの適用は、電力システムにおけるインピーダンスを抑制するための有効な手段である。本稿では、デカップリングコンデンサによる電力システム内のインピーダンス抑制の理由を分析し、デカップリングコンデンサの選定に関する方法を列挙する。さらに、電力システムにおけるインピーダンス抑制効果を最大化するために、高調波解析に基づいてデカップリングコンデンサの配置位置をどのように決定するかを主に研究する。

インピーダンス解析

電源とグラウンドは、大きな平板コンデンサと見なすことができ、その容量は次の式に基づいて計算されますC=kAr/d

この式ではk0.2249インチです。A2つの平面の間の平行な領域を指します。r媒体の誘電率を指し、一般的に使用されるFR4基板材料では4.5である。d電源とグラウンド間の距離を指す。例として、サイズが 2×1 インチの PCB を取り上げる。電源とグラウンドによって形成されるコンデンサのうち、並行面積が 20 ミルの場合、その容量はおおよそ 0.2249×4.5×2×1/0.02 = 101.2pF となる。この式に基づけば、電源系統における自己デカップリング容量は非常に小さく、それに対応するインピーダンスは一般に数オームと非常に大きくなることが分かる。したがって、電源系統の自己デカップリングだけではインピーダンスを十分に低減することは到底できない。

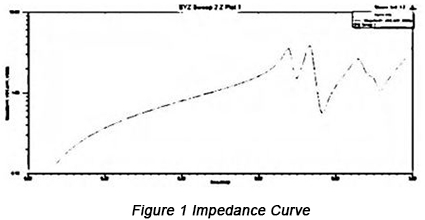

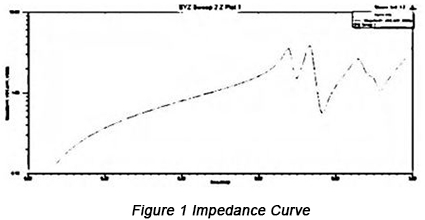

2.5D レベルのシミュレーションツール SIWAVE を用いて、能動デバイスのインピーダンスシミュレーションを実施する。電源およびグラウンド U41 のネットワークを抽出し、0~1GHz のスイープ範囲で XYZ パラメータを計算することにより、以下の図1に示すインピーダンスカーブを得る。

図からわかるように、インピーダンス曲線は周波数の変化に伴って変化し、670MHz、730MHz、870MHz の値における変曲点でインピーダンスが大きく変動している。

禁止方法

・デカップリングコンデンサによるインピーダンス抑制の理論解析

電源そのものからのデカップリングによってインピーダンスを低減することは不可能であるため、インピーダンスを抑制するためにデカップリングコンデンサを適用する必要があります。

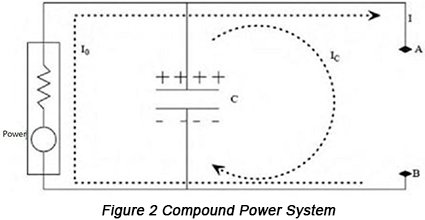

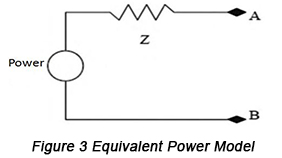

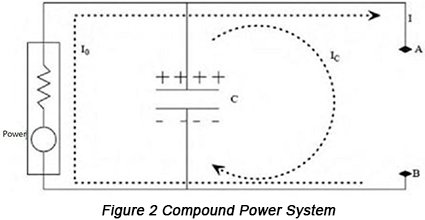

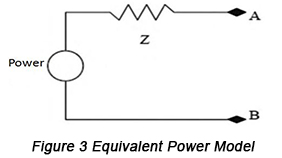

図2は複合動力システムの概略図である。図3は、この動力システムを等価動力モデルで示している。

この回路を表すために式を適用することができます。V=ZxLA点とB点の間で負荷過渡電流が大きく変化し続けたとしても、両点間の電圧変動はごく小さく抑えられるような状況を実現する必要がある。式に基づけば、この目的はインピーダンスの値が(Z) が十分に小さい場合である。図3において、デカップリングコンデンサの適用はこの目的の達成に有効であり、等価回路の観点から、デカップリングコンデンサが電力系統のインピーダンスを低減できることが示されている。さらに、回路理論の観点からも、同じ結論が得られる。コンデンサは交流信号に対して低インピーダンスであるという特性を持つ。その結果、コンデンサが関与することで、電力系統における交流インピーダンスは確実に低減される。

・デカップリングコンデンサの容量の選定

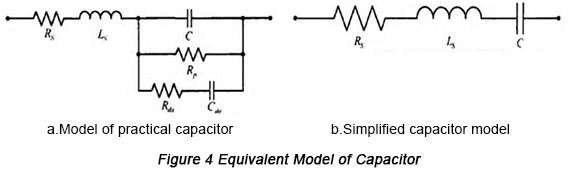

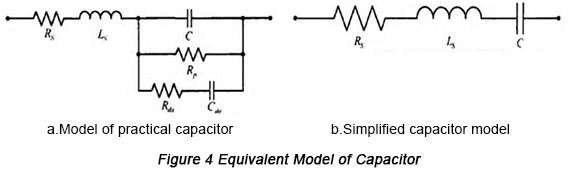

理想的なコンデンサというものは存在せず、必ず寄生パラメータを有しています。コンデンサの高周波特性に最も大きな影響を与えるのは、ESR(等価直列抵抗)とESL(等価直列インダクタンス)です。図4は、寄生パラメータを考慮した等価モデルを示しています。

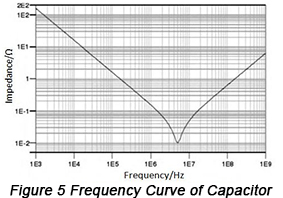

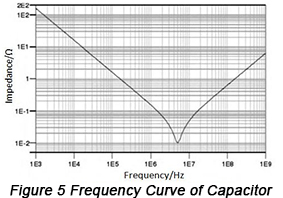

コンデンサは、次の式に従う直列高調波周波数をもつ直列高調波回路としてもみなすことができる。f=1/2PIFC。低周波数の状況では容量性を示します。しかし、周波数が上昇すると、常にそのインダクタンスを示すようになります。言い換えると、そのインピーダンスは周波数の上昇に伴って最初に増加し、その後減少し、等価インピーダンスの最小値は直列共振周波数で発生します。f0このとき、容量性リアクタンスと誘導性リアクタンスがちょうど相殺され、インピーダンス値とESRが等しくなり、コンデンサの等価抵抗が最小となることが示される。コンデンサの周波数特性曲線を図5に示す。

したがって、コンデンサ選定の過程においては、選択するコンデンサの高調波周波数点が、デカップリングが必要となる周波数点の近傍に位置するようにする必要があります。可能な限り自己共振周波数に達する前に、その容量特性が十分に発揮・活用されなければなりません。

異なる静電容量を持つコンデンサは、それぞれ異なる自己高調波周波数に対応しており、下表に示されています。

|

静電容量

|

DIP(MHz)

|

STM(MHz)

|

| 1.0μF |

2.5 |

5 |

| 0.1μF |

8 |

16 |

| 0.01μF |

25 |

50 |

| 1000pF |

80 |

160 |

| 100pF |

250 |

500 |

| 10pF |

800 |

1.6(GHz) |

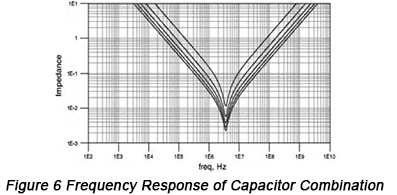

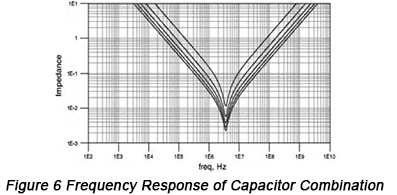

一般的に、デカップリングコンデンサには高調波特性が求められ、複数のコンデンサを並列に組み合わせることで最も低い入力インピーダンスが得られます。同一種類のコンデンサを並列接続した場合の周波数特性を、下の図6に示します。

この方法に基づき、等価ESRおよびESLを大幅に低減することができる。複数のコンデンサに対して(n) 同じ容量の場合、合成後の等価容量 C は nC となり、一方で等価インダクタンスはL〜になるL/n等価ESRはR/nとなる。しかし、高調波周波数は変化しない。自己高調波周波数はコンデンサの種類が異なっても同一であるため、並列に接続するコンデンサの数が多いほど、自己高調波周波数の位置は変わらずに、容量性領域および誘導性領域におけるインピーダンスがより小さくなることが分かる。

結論として、デカップリングコンデンサを選定する過程においては、デカップリング周波数をデカップリングの自己共振周波数点として捉え、それに対応するコンデンサを選択する必要があります。さらに、同一容量の複数コンデンサを並列に用いることで、デカップリング能力を向上させ、インピーダンスを低減することができます。

・デカップリングコンデンサの配置位置の決定

デカップリングコンデンサを選定した後は、その配置位置を考慮する必要があります。電源プレーンとグラウンドプレーンは、複数のインダクタとコンデンサから構成されるネットワーク、あるいは共振キャビティとしてみなすことができます。ある周波数において、インダクタとコンデンサに共振が生じ、電源系統のインピーダンスに影響を与えます。周波数が高くなるにつれてインピーダンスは絶えず変化し、特に並列共振が顕著な場合には、インピーダンスも著しく上昇します。したがって、デカップリングコンデンサの具体的な配置位置は、PCB の高調波解析と組み合わせて決定する必要があります。

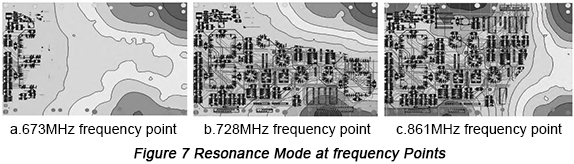

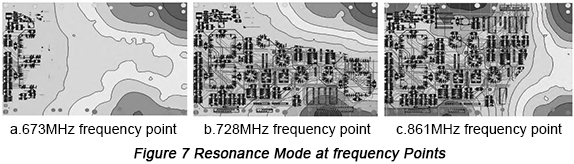

SIWAVEシミュレーションツールの共振解析機能を適用することで、抵抗、容量、インダクタンスを含む等価パラメータが導出される。さらに、図7に示すように、異なる周波数ポイントにおける共振モードを取得して、PCBの共振解析を実施する必要がある。

図1と合わせて見ると、比較的大きなインピーダンスを示すいくつかの周波数ポイントが、共振が発生する周波数ポイントと一致していることが観察できる。したがって、共振解析の結果から、共振が顕著な領域には、インピーダンスを低減するために、適切な容量値を持つデカップリングコンデンサを配置すべきであると結論づけられる。

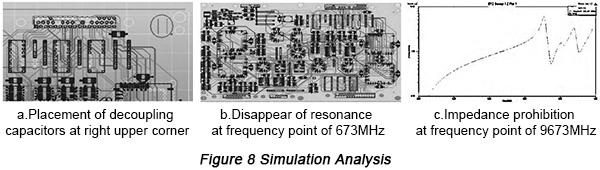

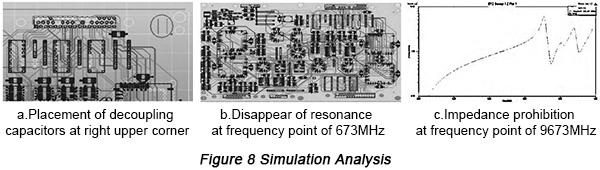

例として 673MHz の周波数ポイントを取り上げると、図 8 に示すように、デカップリングコンデンサを並列に配置することで共振が消失し、対応するインピーダンスが抑制される。

PCBの共振解析に基づき、共振が発生する対応する位置を特定し、その位置に適切な容量のコンデンサを並列に配置することでインピーダンスを抑制する。