今日では多層PCBほとんどの高速回路システムで使用されており、多くの回路システムには多数の動作電源が存在するため、特に複数の電源/グラウンドプレーン間の関係の処理など、イメージプレーン設計に対して厳しい要件が課されています。さらに、高電力部品に優れた放熱性を提供し、発振器がRF(無線周波数)エネルギーを発生するのを防ぐために、デバイス層設計では特別な銅箔クレッド面を設計する必要があります。

PCB がショッピングカートに正常に追加されました

今日では多層PCBほとんどの高速回路システムで使用されており、多くの回路システムには多数の動作電源が存在するため、特に複数の電源/グラウンドプレーン間の関係の処理など、イメージプレーン設計に対して厳しい要件が課されています。さらに、高電力部品に優れた放熱性を提供し、発振器がRF(無線周波数)エネルギーを発生するのを防ぐために、デバイス層設計では特別な銅箔クレッド面を設計する必要があります。

イメージプレーンは、プリント基板において信号層に隣接する銅張りの面です。イメージプレーンの主な機能には、次のようなものがあります。

1).リフローノイズとEMIの低減(電磁干渉). イメージプレーンは、特に電源分配システムに大電流が流れている場合に、信号のリターン電流に対して低インピーダンスの経路を提供します。さらに、信号とリターン電流によって形成される閉ループ面積を小さくすることで、EMI を低減します。

2).高速デジタル回路における信号線間のクロストークの制御。クロストークは、D/H の比によって決まり、ここで D は干渉源と被干渉対象との距離を指し、H は信号層間のイメージプレーンの高さを指す。D/H の比は H の値を変えることで制御でき、その結果、信号線間のクロストークを最終的に制御することができる。

3).インピーダンスの制御。プリント配線の特性インピーダンスは、配線の幅および配線とイメージプレーンとの間の高さに関連している。イメージプレーンがない場合、インピーダンスを制御できない可能性があり、その結果、伝送線路のマッチングができず、信号反射を引き起こす。

さらに、イメージプレーンは外側のボードへの反射によるノイズを制御することも可能である。とはいえ、これらの機能を実現するにはイメージプレーンだけでは不十分であり、期待される目標を達成するためには厳格な設計ルールを補完的に適用しなければならない。この事実は次のように言い表すことができる。すなわち、高速デジタル回路においてノイズを制御するためにはイメージプレーンは不可欠であるが、それ単独では機能しないということである。

多層プリント基板においては、各配線層はそれぞれ 1 つのリファレンスプレーンに隣接し、信号のリターン電流は対応するリファレンスプレーン上を流れるべきである。信号線がある配線層を通過しない場合、一般的な方法としては、まず信号線をビアによってある配線層に接続し、その後さらに別の層へと接続する。したがって、信号線がある層から別の層へ飛び移るのと同様に、リターン電流も同じ経路に従って飛び移ることになる。両方の層がグランド層である場合、リターン電流は 2 つの層を接続するビアやグランドピンを介して飛び移ることができる。一方、一方の層が電源層で、もう一方がグランド層である場合、リターン電流が層間を飛び移ることができる唯一の場所は、デカップリングコンデンサが配置されている位置である。もしデカップリングコンデンサやグランド層同士を接続するビアが存在しない場合、リターン電流は最も遠回りの経路を通らざるを得ず、その結果、他の回路との結合が弱まり、クロストークや EMI を引き起こす原因となる。

その結果、〜の過程でPCB設計レイヤースキッピングは、可能であれば部品に隣接するグランドピンやデカップリングコンデンサの周囲で設定するべきです。これが実現できない場合は、リターン電流をスキップさせるために、スキッピングポイントにグランドスルーホール(2つのグランド層間のスキッピング)やバイパスコンデンサ(電源層とグランド層間のスキッピング)を配置することができます。

多層PCBを使用する過程では、一定の幅を持つ無銅箔エリアを生成し、ひとつの一体型プレーンを複数の独立した部分に分割する必要が生じることがあります。これをプレーン分割と呼びます。

スプリットプレーンは通常、ノイズが感度の高い回路に干渉するのを防ぎ、異なる基準電圧を分離するために使用されます。例えば、デジタルノイズがアナログ、オーディオ、I/O エリアに入り込むのを防いだり、5V と 3.3V の電源電圧間を絶縁したりする目的で用いられます。

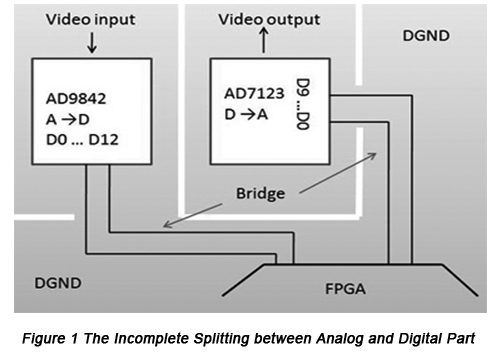

分割プレーンは、完全分割と不完全分割に分類することができます。前者は、分割後に電源層とグラウンド層が完全に分離されている状態を指します。後者は、電源層同士は完全に分離されている一方で、グラウンド層同士が「ブリッジ」によって接続されている状態を指します。完全分割と不完全分割のどちらを採用するかは、分割プレーン間に信号接続が存在するかどうかによって決まります。

・分割平面の例

図1は、あるテストプラットフォームにおけるアナログ・デジタル混在回路のイメージプレーン設計の一部である。ビデオアナログ入力は、AD変換によってFPGAに送られ、DA変換として出力される。ADとDAはいずれも、電源供給のために独立した電源コンポーネントを使用している。基板上ではデジタル部品が大部分のスペースを占め、アナログ部品はごく一部しか占めていない。しかし、いずれもシステム全体の性能にとって重要な不可欠要素である。そのため、これらの部品を扱う過程では細心の注意を払う必要がある。理想的には、デジタル部のノイズがアナログ部に入り込まないことが望ましい。しかし、ADおよびDAコンバータからのいくつかの信号は、デジタル部であるFPGAに接続されている。これら接続信号のリターンパスを確保するためには、デジタル電源とアナログ電源は完全に分離しつつ、デジタルグラウンドとアナロググラウンドは完全には分離しないようにし、デジタル部からアナログ部への影響を最小限に抑えなければならない。

デジタル部からアナログ部へ向かうすべての配線はブリッジを通過しなければならず、その開口サイズは必要な配線が通過できる程度にちょうど適切な大きさとする必要があります。こうすることで、データ信号のリターン電流がブリッジを経由して戻ることが可能となり、リターンパスの迂回によって他の信号に干渉を与えることを防ぎます。本PCB設計では、AD部とDA部のグラウンドは互いに完全に分離されています。

・平面分割の過程におけるいくつかの問題

a. 絶縁層の重なり

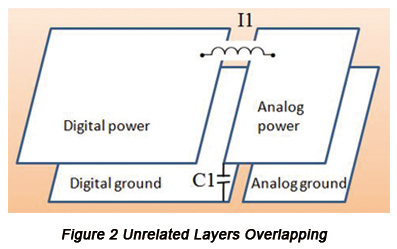

多層プリント基板では、異なる電源を分離するために分割プレーンがよく用いられます。一般的に言えば、これらの電源に対応するグラウンド層同士も互いに分離されており、つまり各電源にはそれぞれ専用のリファレンス層があります。PCB設計の過程では、これら分離された層同士が重ならないようにしなければなりません。例えば、ほとんどの多層プリント基板では、アナログ部の電源層とグラウンド層、およびデジタル部の電源層とグラウンド層は互いに分離されています。図2に示すように、アナログ電源層とデジタルグラウンド層が空間的に重なることがあってはなりません。

重なり合うアイソレーション層が現れると、重なり部分に小さなパッド容量 C1 が生じます。この容量により、ある層から別の独立した静的なアイソレーション層へと伝送される高周波エネルギーが発生し、アイソレーションの有効性が低下します。

b. デカップリングコンデンサの配置

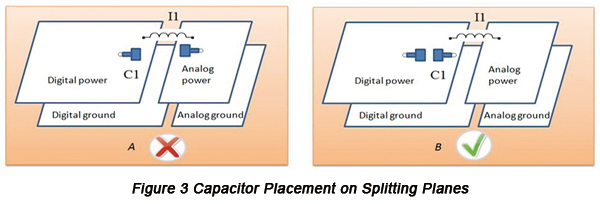

高速コンポーネントによって発生する高周波ノイズを除去するために、多数のデカップリングコンデンサが配置されているプリント基板. PCB にスプリットプレーンが存在する場合、レイアウト作業の過程で、デカップリングコンデンサのグランド端子が、本来対応すべきグランド層ではなく、他の基準グランド層に接続されてしまう状況が発生する可能性があります。この種のミスが起こると、ある層から別の層へノイズがデカップリングされてしまい、スプリットプレーンの重なりと同様の問題を引き起こします。そのため、この問題は設計段階で対処しておく必要があります。再びデジタル・アナログ混在回路を例にとります。アナログ電源はフェライトビーズを介してデジタル部から引き込まれ、C1 はデジタル部のデカップリング容量を表します。図 3A では、C1 の電源端子がデジタル電源に接続されている一方で、グランド端子がアナロググランドに接続されており、その結果、高周波のデジタルノイズが感度の高いアナログ部でデカップリングされてしまいます。これは誤った接続です。図 3B は正しいデカップリングコンデンサの接続例です。

c. 単一点接地

異なる電源を持つリファレンス層が相互に接続される場合、単一点接地を確保しなければなりません。例として示したデジタル・アナログ混在回路では、基板はデジタル部とアナログ部に分類され、デジタルグラウンドとアナロググラウンドの双方に少なくとも 2 つの接続点があるため、ノイズ信号が 2 つの接続点を介して 2 つのリファレンス層間を循環しうる状態になります。これを「グラウンドループ」と呼びます。グラウンドループは、ノイズ、EMI、電力損失および放熱の困難を引き起こします。グラウンドループ問題には簡単な解決策があります。リファレンス層間の接続点を 1 か所のみにすれば、ループは形成されません。

イメージプレーンの一部として、ローカルグランド層とは、PCB の表面に設けられた銅箔であり、内部のグランド層に直接接続されているものを指します。その主な機能は、一部の重要なチップ(例えばオシレータ)の内部で発生する RF 磁束を捕捉すること、または放熱用途に用いられることです。

優れた性能を得るためには、発振器、水晶およびクロックサポートは、独立したローカルグラウンド層上に実装する必要があります。その理由としては、次の点が挙げられます。

1).発振器が金属クラッドに封止されている場合、金属クラッド内部で発生する高周波電流が非常に大きくなり、そのグランド端子では、低損失な方法でその大電流をグランドへ導くことができない可能性があります。その結果、この金属クラッドは単極アンテナとなってしまいます。

2).もし表面実装組立この手法は発振器をプリント基板上に実装する際に用いられますが、前述の問題はさらに悪化します。というのも、SMTパッケージには通常プラスチック材料が使用され、RF電流がグラウンドポイントへ導かれるのを妨げてしまうからです。最終的に、パッケージ内部で発生したRF電流は自由空間へ放射され、他の部品と結合してしまいます。

3).一般的な発振器は、超高速かつ立ち上がりの速いエッジレートを持つコンポーネントに属するクロックバッファリングを駆動することが可能であり、多量のRF電流を発生させるため、電流機能の故障を引き起こす可能性があります。

発振器およびクロック回路内にローカルグランド層が組み込まれている場合、発振器および関連回路内部で発生する高周波エネルギーを捕捉して高周波放射を低減するために使用されるイメージプレーンが提供されます。

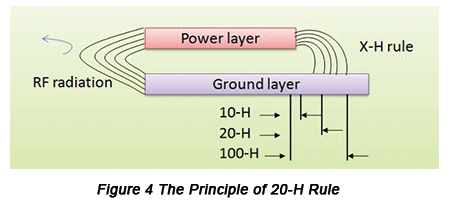

経験則として、20-Hルールは、高密度の多層PCBにおいて、回路基板から自由空間へ放射される電磁エネルギーを低減するために、電源層のサイズをグランド層よりも20Hだけ小さくすべきであると説明している。ここでHは、これら2つの層間の距離を指す。図4では、左側は特別な設計を施していない電源/グランド層を示しており、エッジ放射が非常に強く、隣接回路の機能に影響を与える可能性がある。右側は、電源面のサイズをX-Hだけ縮小することでのRF放射の状況を示している。グランド層が多くの磁力線を引きつけ、RF放射エネルギーが低減されていることが分かる。実験結果によれば、RF放射強度は10-Hから低下し始め、20-Hの場合にはグランドが磁束の70%を引きつけることができ、100-Hの場合には磁力が98%低減される。

もちろん、20-H はすべてにとって完璧というわけではありませんPCB構造20-H の効率は、動作周波数、電源層/グラウンド層の物理サイズ、およびそれらの間隔に依存し、後者 2 つの要素が PCB ボードの SRF(自己共振周波数)を決定する。研究によれば、PCB がいずれかの SRF で動作している場合、20-H は機能せず、グラウンドも放射エネルギーを引き寄せることができない。それどころか、多量の放射エネルギーが発生してしまう。したがって、実際の高速回路では、20-H ルールを採用するかどうかを決定する際に、具体的な状況を考慮しなければならない。

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

[email protected] [email protected]

[email protected] [email protected]

ご支援ありがとうございます!お寄せいただいたご意見は、サービス最適化のために詳細に検討させていただきます。お客様のご提案が最も価値のあるものとして採用された場合、100ドル分のクーポンを添えて、すぐにメールでご連絡いたします。