エレクトロニクス製造の世界において、試作から量産(ハイボリュームマニュファクチャリング)への移行は、もう一つの重要な転換点となります。試作段階が機能性と市場投入までのスピードに重点を置くのに対し、大量生産の中核となる原則は、効率性、一貫性、そして――何よりも重要なのは――コスト管理です。1万台を超える生産ロットでは、単一のはんだ付け箇所や部品で数セントのコストを削減できれば、スケールメリットによって数十万ドル規模の利益につながる可能性があります。

コスト最適化(in)PCBA単に材料費の引き下げを交渉することにとどまらず、エンジニアリング設計、サプライチェーン管理、および製造プロセスを統合する包括的な分野です。以下では、大量生産環境におけるコスト最適化のための実行可能な戦略を示します。

コスト構造の分解

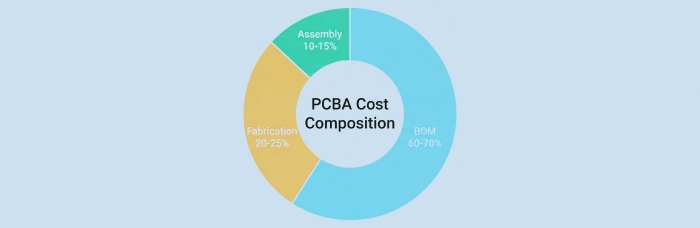

コスト構成を理解することは、意味のあるコスト削減の中心となります。PCBA の価格は、通常 3 つの要因によって決まります。

部品表(BOM)コスト:これは通常、総コストの60~70%を占めます。量産時には、単一ソースの高級ICやコネクタが「価格の下限」を設定してしまうことが多く、交渉が難しくなります。

PCB製造:層数は最も重要なコスト増加要因です。4層基板から6層基板に移行すると、ベア基板のコストが30〜50%上昇する可能性があります。また、特殊なプロセス(例えば、HDIまたはブラインドビア/ベリードビア製造コストを大幅に膨らませる。

組立と労働:SMTは自動化の度合いが高く、コスト効率にも優れていますが、THTでは部品の実装に手挿入または専用パレットのいずれかを使用するため、非効率でコストも高くなります。

製造のための設計(DFM)

最初の基板が一枚でも製造される前に、最も大きなコスト削減効果が生まれます。DFM原則は設計段階そのものにおいて実装される必要があります。

複雑さとレイヤー数の削減

エンジニアは「オーバーエンジニアリング」を強く避けるべきです。コンポーネントのレイアウトと配線ロジックを連携させて最適化することで、可能な限り層数を削減します。例えば、6層設計を最適化して4層に減らすといった具合です。民生用電子機器では、スペースが極端に制限されていない限り、高価なHDIプロセスは回避できます。多くの場合、高価なマイクロビアを必要とするほど基板サイズを小さくするよりも、標準的な配線技術を適用できるように基板寸法をわずかに大きくしたほうが安価です。

BOMの正規化と標準化

膨れ上がったBOMは、気づかれにくい利益の殺し屋です。量産向けの設計は、「標準化」の原則に基づいて行うべきです。

明細行を減らすある設計で 10kΩ と 10.2kΩ の両方の抵抗を使用しており、許容差の範囲内であれば、それらを 10kΩ に標準化してください。これにより、実装機のフィーダースロット数を減らすことができ、セットアップおよび段取り替え時間を短縮できます。

SMD を優先する可能な限り、スルーホール部品ではなく表面実装デバイス(SMD)を使用してください。完全自動化されたSMTラインは、1時間あたり数万個の部品を実装できますが、手作業による挿入ははるかに遅く、品質リスクも生じます。

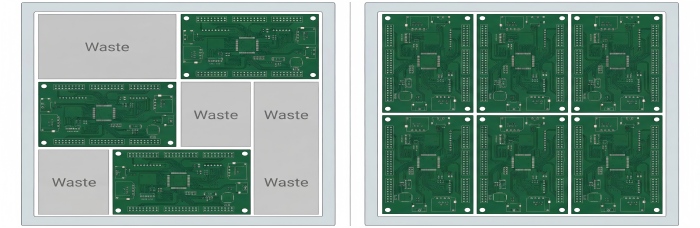

パネル化効率

大量生産では、PCB は「パネル」単位で製造されます。設計者は、端部に生じるレールと呼ばれる廃材を最小限に抑えるために、パネルの利用率を計算する必要があります。最適化されたパネル設計は、ラミネート材料のコストを削減するだけでなく、SMT 装置のスループット率も大幅に向上させます。

サプライチェーンマネジメント

絶えず部品が変動する世界において、サプライチェーン戦略はエンジニアリング設計と同じくらい重要である。

経済的発注量大量生産のボリュームを活用し、在庫保有コストと一括購入による割引のバランスが最も取れたスイートスポットを見つけましょう。これを実現するためには、カットテープで購入するよりも、フルリールで部品を購入したほうが大幅に安くなります。

承認済みベンダーリストを拡大する量産において、BOM に「Murata Only(村田のみ)」と指定することは非常に危険です。すべての受動部品について、エンジニアが 2~3 社程度のセカンドソース(異なるブランド)を検証しておき、調達チームが必要なときに、最も安価かつ/または入手可能なものへ切り替えられるようにすべきです。

ローカリゼーション海外の労働力は安価な場合がありますが、重量物やかさばる製品の場合、海上輸送費や長い輸送時間によって労働コストの節約分が相殺されてしまいます。組立工場周辺のサプライヤーを優先することで、「ジャストインタイム」納入が可能になり、在庫保管の負担を軽減できます。

プロセス最適化と不良品質コスト

テストカバレッジのバランス調整100%の機能テストは安心できますが、通常はHVMには遅すぎます。HVMはその依存の大部分を…AOIそしてICTICTの「ベッド・オブ・ネイル」治具には、数千ドルの前払い投資が必要ですが、回路を数秒で検証でき、手動でのデバッグよりはるかに高速です。

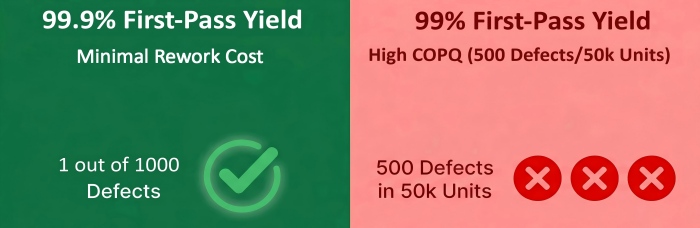

「不良品質コスト」(COPQ)の管理手直しには多大なコストがかかります。5万台の生産ロットにおいて、不良率が1%であれば、500枚の基板が不良となる計算です。後から技術者を雇って不良基板を手直しするよりも、最初から高精度のステンシルやSPI装置に投資して初回合格率を99.9%まで高める方が、はるかに安上がりです。

要するに、~のコスト最適化は大量生産向けPCB実装は、設計原則、サプライチェーン管理、および製造プロセスを慎重に統合する、真に多次元的な取り組みです。企業は、コスト構造の分解、DFM(製造容易化設計)検討、BOM(部品表)の標準化、効率的なパネル化を通じて、かなりのコスト削減を実現できます。さらに、サプライチェーンの柔軟性を高め、品質保証プロセスへの投資を行うことで、製品の一貫性を確保しつつコストを一層引き下げることができます。このような戦略的取り組みは、大量生産規模で競争優位性を確立するうえで不可欠であり、企業が最適化されたコストで高品質な製品を供給することを可能にします。

PCBCart は、この最適化の旅路において信頼できるパートナーとして際立っており、豊富な業界経験と最先端の製造ソリューションを提供しています。私たちの能力は、高度な技術と効率化されたサプライチェーン運用により、大量生産のニーズを支援するよう設計されています。私たちは品質と効率に細心の注意を払い、お客様の製品が複雑さとコストの削減という恩恵を受けられるようにしています。PCBCart をお選びいただくことで、生産プロセスのあらゆる段階で価値を最大化することに尽力するパートナーと歩調を合わせることができます。ぜひ本日 PCBCart にお見積もりをご依頼いただき、大量 PCB アセンブリ案件を、より高い精度とコスト効率で次のレベルへと引き上げる方法をご検討ください。

役立つリソース:

•品質を損なうことなくPCB組立コストを削減する6つの効果的な方法

•PCB製造および実装の価格に影響を与える要因

•多ヘッドガントリー式チップマウンタによるSMT実装プロセスの最適化

•PCBの品質を確保する方法

・PCBのコスト削減と信頼性向上のためのヒントのご案内