パッケージ・オン・パッケージ(PoP)は、個別のロジックおよびメモリのボール・グリッド・アレイ(BGA)パッケージを垂直方向に組み合わせる半導体パッケージング方式である。2つ以上のパッケージが互いに積み重ねられる、すなわちスタックされ、その間で信号を伝送するための標準インターフェースによって接続される。

PoP 技術は、スマートフォンやデジタルカメラなどの電子製品に対して、微細ピッチ化、小型化、高速な信号処理、実装面積の縮小といったエレクトロニクス産業の絶え間ない要求に応えるために生まれました。この技術を適用する際にはPCB組立工程上部パッケージのメモリデバイスと下部パッケージのロジックデバイスの間で電気的接続が行われることで、これらのデバイスは個別にテストおよび交換することさえ可能となる。これらすべての特長が役立っている。PCB組立コストを削減するおよび複雑さ。

広く使用されているPoP構造には、標準PoP構造とTMV PoP構造の2種類があります。

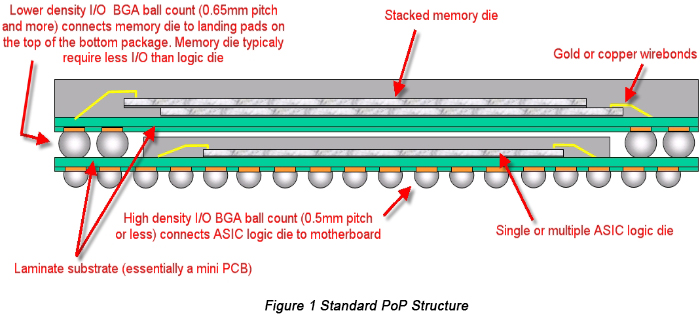

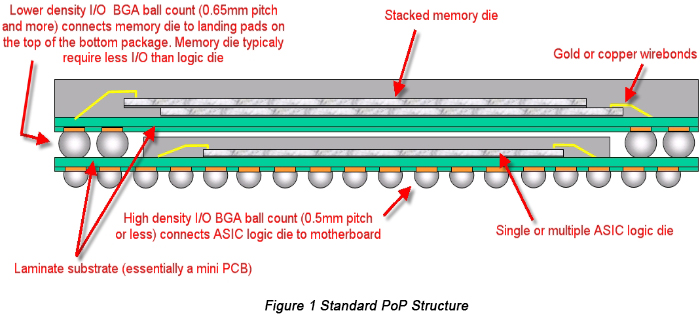

標準的なPoP構造

標準的なPoPでは、ロジックデバイスは下側パッケージに配置され、ロジックデバイスは多数のピン数というデバイス特性に対応して、微細ピッチBGAはんだ構造を備えています。標準PoP構造における上側パッケージには、メモリデバイスまたは積層メモリが搭載されます。メモリデバイスが有するピン数が不足しているため、マージンアレイを適用することで、2つのパッケージの周辺部においてメモリデバイスとロジックデバイス間の相互接続を実現することができます。

現在、ボトムパッケージではワイヤボンドが急速にフリップチップ技術に置き換えられており、より小型のパッケージサイズに対する高い要求に応えるため、ボトムパッケージのはんだピッチは継続的に縮小している。0.4mm のはんだピッチはボトムパッケージで一般的に適用されている。さらに、アッパーパッケージ内の DRAM チップおよびフラッシュメモリを内蔵した DRAM チップの双方で、より高い速度と帯域幅が求められている。それに対応して、トップパッケージにはより多くのはんだボールが必要となり、アッパーパッケージのはんだピッチを縮小する必要が生じている。当初は 0.65mm のピッチで十分であったが、現在ではより微細なピッチが要求されている。先ほど述べたように、0.4mm のピッチは PoP 構造に広く適用されている。

ウィキペディア(wikipedia.org)からの画像

高い集積による小型化は、PoP の広範な普及に寄与する重要な要素です。PoP のサイズを決定する主な要素には、次のものが含まれます。

・ベアロジックデバイスの最大サイズ

・ロジックデバイスのI/Oインターフェース数

・電源およびグラウンドの全体的なバス数

・上部パッケージ内のメモリデバイスの寸法であり、全体的な I/O、電源、グランドおよび機械的サポートを提供するもの。

・BGA に統合されたロジックおよびメモリデバイスの構成によって要求される高密度配線およびクロスネットワーク。

・ボトムパッケージおよび関連エリアで要求される総はんだ数

TMV PoP 構造

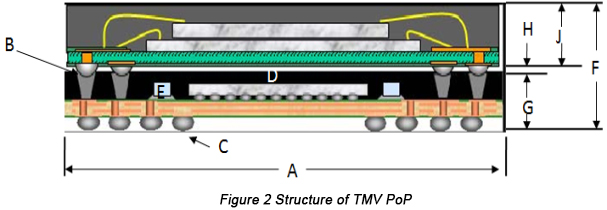

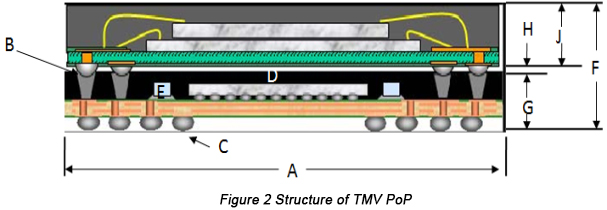

標準PoPに基づいて開発・改良されたスルーモールドビア(TMV)PoPは、微細ピッチという利点により、携帯型電子機器の用途で広く用いられている。図2にTMV PoPの構造を示す。

次の表は、TMV PoP 構造の主要寸法を示しています。

|

パッケージ(A)

|

上側はんだ

配列 (B)

|

ボトムはんだ

配列 (C)

|

シリコンウェーハ(D)

|

パッシブ

コンポーネント(E)

|

積層パッケージ(F)

|

| 14×14mm |

ピッチ:0.5mm

パッド:200

配列: 27*2 |

ピッチ:0.4mm

パッド:620

配列:33×6 |

7.10mm*6.97mm*0.13mm |

サイズ:0105

数量:32 |

金型上面から:0.40

下層:0.21mm

底部パッケージ高さ:0.76mm

クリアランス(H):0.03mm

パッケージ最高高さ (J):0.53mm

全高:1.32mm |

TMV PoP において、スルーモールドビアは、ボトムパッケージ内のスルーモールドビアおよびボトムパッケージのトップ側はんだとトップパッケージのはんだとの間を介して、トップパッケージ内のロジックデバイスとボトムパッケージ内のメモリデバイスとの電気的接続を担っている。トップパッケージおよびボトムパッケージの両方のはんだは、はんだ付け前は球状であったが、はんだ付け後には図2に示されているような、B が指し示す円柱状の形状になった。

TMV PoP は、パッケージサイズ、厚さ、および反りを縮小できると期待されています。さらに、次世代 PoP がより高い接続密度、性能、および信頼性を実現することを可能にします。その利点には、次のような点が含まれます。

・ピッチとパッケージクリアランス間のボトルネックを解消し、増大するメモリインターフェース密度の要求を満たすのに貢献します。

・バランスの取れた完全成形構造は、反りを抑制し、下部パッケージの薄型化要求を満たすのに有利である。

・チップとパッケージ間に寸法比が追加されます。

・ワイヤボンディング、FC、積層チップおよび受動部品の構成に寄与します。

・トップコンポーネントおよびボトムスルーモールドビアの信頼性向上に役立ち、より大きな体積のはんだを保持できるため、より高いスタンドオフ高さをサポートし、熱サイクル時の応力分布を改善します。

PoP の表面実装技術(SMT)方式には、プリスタック PoP とオンボードスタッキング PoP の 2 種類の技術があります。

プリスタック型PoP技術では、メーカーはトップパッケージとボトムパッケージを積層し、はんだ付けを行って「プリスタックデバイス」と呼ばれる一体型コンポーネントとした後、その一体化されたコンポーネントをプリント基板(PCB)表面に実装し、リフローはんだ付けを行います。

オンボードスタッキングPoP技術では、メーカーは回路基板上でボトムパッケージとトップパッケージを順次積層します。まず、ボトムパッケージを回路基板上に実装し、その後、フラックスまたははんだペーストにディップした後にトップパッケージをボトムパッケージ上に実装します。次に、積層パッケージに対してリフローはんだ付けを行います。

両面SMT実装を例に取ると、オンボードスタッキングPoP実装の手順には次のものが含まれます。

・非PoP側コンポーネント組立(印刷、実装、リフローはんだ付けおよび検査);

・PoP側へのはんだペースト印刷

・ボトムパッケージおよびその他のデバイスの実装・取り付け

・トップパッケージデバイスのフラックスまたははんだペーストへのディッピング

・トップパッケージ実装

・リフローはんだ付け

・検査(X線またはAOI)

プリスタック型PoPのSMT実装技術と比較すると、オンボードスタッキングPoPには、トップパッケージのフラックスまたははんだペーストディッピングと、トップコンポーネントの実装という2つの工程が追加される。

ステップ1:PoPボトムパッケージのはんだペースト印刷

PoPボトムパッケージのはんだペースト印刷は、部品サイズ、パッドサイズ、および部品間クリアランスによって決定される。01005や高密度CSP(チップスケールパッケージ)の広範な適用により、クリアランスは0.1~0.15mmへと推移し、ステンシル印刷におけるクリアランスは4~5milの範囲となっている。このような高まる要求を満たすために、レーザーカットおよび/または電鋳によるラダーステンシルテンプレートが一般的に用いられる。はんだペーストは印刷クリアランスに基づいて選定される。多くの企業がType IVはんだペーストの使用を開始している一方で、Type IIIはんだペーストも依然として多くの場面で使用されている。

PoP 実装のボトムパッケージは、はんだペースト印刷の制御技術という点で BGA(ボールグリッドアレイ)および CSP 実装と同一であり、ボトムパッケージ PoP と他のファインピッチ部品との間に顕著な差異は見られません。印刷品質の検査は、プリンターまたは AOI(自動光学検査)装置で行うことができます。

ステップ2:PoPトップパッケージのディッピング

はんだペーストディッピングであれフラックスディッピングであれ、すべての実装システムはトップパッケージのディッピングを成功させるために、統合ディッピングモジュールを考慮しなければならない。ディッピング中は、全体としてのディッピング能力を考慮する必要がある。接触面積の向上に伴い、PoP によってはんだペースト表面にもたらされる応力もそれに応じて増加する。不十分または不完全なはんだペーストのピックアップを避けるため、吸着能力、あるいは吸着ツールが作用する領域を変更することが推奨される。表面実装組立の前に、はんだペースト表面と PoP 積層体との間に横方向の動きが生じると、はんだ付け端子における濡れ性不良の可能性が確実に高まる。リフローはんだ付けの前には、はんだ付け端子の周辺にあるはんだペーストを除去しなければならず、そうしないと、はんだ付け不良を引き起こすおそれがある。

ディップ後のはんだペースト表面の変化を注意深く観察することは重要です。

はんだペーストの厚さは、はんだペーストの表面を強く移動するスクレイピングブレードによって制御されます。

ディップ後および表面実装前において、表面実装装置が備える位置決め検査システムは、はんだ上のソルダーペーストまたはフラックスの流出や不足を検査できるとともに、はんだ上の過剰なソルダーペーストも検査できなければならない。不適切なディップ厚さやソルダーペーストの粘度変化は、ディップされるソルダーペースト量の変動を引き起こす可能性がある。さらに、環境変化、トレイ内での長時間の待機、および大気への曝露時間により、ソルダーペーストの特性が変化する可能性がある。

ディップ後および表面実装前のはんだ検査には、色認識の問題により大きな課題が生じる。PoP や FC においては、フラックスディップ後のはんだにいくつかの外観上の変化が見られる。AOI の要求を満たすためには、フラックスサプライヤーはフラックスに着色しなければならない。現在、白、黒、赤といった着色剤がフラックスに広く用いられている。

はんだペーストディッピングとフラックスディッピングのいずれにおいても、信頼できる量のはんだペーストまたはフラックスが確保されていることを保証しなければならない。具体的な用途に関しては、実験や最適化に頼ることができるが、評価が困難な問題については、他の方法を検討すべきである。たとえば、ディッピングフラックスの量を判断するのは比較的難しく、はんだペーストディッピングの量は、ディッピング後の重量変化の観察によって評価する必要がある。

優れたディッピング効果を得るためには、はんだペーストディッピングおよびフラックスディッピングにおいて、以下のいくつかの重要な要素を確保する必要があります。すなわち、均一性、トレイ上での滞留時間、ディッピング量と体積の一貫性、およびディッピング後のリフローはんだ付けまでの待機時間です。

A.同質性

最初、均一性は、ディッピング材料をガラス表面に塗布し、その後光学顕微鏡で観察する方法で確認された。もし均一でクリーミーな質感が観察されれば、均一性が達成されていることを示していた。一方、波状またはざらついた外観、大きな粒子や凝集体が見られた場合は、均一性が達成されていないことを示していた。均一性に関する要求は PoP のサイズによって決定される。一般的に、直径がはんだの直径の 3 分の 1 を超える粒子は、ディッピングに混入してはならない。

B.トレイ上での滞在時間

ディッピング工程では、フラックスまたははんだペーストが、厚さを設定できるドクターブレードによって回転トレイ上に均一に塗布される。水分の侵入や蒸発により、材料の特性が低下したり、さらには不均一を引き起こす可能性がある。滞留時間は、1作業シフト(8~10時間)全体と同程度の長さであるべきであり、ディッピング装置を用いてディッピング後のPoPの一貫性を監視することで算出できる。さらに、はんだペーストおよびフラックスの粘度は、印刷厚さを200~250μmの範囲と規定しているIPC-TM-650の規定に基づいて測定することができる。

C.浸漬量と体積の一貫性

特にフラックスディッピングにおいて、ディッピング量と体積の整合性を判断することは複雑な問題です。PoP のディッピング量は、ディッピング前後の重量を測定することで算出できます。

PoP を反転させてディップした後、光学顕微鏡下でディッピングソルダーペーストの均一性を検査することができます。フラックスが透明であるため、フラックスディッピングの均一性を測定することは非常に困難な作業であり、そのため以下の手順をガイドとして示します。

・フラックスを回転槽に投入し、固定されたゴムローラーを使用して均一性を確保する。

・PoP を選び、フラックスに浸します。

・PoPを銅板の上に置き、その後PoPを取り上げて、フラックスを基板上に残します。

・倍率45倍の顕微鏡で銅板を観察する。

フラックスの分布を測定する別の方法として、フラックスディッピングによってPoPをガラスラミネート片の上に積層し、それらをテープで固定します。アセンブリを裏返すと、フラックスの分布を観察できます。ガラスラミネート上にはフラックスのハローが直接確認できます。

着色されたフラックスに関しては、そのフラックス分布の一貫性を測定することがより容易です。とはいえ、ディップされたフラックスの体積は非常に小さいため、着色法は通常省略されます。

D.ディップ後のリフローはんだ付けまでの待機時間

一般的に言えば、ディップ後のリフローはんだ付けまでの待ち時間は、はんだ付け品質にほとんど影響を与えず、フラックスが乾燥しても極端に低いはんだ付け品質を招くことはありません。多くの場合、ゲル状フラックスで、はんだの信頼性は十分に確保できます。しかし、はんだペーストの場合はまったく事情が異なります。はんだペースト中の粉末は酸化されやすいため、ディップ後のリフローはんだ付けまでの許容待ち時間を、あらかじめ確保しておく必要があります。

待機時間の特定は、はんだ形成を観察する実験によって行うことができる。この実験は、はんだ形成の前に酸化物を除去し、優れたはんだ形成を確保することを目的としている。その結果として、ディップ後のリフローはんだ付けまでの待機時間をより長く維持できるかどうかを示すために、フラックスまたははんだペーストを過酷な環境下で試験する必要がある。本実験の条件および要件は次のとおりである。

・フラックスまたははんだペーストは、高い湿度にさらされなければならない。

・リフローはんだ付けの前に、フラックスまたははんだペーストは高温下で長時間、空気にさらされる必要があります。例えば、フラックスまたははんだペーストの性能を試験する場合、相対湿度は95%とし、曝露時間はそれぞれ2/4/8時間とします。

・リフローはんだ付け後、ぬれ不良、ボイド、ブリッジなどの欠陥を検出するために、はんだをX線で検査する必要があります。

本実験では、はんだにディップされたフラックスまたははんだペーストを損傷しないようにするため、ディップ済みPoP構成はまず反転させ、その後に高温高湿環境にさらす必要があります。

E.フラックス浸漬

フラックスディッピングには、次の3つの主な利点があります。もともと存在するはんだ間のサイズ差が拡大しないこと、技術が制御しやすいこと、材料を容易にピックアップできることです。

チップは反りが小さいため、FC におけるフラックスの適用によってオープンはんだ付けが発生することはありません。おそらく FC での適用経験に基づき、PoP では当初ディッピングフラックスが選択されました。しかし、PoP には少なくとも 2 つの接触面(基板と下段 PoP、下段 PoP と上段 PoP)があり、それぞれに反りの問題が潜在的に存在します。この問題の解決策は、はんだ付け不良を引き起こさない範囲でフラックスのディッピング厚を増やすことにありますが、その結果としてコンタミ量が確実に増加し、後工程のボトムフィルにとって真の問題となる可能性があります。

F.はんだペーストディッピング

PoP反りによって生じる問題を解決するためには、フラックスディッピングの代わりにソルダーペーストディッピングを使用する必要があります。フラックスディッピングと比較して、ソルダーペーストディッピングの利点には次のようなものがあります。

・部品および基板の反りをある程度まで補正することが可能です。

・追加の技術を導入することなく、現在の技術との互換性が非常に高い。

・はんだ付け後、部品と基板の間に比較的大きな距離があることは、信頼性の向上に有利です。

・表面実装の前には、はんだペーストをディップしたはんだの方が、より容易に検査できる傾向があります。

はんだペーストディッピングは、品質と性能を最優先に考えた最適な代替手段と見なされているものの、次のような欠点があります。

・兵士同士の違いを拡大して際立たせることができる。

・適用できるはんだペーストの種類が限られており、コストも高い。

ディッピングには、Type V はんだペーストまたはそれより微細な粒子を含むはんだペーストの使用が推奨されます。はんだペーストの金属含有量は重量比で約 80%~85% とし、はんだペーストの適用によってはんだとパッド間の接続性が向上し、オープンはんだ不良の可能性を低減します。微細粒子を含むはんだペーストは高い酸化傾向を有するため、この種のはんだペーストを用いることで均一性を向上させるだけでなく、溶融プロセスを遅延させることも可能です。

リフローはんだ付けの工程において、PoP のトップパッケージが高温を維持するため、はんだペーストが存在していても、はんだ内部にコアの侵入が起こる場合があり、それがオープンはんだ付けを引き起こす可能性がある。微細な粒子を含むはんだペーストを使用すると、はんだペーストの溶融速度が遅くなり、トップパッケージとボトムパッケージが同時に同じ温度に達することで、コアの侵入を防止することができる。

はんだペーストのディッピング厚さは、部品のはんだ寸法によって決定し、十分に安定かつ均一な厚みを確保するとともに、最も小さいはんだにもはんだペーストがディップされるようにしなければならない。はんだペーストのディッピング深さは厳密に管理する必要がある。実験によれば、ディッピング深さがはんだ高さの50%を超えると、一方でははんだペースト量が増加し、他方でははんだペーストがボール端子を包み込んで過剰なはんだペーストの付着を招き、その結果、はんだ付け不良を引き起こす可能性があることが示されている。

ステップ3:PoPコンポーネントの配置

PoP の特殊な構造により、すべての先進的な表面実装システムは Z 軸方向の寸法精度を確保し、組立工程における衝撃や振動に耐えなければならないため、トップパッケージの位置決めと制御には細心の注意を払う必要があります。

PoP の積層構造は変位を引き起こしやすい傾向があります。実装中、実装装置のコンベヤーベルトの伸びにより、ランダムな振動が発生することがあります。リフローはんだ付け装置では、ガス対流も振動を引き起こす場合があるため、十分に考慮する必要があります。

ステップ4:PoPのリフローはんだ付け

鉛フリー技術金属の酸化、不良なぬれ性、不完全なはんだ付けなどの欠陥を引き起こしがちです。酸素濃度が低い(50ppm)の窒素雰囲気では、はんだ付けにより金属の酸化が抑制され、優れたぬれ性を発揮し、完全なはんだの広がり形成に寄与することができます。さらに、セルフセンタリング性にも優れており、はんだ付けコストは25%~50%増加します。

鉛フリーはんだ付けは高温で行われるため、比較的薄い部品や基板(厚さ0.3mm程度)はリフローはんだ付け工程中に変形しやすく、繊細で最適化されたリフローはんだ付けの温度プロファイルが必要となる。さらに、リフローはんだ付けにおいては、上側パッケージ部品と下側パッケージ部品の内部温度が極めて重要な役割を果たすため、上側パッケージ部品の表面温度は過度に高くしてはならない一方で、下側パッケージ部品に属するはんだおよびはんだペーストは、高品質なはんだ付け部を得るために完全に溶融させる必要がある。多段積層実装の場合、熱衝撃や炉内でのずれなどの欠陥の発生を防ぐため、温度上昇速度は1.5°C/s以内に制御することが推奨される。はんだ付け品質を確保することを前提として、熱変形の可能性を最大限低減するために、リフローはんだ付け温度はできるだけ低く抑えるべきである。

また、PoP の包装材としてプラスチックが使用されているため、ポップコーン現象を防ぐには PoP の湿度を厳密に管理する必要があることも、改めて注意しておく価値があります。

ステップ5:PoPの光学およびX線検査

PoP実装およびはんだ付けの工程では、オープンはんだ、コールドはんだ、ブリッジ、コア侵入、はんだペースト不足、はんだペースト過多、はんだボイド、はんだ欠損、パッド浮き、ピロー不良、異物、はんだボール、フラックス過多、パッケージ反り、パッケージ破損、ソルダーレジスト損傷、ソルダーレジストずれなど、多くの種類の欠陥が発生する可能性がある。これらの欠陥を防ぐために、検査方法としては、AOI、内視鏡検査、X線検査、斜入射X線検査および3D X線検査。以下の表は、各手法の特性に基づく検査能力を示しています。

|

検査方法

|

光学検査

|

X線検査

|

|

AOI

|

内視鏡検査

|

2D

|

2D+斜視図

|

3D

|

| オープンはんだ付け |

部分的に |

部分的に |

X |

√ |

√ |

| コールドはんだ付け |

部分的に |

部分的に |

X |

√ |

√ |

| 橋渡し |

部分的に |

部分的に |

√ |

√ |

√ |

| コアの侵入 |

部分的に |

部分的に |

X |

√ |

√ |

| はんだペースト不足 |

X |

部分的に |

X |

√ |

√ |

| はんだペーストの過剰 |

X |

X |

X |

√ |

√ |

| はんだキャビティ |

X |

X |

√ |

√ |

√ |

| はんだ損失 |

部分的に |

部分的に |

√ |

√ |

√ |

| はんだ剥がれ |

部分的に |

部分的に |

X |

√ |

√ |

| パッドの剥がれ |

X |

部分的に |

X |

√ |

√ |

| ピローディフェクト |

部分的に |

部分的に |

X |

√ |

√ |

| 破片 |

部分的に |

部分的に |

部分的に |

部分的に |

部分的に |

| スズの球 |

部分的に |

部分的に |

√ |

√ |

√ |

| 過剰フラックス |

部分的に |

部分的に |

X |

X |

X |

| パッケージ反り |

√ |

√ |

X |

√ |

√ |

| 破損したパッケージ |

部分的に |

部分的に |

X |

部分的に |

部分的に |

| ソルダーマスクの損傷 |

X |

X |

√ |

√ |

√ |

| ソルダーマスクのずれ |

X |

X |

√ |

√ |

√ |

内視鏡検査は、オープンはんだ付け、コア侵入、不十分なはんだペースト、パッドの剥離、異物(非金属)など、2D X線では検査できない欠陥の確認に適用することができます。主な欠点は、BGA内部のはんだを検査できない点にあります。しかし、X線検査よりもコストが低く、はんだ付け中の画像や動画を取得できる多機能検査ツールとして利用することができます。

2D X線検査では、ブリッジング、ボイド(はんだ空洞)、はんだ不足、はんだボール、ソルダーレジスト損傷、位置ずれなどの欠陥を検査することができます。しかし一方で、条件によってはオープンはんだ、不完全はんだ(コールドジョイント)、はんだペースト不足などの欠陥を検出できない場合があります。これらの検査は、高精度かつ優れた性能を持つ斜め観察高倍率検査(OVHM)を適用して初めて可能になります。2D X線検査装置の分解能は8~10μmであり、一部の先進的なシステムでは1μm未満の分解能を実現できます。

3D X線検査は、内視鏡検査と2D X線検査の機能を統合しており、はんだ接合部および内部金属組織構造の検査が可能である。その主な欠点は、コストが高く、検査速度が遅く、機能が冗長である点である。したがって、非常に複雑な技術や製品に対して最も効果的に機能する。

2D X線と斜視検査の適用により、次のような機能を実現することができます。

・PoP組立およびはんだ付け不良検査

・PoPスタッキング状況の確認

・反り検査